邊沿觸發器,指的是接收時鐘脈衝CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數據。在CP=1及CP=0 期間以及CP非約定跳變到來時,觸發器不接收數據的觸發器。

基本介紹

- 中文名:邊沿觸發器

- 學科:數字電路設計

簡介

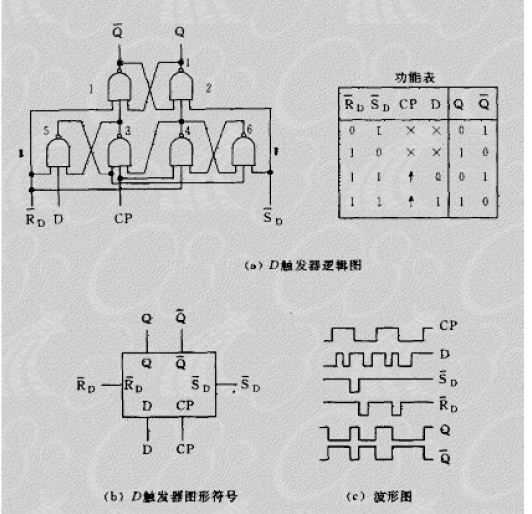

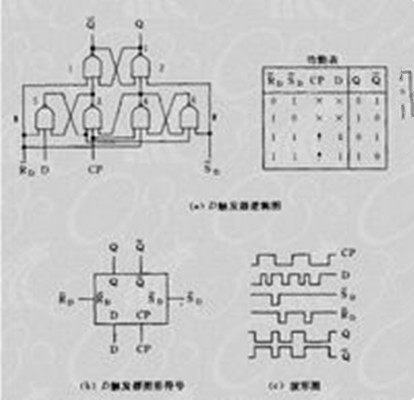

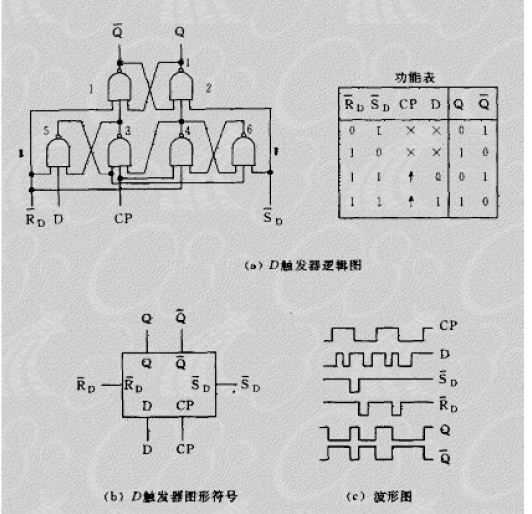

圖1.邏輯圖及典型波形圖

圖1.邏輯圖及典型波形圖邊沿D觸發器

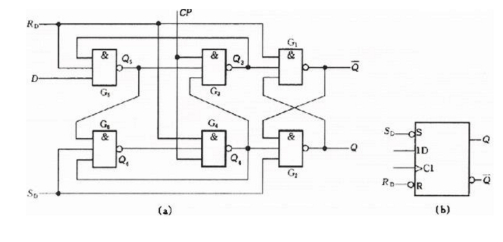

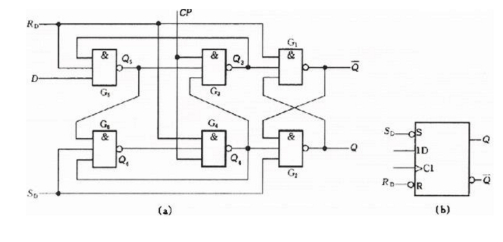

圖2 邊沿D 觸發器的邏輯圖和邏輯符號

圖2 邊沿D 觸發器的邏輯圖和邏輯符號

邊沿觸發器,指的是接收時鐘脈衝CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數據。在CP=1及CP=0 期間以及CP非約定跳變到來時,觸發器不接收數據的觸發器。

圖1.邏輯圖及典型波形圖

圖1.邏輯圖及典型波形圖 圖2 邊沿D 觸發器的邏輯圖和邏輯符號

圖2 邊沿D 觸發器的邏輯圖和邏輯符號邊沿觸發器,指的是接收時鐘脈衝CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數據。在CP=1及CP=0 期間以及CP非約定跳變到來時,觸發器不接收數據的觸發器...

D觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中...

在電子電路中,有許多觸發器採用下降沿觸發方式,例如主從RS觸發器(如下圖)、下降沿JK邊沿觸發器等(詳見JK觸發器)[2] 。主從RS觸發器 ...

當觸發器的同步控制信號E為約定“1”或“0”電平時,觸發器接收輸入數據,此時輸入數據D 的任何變化都會在輸出Q 端得到反映;當E 為非約定電平時,觸發器狀態保持...

與常規RS觸發器相比,同步RS觸發器多出一個端子,稱為時鐘信號輸入端支結構可以使同步RS觸發器根據時鐘脈衝時序改變輸出狀態。當輸入端(S、R)狀態發生變化.同時只有...

觸發器邏輯功能 編輯 電路結構,是指電路中門電路的種類及組合方式。基本RS觸發器、同步RS觸發器、主從觸發器、邊緣觸發器等是指電路結構的不同形式。由於電路結構...

施密特觸發器有兩個穩定狀態,但與一般觸發器不同的是,施密特觸發器採用電位觸發方式,其狀態由輸入信號電位維持;對於負向遞減和正向遞增兩種不同變化方向的輸入信號,...

觸發器暫存器是邊沿敏感的存儲單元,數據存儲的動作有某一信號的上升或者下降沿進行同步的,觸發器的Q輸出端在每一個時鐘沿都會被更新,而所存器只能在使能電平有效...

時鐘觸發器,指的是凡是有時鐘信號控制的觸發器。...... 時鐘觸發器又可分為同步觸發器、主從觸發器、邊沿觸發器。時鐘觸發器按邏輯功能分為5種:時鐘jk觸發器、rs...

斯密特觸發器又稱斯密特非門,是具有滯後特性的數字傳輸門。該器件既可以像普通“與非”門那樣工作,也可以接成斯密特觸發器來使用。...

時鐘信號通常被用於同步電路當中,扮演計時器的角色,並組成電路的電子組件。時鐘邊沿觸發信號意味著所有的狀態變化都發生在時鐘邊沿到來時刻。只有當同步信號到達時,...

在數字電路中,移位暫存器(英語:shift register)是一種在若干相同時間脈衝下工作的以觸發器為基礎的器件,數據以並行或串列的方式輸入到該器件中,然後每個時間脈衝依次...

空翻現象,又稱為競態現象,是數字電路中的一個術語,指在同一個時鐘脈衝信號作用區間內,由於時鐘脈衝的寬度過大,觸發器出現在“0”“1”兩邏輯信號中多次翻轉的...

在數字電路中,移位暫存器是一種在若干相同時間脈衝下工作的以觸發器為基礎的器件,數據以並行或串列的方式輸入到該器件中,然後每個時間脈衝依次向左或右移動一個比特...

CC4027屬於CMOS邊沿JK觸發器。雙列16腳封裝,雙上升沿J-K觸發器,金屬-氧化物-半導體型互補MOS,電源電壓=3~18V。...

10.2.1主從RS觸發器 10.2.2主從JK觸發器 10.2.3主從T觸發器和T′觸發器 10.2.4主從JK觸發器存在的問題——一次變化現象 10.3邊沿觸發器 10.3...

5.3 同步觸發器(鐘控觸發器) 1515.3.1 同步RS觸發器 1525.3.2 同步JK觸發器 1545.4 邊沿觸發器 1565.4.1 下降沿JK觸發器 157...