專利背景

深度學習技術是

人工智慧的核心,對很多套用都起到了非常大的推動作用。深度學習算法是典型計算密集型算法,作為該算法核心部分的矩陣乘法,是一種計算和數據密集型的運算。在需要較高計算效率的場景,矩陣算法通常需要使用基於FPGA或者ASIC的專用處理器來執行,專用處理器可以提供大量定製化的計算和存儲資源。如果專用處理器中用於執行矩陣乘法算法的部分能採用合理的計算單元和存儲結構,將會大大降低電路資源消耗,降低設計複雜度,提高晶片的性價比和能耗比。

2016年10月之前的專用

處理器中執行矩陣乘法算法的硬體架構,在對M×N的矩陣與N×K的矩陣相乘時,通常在M和K兩個維度進行並行度的挖掘。然而,由於深度學習算法中涉及的矩陣乘運算常常出現被乘數矩陣的行數較少甚至被乘數矩陣為單行矩陣的情形,在M維度挖掘並行度容易導致架構通用性較差;若僅從K維度挖掘,並行度受限於套用中K的規模,計算性能有限,導致利用率低。

發明內容

專利目的

《處理器和用於在處理器上執行矩陣乘運算的方法》的目的在於提出一種改進的處理器和用於在處理器上執行矩陣乘運算的方法,來解決以上背景技術部分提到的技術問題。

技術方案

第一方面,《處理器和用於在處理器上執行矩陣乘運算的方法》提供了一種處理器方法,所述處理器包括數據匯流排以及由k個處理單元組成的陣列處理機,其中:所述數據匯流排,用於依次從M×N的被乘數矩陣中讀取n列的行向量並輸入至所述陣列處理機中的每個處理單元、從N×K的乘數矩陣中讀取n×k的子矩陣並將所述子矩陣的每個列向量輸入至所述陣列處理機中對應的處理單元以及將每個處理單元執行乘運算所得到的結果輸出;所述陣列處理機中的每個處理單元,用於並行對輸入的行向量以及列向量執行向量乘運算,每個處理單元包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器;其中,n、k、M、N均為大於1的整數。

在一些實施例中,所述處理器還包括:第一片上存儲單元、第二片上存儲單元以及第三片上存儲單元;以及所述數據匯流排進一步用於:將所述被乘數矩陣以及所述乘數矩陣分別快取至所述第一片上存儲單元和所述第二片上存儲單元;依次從所述第一片上存儲單元以及所述第二片上存儲單元分別讀取對應的行向量和列向量到每個處理單元中;將每個處理單元執行乘加運算所得到的結果輸出至所述第三片上存儲單元;對所述第三片上存儲單元的數據進行快取。

在一些實施例中,所述數據匯流排的快取操作以及所述陣列處理機中處理單元的運算操作以桌球操作方式並行執行。

在一些實施例中,所述第一片上存儲單元以行為單位進行數據存儲,所述第二片上存儲單元以列為單位進行數據存儲。

在一些實施例中,所述第三片上存儲單元以行為單位進行數據存儲。

第二方面,該申請提供了一種用於在處理器上執行矩陣乘運算的方法,所述處理器包括k個處理單元組成的陣列處理機,所述方法包括:將M×N的被乘數矩陣中n列的行向量讀取到所述陣列處理機中的每個處理單元上,每個處理單元包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器;將N×K的乘數矩陣中n×k的子矩陣中每個n行的列向量分別讀取到所述陣列處理機中對應的處理單元上;使用各個處理單元並行對每個列向量與所述行向量執行向量乘運算,其中,每個處理單元中的華萊士樹乘法器用於並行執行乘向量運算中的乘運算和加運算;將每個處理單元執行乘運算所得到的結果輸出;其中,n、k、M、N均為大於1的整數。

在一些實施例中,所述處理器還包括第一片上存儲單元、第二片上存儲單元、第三片上存儲單元;以及所述將M×N的被乘數矩陣中n列的行向量讀取到每個處理單元上,包括:將所述被乘數矩陣快取至第一片上存儲單元;依次從第一片上存儲單元讀取行向量到所述陣列處理機的每個處理單元中;以及所述將N×K的乘數矩陣中n×k的子矩陣中每個n行的列向量分別讀取到對應的處理單元上,包括:將所述乘數矩陣快取至第二片上存儲單元;依次從第二片上存儲單元讀取對應的子矩陣以將子矩陣中的各個列向量分別輸出到所述陣列處理機中對應的處理單元上;以及所述將每個處理單元執行乘運算所得到的結果輸出,包括:將每個處理單元執行乘加運算所得到的結果輸出至第三片上存儲單元;對所述第三片上存儲單元的數據進行快取。

在一些實施例中,以桌球操作方式並行執行運算操作以及數據快取操作。

在一些實施例中,所述方法還包括:以行為單位存儲所述第一片上存儲單元上的數據;以列為單位存儲所述第二片上存儲單元上的數據。

在一些實施例中,所述方法還包括:以行為單位存儲所述第三片上存儲單元上的數據。

改善效果

《處理器和用於在處理器上執行矩陣乘運算的方法》在對矩陣進行乘運算時,不對M維度進行並行度挖掘,使得處理器在處理涉及較多的向量與矩陣的乘運算的深度學習算法時,保證架構較高的通用性;此外,陣列處理機的多個PE以及PE內部的華萊士樹乘法器分別可以在矩陣的K維度和N維度進行並行度挖掘,進一步提高了整體的並行度,從而加快了對矩陣乘運算的處理速度。

附圖說明

圖1是《處理器和用於在處理器上執行矩陣乘運算的方法》可以套用於其中的示例性系統架構圖;

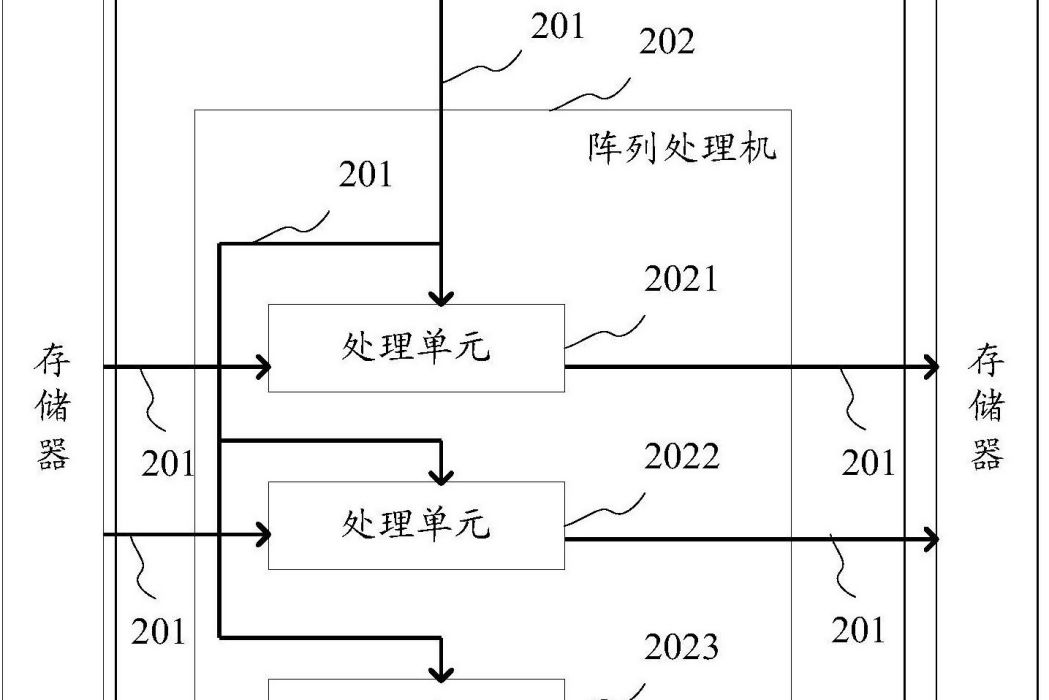

圖2是根據該申請的處理器的一個實施例的結構示意圖;

圖3是根據圖2對應實施例中陣列處理機的處理單元的結構示意圖;

圖4是根據該申請的處理器的又一個實施例的結構示意圖;

圖5是根據該申請的用於在處理器上執行矩陣乘運算的方法的一個實施例的流程圖。

圖6是循環執行圖5實施例中所示方法的一種示意圖。

技術領域

《處理器和用於在處理器上執行矩陣乘運算的方法》涉及計算機技術領域,具體涉及計算機硬體技術領域,尤其涉及處理器和用於在處理器上執行矩陣乘運算的方法。

權利要求

1.一種處理器,其特徵在於,所述處理器包括數據匯流排以及由k個處理單元組成的陣列處理機,其中:所述數據匯流排,用於依次從M×N的被乘數矩陣中讀取n列的行向量並輸入至所述陣列處理機中的每個處理單元、從N×K的乘數矩陣中讀取n×k的子矩陣並將所述子矩陣的每個列向量輸入至所述陣列處理機中對應的處理單元以及將每個處理單元執行乘運算所得到的結果輸出;所述陣列處理機中的每個處理單元,用於並行對輸入的行向量以及列向量執行向量乘運算,每個處理單元包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器;其中,n、k、M、N均為大於1的整數。

2.根據權利要求1所述的處理器,其特徵在於,所述處理器還包括:第一片上存儲單元、第二片上存儲單元以及第三片上存儲單元;以及所述數據匯流排進一步用於:將所述被乘數矩陣以及所述乘數矩陣分別快取至所述第一片上存儲單元和所述第二片上存儲單元;依次從所述第一片上存儲單元以及所述第二片上存儲單元分別讀取對應的行向量和列向量到每個處理單元中;將每個處理單元執行乘加運算所得到的結果輸出至所述第三片上存儲單元;對所述第三片上存儲單元的數據進行快取。

3.根據權利要求2所述的處理器,其特徵在於,所述數據匯流排的快取操作以及所述陣列處理機中處理單元的運算操作以桌球操作方式並行執行。

4.根據權利要求2或3所述的處理器,其特徵在於,所述第一片上存儲單元以行為單位進行數據存儲,所述第二片上存儲單元以列為單位進行數據存儲。

5.根據權利要求4所述的處理器,其特徵在於,所述第三片上存儲單元以行為單位進行數據存儲。

6.一種用於在處理器上執行矩陣乘運算的方法,其特徵在於,所述處理器包括k個處理單元組成的陣列處理機,所述方法包括:將M×N的被乘數矩陣中n列的行向量讀取到所述陣列處理機中的每個處理單元上,每個處理單元包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器;將N×K的乘數矩陣中n×k的子矩陣中每個n行的列向量分別讀取到所述陣列處理機中對應的處理單元上;使用各個處理單元並行對每個列向量與所述行向量執行向量乘運算,其中,每個處理單元中的華萊士樹乘法器用於並行執行乘向量運算中的乘運算和加運算;將每個處理單元執行乘運算所得到的結果輸出;其中,n、k、M、N均為大於1的整數。

7.根據權利要求6所述的方法,其特徵在於,所述處理器還包括第一片上存儲單元、第二片上存儲單元、第三片上存儲單元;以及所述將M×N的被乘數矩陣中n列的行向量讀取到每個處理單元上,包括:將所述被乘數矩陣快取至第一片上存儲單元;依次從第一片上存儲單元讀取行向量到所述陣列處理機的每個處理單元中;以及所述將N×K的乘數矩陣中n×k的子矩陣中每個n行的列向量分別讀取到對應的處理單元上,包括:將所述乘數矩陣快取至第二片上存儲單元;依次從第二片上存儲單元讀取對應的子矩陣以將子矩陣中的各個列向量分別輸出到所述陣列處理機中對應的處理單元上;以及所述將每個處理單元執行乘運算所得到的結果輸出,包括:將每個處理單元執行乘加運算所得到的結果輸出至第三片上存儲單元;對所述第三片上存儲單元的數據進行快取。

8.根據權利要求7所述的方法,其特徵在於,以桌球操作方式並行執行運算操作以及數據快取操作。

9.根據權利要求7或8所述的方法,其特徵在於,所述方法還包括:以行為單位存儲所述第一片上存儲單元上的數據;以列為單位存儲所述第二片上存儲單元上的數據。

10.根據權利要求9所述的方法,其特徵在於,所述方法還包括:以行為單位存儲所述第三片上存儲單元上的數據。

實施方式

圖1示出了可以套用《處理器和用於在處理器上執行矩陣乘運算的方法》的實施例的示例性系統架構100。

如圖1所示,系統架構100可以包括通用處理器101和專用伺服器102。

通用處理器101用於將外部指令(例如矩陣運算)以及待處理的數據(例如矩陣)傳送給專用處理器102,專用處理器102可以根據外部指令生成控制信號,以通過控制信號來控制內部的器件執行數據處理操作(例如矩陣運算),最後處理生成的結果可以再傳送回通用處理器101。其中,通用處理器101也可以稱為主機,而專用處理器102可以是由FPGA(Field-Programmable Gate Array,即現場可程式門陣列伺服器)設計而成。

需要說明的是,該申請實施例所提供的處理器一般是指圖1中的專用處理器102,相應地,用於在處理器上執行指令的方法一般由專用處理器102執行。

應該理解,圖1中的通用處理器101和專用處理器102的數目僅僅是示意性的。根據實現需要,可以具有任意數目的通用處理器和專用處理器。

繼續參考圖2,示出了根據該申請的處理器的一種結構示意圖200。

如圖2所示,處理器200包括數據匯流排201和陣列處理機202。其中,陣列處理機202包括處理單元(PE,Processing Element)2021、處理單元2022和處理單元2023。需要說明的是,圖中各個部件的數目僅為示意性的,可以具有任意數目的數據匯流排和陣列處理機,陣列處理機202中的PE的數目為k個(k為大於1的整數),而不限於圖中所示的3個。

數據匯流排201可以用於從存儲待執行矩陣乘運算的被乘數矩陣和乘數矩陣的存儲器進行數據讀取,並按照一定的規則將數據輸入到陣列處理機202中相應的處理單元。以M×N(M、N均為大於1的整數)的被乘數矩陣與N×K(K為大於1的整數)的乘數矩陣為例,數據匯流排201可以依次從外部的存儲器203中的被乘數矩陣中依次讀取n列的行向量並輸入至陣列處理機202的每個處理單元;與此同時,數據匯流排201可以依次從外部的存儲器204中的乘數矩陣讀取n×k(n是大於1的整數)的子矩陣,並將n×k的子矩陣中的k個列向量分別輸入至陣列處理機202中k個PE中對應的PE中。從而,每個PE讀取到的數據為相同的n列行向量和不同的n行列向量。此外,數據匯流排201還可以用於將每個PE所處理的計算結果輸出到外部的存儲器205。需要說明的是,存儲器203、存儲器204、存儲器205可以是相同的設備,也可以是不同的設備。

陣列處理機202中的k個PE,可以同時根據輸入至每個PE的n列的行向量和n行的列向量進行向量乘運算。從而,陣列處理機202中的k個PE可以並行處理k個向量乘運算。

陣列處理機202中的每個PE可以包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器。在該華萊士樹乘法器中,n個乘法器並聯設定,n-1個加法器則設定為多個彼此串聯連線的加法器組,加法器組分別包括一個或多個並聯設定的加法器,各個加法器組中加法器的數目依次為n/2,n/4……1。每兩個乘法器進行運算所得到的乘積輸入至第一個加法器組中的各個加法器,各個加法器組中每兩個加法器進行運算所得到的加和輸入至相鄰的後續加法器組中的各個加法器中。從而,在對n列的行向量和n行的列向量執行向量乘運算時可以並行執行對應分量的乘運算。同時,也在對乘運算所得到的乘積進行累加操作時,可以並行執行加運算。

圖3是n為4時每個PE的結構示意圖。如圖3所示,PE所包括的華萊士樹乘法器由三個部分串聯而成,分別是4個並聯設定的乘法器301、302、303、304,2個並聯設定的加法器305、306以及一個單獨設定的加法器307。其中,4個並聯設定的乘法器301、302、303、304可以用於對4列的行向量和4行的列向量中4組對應的分量進行乘運算。乘法器301、302的結果輸入至加法器305,乘法器303、304的結果輸入至加法器306。加法器305、加法器306用於並行執行對應的加法運算。加法器305、加法器306的運算結果均輸入加法器307,加法器307進行加運算後將結果輸出。在該華萊士樹乘法器中,4個並聯設定的乘法器301、302、303、304可以實現在N維度上挖掘並行度,加法器305、加法器306也能提高運算並行性。

《處理器和用於在處理器上執行矩陣乘運算的方法》的上述實施例提供的處理器,在對矩陣進行乘運算時,不對M維度進行並行度挖掘,使得處理器在處理涉及較多的向量與矩陣的乘運算的深度學習算法時,保證架構較高的通用性;此外,陣列處理機的多個PE以及PE內部的華萊士樹乘法器分別可以在矩陣的K維度和N維度進行並行度挖掘,進一步提高了整體的並行度,從而加快了對矩陣乘運算的處理速度。

繼續參考圖4,圖4示出了根據該申請的處理器的又一種結構示意圖400。

如圖4所示。其中,處理器400可以包括:數據匯流排201、陣列處理機402、第一片上存儲單元403、第二片上存儲單元404以及第三片上存儲單元405。

陣列處理機402以及其中的處理單元的結構可以參考圖2對應實施例中的陣列處理機202,這裡不再贅述。上述數據匯流排401用於執行以下功能:將被乘數矩陣以及乘數矩陣分別從外部的存儲器406和存儲器407快取至第一片上存儲單元403和第二片上存儲單元404;依次從第一片上存儲單元403以及第二片上存儲單元404分別讀取對應的行向量和列向量到每個處理單元中;將每個處理單元執行乘加運算所得到的結果輸出至第三片上存儲單元405;將第三片上存儲單元的數據快取至外部的存儲器408。

可選的,第一片上存儲單元403、第二片上存儲單元404以及第三片上存儲單元405可以採用靜態隨機存取存儲器,這種存儲器不需要刷新電路即能保存它內部存儲的數據,具有較高的性能與更小的功耗。

可選的,第二片上存儲單元404可以包括k個子存儲單元,每個子存儲單元n×k的子矩陣中k個列向量,從而使得數據匯流排401可以分別從各個子存儲單元讀取數據到陣列處理機402中對應的PE上。同樣,與第三片上存儲單元405也可以包括k個子存儲單元,使得數據匯流排401可以將陣列處理機402中每個PE得到的運算結果寫入第三片上存儲單元405中對應的子存儲單元。

在該實施例的一些可選實現方式中,數據匯流排401的快取操作以及陣列處理機402中處理單元的運算操作以桌球操作方式並行執行。在該實現方式中,數據快取操作以及運算操作可以並行執行,從而使得從片外讀取數據的時間以及將數據快取至片外的時間可以被運算所占用的時間覆蓋,從而進一步減少矩陣乘運算的時間。

在該實施例的一些可選實現方式中,第一片上存儲單元403可以以行為單位進行數據存儲,第二片上存儲單元404可以以列為單位進行數據存儲。由於第一片上存儲單元403可以以行為單位進行數據存儲,第二片上存儲單元404可以以列為單位進行數據存儲,在數據匯流排401從第一片上存儲單元403讀取行向量以及從第二片上存儲單元404讀取列向量到陣列處理機402中的PE中時,可以直接從第一片上存儲單元403中一行的數據中讀取需要的行向量以及從第二片上存儲單元404中一列的數據中讀取需要的列向量,從而提高讀取效率。

在該實施例的一些可選實現方式中,第三片上存儲單元405可以以行為單位進行數據存儲。在深度學習算法中,上一個矩陣乘運算的結果常常用於下一次矩陣乘運算的被乘數矩陣,因此在第三片上存儲單元405在以行為單位進行數據存儲時,第一片上存儲單元403可以直接從第三片上存儲單元405讀取數據,在不作處理情況下即可用作下一次矩陣乘運算。

《處理器和用於在處理器上執行矩陣乘運算的方法》的上述實施例提供的處理器,相對於圖2對應實施例中所提供的處理器,額外設定了用於對被乘數矩陣和乘數矩陣進行讀快取的片上存儲單元以及用於對運算結果進行寫快取的片上存儲單元,從而可以使得避免每次使用陣列處理機202進行矩陣乘運算的片段時都要等待從片外讀取數據以及向片外寫出數據的時間,消除大量的數據復用情況下對片外頻寬的需求,有助於提高整體的處理效率。

繼續參考圖5,示出了根據該申請的用於在處理器上執行矩陣乘運算的方法的一個實施例的流程500。處理器包括k個處理單元組成的陣列處理機,用於在處理器上執行指令的方法,包括以下步驟:

步驟501,將M×N的被乘數矩陣中n列的行向量讀取到陣列處理機中的每個處理單元上。

在該實施例中,處理器(例如圖1中的專用處理器102)首先從M×N的被乘數矩陣中讀取數據。其中,被乘數矩陣可以是存儲在片外的存儲單元(例如通用處理器CPU中的存儲器)中,處理器從該存儲單元即可讀取到相應的數據。需要說明的是,被乘數矩陣也可以存儲在其他存儲單元中。在讀取過程中,處理器每次讀取被乘數矩陣中n列的行向量。由於被乘數矩陣有N列,因此對被乘數矩陣的一行數據遍歷一次,需要讀取次數為N/n。每次讀取到的行向量,可以輸入至陣列處理機的每個PE中,即k個PE分享同一個行向量。

步驟502,將N×K的乘數矩陣中n×k的子矩陣中每個n行的列向量分別讀取到陣列處理機中對應的處理單元上。

在該實施例中,對應於步驟501中讀取並輸入至每個處理單元的行向量,處理器可以從N×K的乘數矩陣中每次讀取n×k的子矩陣。對於每次讀取到的n×k的子矩陣,處理器可以將k個列向量分別輸入至陣列處理機的k個PE中,每個列向量對應一個PE,從而可以保證後續過程中k個PE可以同時處理k個向量乘運算,實現在K維度上的並行處理。

步驟503,使用各個處理單元並行對每個列向量與行向量執行向量乘運算。

在該實施例中,基於每次讀取並輸入至陣列處理機中各個處理單元的數據,處理器可以通過陣列處理機的各個處理單元執行行向量與子矩陣的乘操作,其中每個處理單元對行向量與列向量執行向量乘運算。具體的,由於k個處理單元讀取到同樣的行向量,而每個處理單元則讀取到n×k的子矩陣中不同的列向量,因此k個處理單元可以實現k個列向量與同一個行向量的並行運算。

進一步的,由於每個處理單元包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器,對於每個處理單元,可以使用n個乘法器同時執行n列的行向量與n行的列向量進行相乘時涉及的n個分量乘運算,每次可以並行處理n個數字乘運算,同時,使用華萊士樹乘法器中設定的加法器還可以對向量乘運算中涉及的數字加操作進行並行操作,從而實現在乘數矩陣N維度上並行度的挖掘,進一步提高處理的並行性,進而提高整體的處理效率。

步驟504,將每個處理單元執行乘運算所得到的結果輸出。

基於步驟503中每個處理單元執行的向量乘運算,處理器可以通過每個處理單元將乘運算所得到的結果輸出。由於步驟501中每次讀取陣列處理機的數據僅為被乘數矩陣長度為N的一行數據中長度為n的向量,而步驟202中每次讀取的也僅為N×K的乘數矩陣中n×k的子矩陣,可見上述方案中的各個步驟通常需要循環執行多次才能完成整個矩陣乘運算。

在該實施例的一些可選實現方式中,處理器可以按照圖6所示方式循環執行步驟501和步驟502,以完成完整的矩陣乘運算。如圖6所示,所執行的是被乘數矩陣為A(M×N)和乘數矩陣B(N×K)之間的矩陣乘運算。循環可以包括最內層循環、次內層循環以及最外層循環。

在最內層的循環中,可以使用步驟501對被乘數矩陣中單行N列的數據進行遍歷,即沿著被乘數矩陣N維度的方向每次讀取n列的行向量。對應的,在最內層的循環中可以使用步驟502對乘數矩陣N行k列的數據進行遍歷,即沿著乘數矩陣N維度的方向每次讀取n行k列的子矩陣。每完成一輪內循環,即可對被乘數矩陣中一行的數據和乘數矩陣中一個N行k列的數據的乘操作。可見,每次內循環每執行N/n次,即可觸發後續的次外層循環執行一次。

在次內層循環中,可以在每完成一次最內層循環時使用步驟502對被乘數矩陣中K方向上的下一個N行k列的數據進行遍歷,而步驟502則可以重新對單行N列的數據進行遍歷。每完成一輪的次內層循環,即可完成被乘數矩陣的一行數據與整個乘數矩陣的乘操作。可見,次外層循環每執行K/k次,即可觸發後續的最外層循環執行一次。

在最外層循環中,當乘數矩陣中的數據均遍歷後,可以使用步驟501對被乘數矩陣中M維度的方向中下一個單行N列的數據進行遍歷,直到處理完被乘數矩陣的M行。可見,最外層循環每執行M次,即可完成一次完整的矩陣乘運算。

在該實施例的一些可選實現方式中,上述處理器還包括第一片上存儲單元、第二片上存儲單元、第三片上存儲單元。同時,步驟501包括:將被乘數矩陣快取至第一片上存儲單元;依次從第一片上存儲單元讀取行向量到陣列處理機的每個處理單元中。步驟502可以包括:將乘數矩陣快取至第二片上存儲單元;依次從第二片上存儲單元讀取對應的子矩陣以將子矩陣中的各個列向量分別輸出到陣列處理機中對應的處理單元上。步驟504則可以包括:將每個處理單元執行乘運算所得到的結果輸出,包括:將每個處理單元執行乘加運算所得到的結果輸出至第三片上存儲單元;對第三片上存儲單元的數據進行快取。該實現方式的具體處理可以參考圖4對應實施例中相應的描述,這裡不再贅述。

在該實施例的一些可選實現方式中,步驟501、步驟502、步驟503以及步驟504所涉及的運算操作以及數據快取操作可以並行執行。其中,步驟503中涉及的為運算操作,步驟501、步驟502以及步驟504中涉及的為數據快取操作。該實現方式的具體處理可以參考圖4對應實施例中相應的實現方式,這裡不再贅述。

在該實施例的一些可選實現方式中,上述方法還包括:以行為單位存儲第一片上存儲單元上的數據;以列為單位存儲第二片上存儲單元上的數據。該實現方式的具體處理可以參考圖4對應實施例中相應的實現方式,這裡不再贅述。

在該實施例的一些可選實現方式中,上述方法還包括:以行為單位存儲第三片上存儲單元上的數據。該實現方式的具體處理可以參考圖4對應實施例中相應的實現方式,這裡不再贅述。

《處理器和用於在處理器上執行矩陣乘運算的方法》的上述實施例提供的方法,在對矩陣進行乘運算時,不對M維度進行並行度挖掘,使得在使用處理器處理涉及較多的向量與矩陣的乘運算的深度學習算法時,保證架構較高的通用性;此外,陣列處理機的多個PE以及PE內部的華萊士樹乘法器分別可以在矩陣的K維度和N維度進行並行度挖掘,進一步提高了整體的並行度,從而加快了對矩陣乘運算的處理速度。

作為另一方面,該申請還提供了一種非易失性計算機存儲介質,該非易失性計算機存儲介質可以是上述實施例中所述裝置中所包含的非易失性計算機存儲介質;也可以是單獨存在,未裝配入終端中的非易失性計算機存儲介質。上述非易失性計算機存儲介質存儲有一個或者多個程式,該一個或者多個程式可以被包括k個處理單元組成的陣列處理機的處理器執行,當所述一個或者多個程式被一個處理器執行時,使得所述處理器:將M×N的被乘數矩陣中n列的行向量讀取到所述陣列處理機中的每個處理單元上,每個處理單元包括由n個乘法器和n-1個加法器組成的華萊士樹乘法器;將N×K的乘數矩陣中n×k的子矩陣中每個n行的列向量分別讀取到所述陣列處理機中對應的處理單元上;使用各個處理單元並行對每個列向量與所述行向量執行向量乘運算,其中,每個處理單元中的華萊士樹乘法器用於並行執行乘向量運算中的乘運算和加運算;將每個處理單元執行乘運算所得到的結果輸出。其中,n、k、M、N均為大於1的整數。

2020年7月14日,《處理器和用於在處理器上執行矩陣乘運算的方法》獲得

第二十一屆中國專利獎優秀獎。