立體積體電路即三維積體電路。20世紀60年代產生的積體電路是用平面工藝製作的,器件的工作區和引線按平面布置,所以稱為二維積體電路。

基本介紹

- 中文名:立體積體電路

- 別名:三維積體電路

- 產生:20世紀60年代

- 目的:提高集成密度和減少外引線

發展,特點,

發展

為了提高集成密度和減少外引線,80年代初出現了由多層疊積而成的三維電路結構,其電路各層之間均用絕緣層隔離,並通過穿孔互連,已達幾十層之多,它分為疊層高密度結構和疊層多功能結構兩種類型。

特點

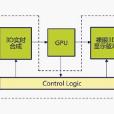

由於將不同功能的器件和電路縱向立體地集成起來,從而得到新的功能部件,所以具有高密度、高速度、多功能和低功耗等特點,可作成大容量存儲器和高速信號處理器。製作三維積體電路的關鍵是SOI(矽/絕緣層結構)技術。隨著分子束外延、化學氣相澱積和原子搬移等超微加工技術的發展,在半導體晶片內部實現器件布局的立體化也將逐步實現,以製作出密度更高的立體積體電路。