分支預測(Branch Prediction):從P5時代開始的一種先進的,解決處理分支指令(if-then-else)導致流水線失敗的數據處理方法,由CPU來判斷程式分支的進行方向,能夠加快運算速度。

基本介紹

- 中文名:分支預測

- 外文名:Branch Prediction

- 作用:解決處理分支指令

- 實用性:近來的處理器已經嘗試採用

指令分支預測一般指本詞條

分支預測(Branch Prediction):從P5時代開始的一種先進的,解決處理分支指令(if-then-else)導致流水線失敗的數據處理方法,由CPU來判斷程式分支的進行方向,能夠加快運算速度。

分支 分支(branch)是指程式運行時需要改變的節點。分枝有無條件分支和有條件分支,其中無條件分支只需要CPU按指令順序執行,而條件分支則必須根據處理結果再決定程式運行方向是否改變。因此需要"分支預測"技術處理的是條件分枝。分支預測 由於程式中的條件分支是根據程式指令在流水線處理後結果再執行的,所以當CPU等待...

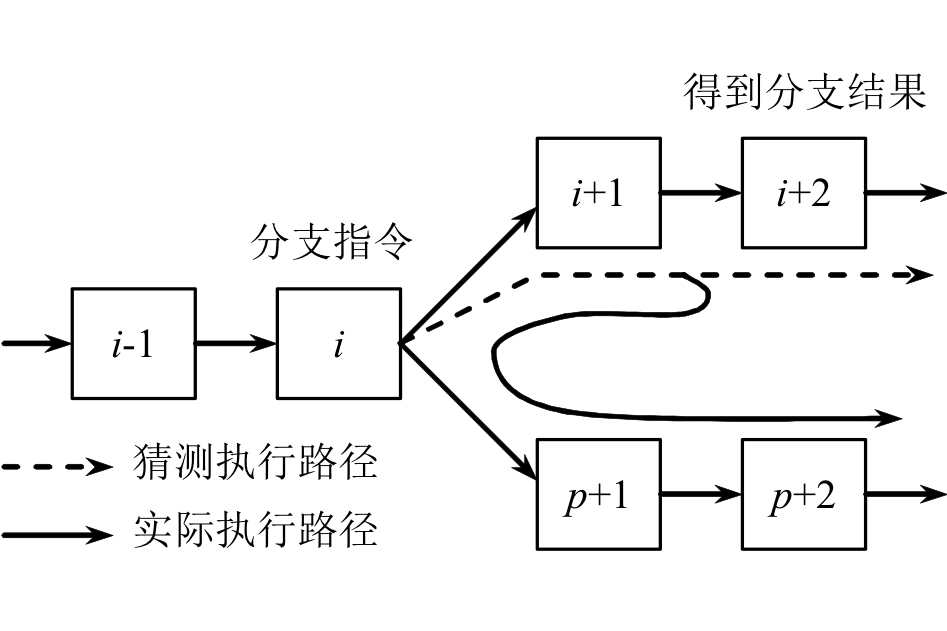

在計算機體系結構中,分支預測器(英語:Branch predictor)是一種數字電路,在分支指令執行結束之前猜測哪一路分支將會被運行,以提高處理器的指令流水線的性能。使用分支預測器的目的,在於改善指令管線化的流程。現代使用指令管線化處理器的性能能夠提高,分支預測器對於現今的指令流水線微處理器獲得高性能是非常關鍵的...

其中,第1章論述計算機系統結構的基本概念以及定量分析基礎;第2章論述計算機指令集的設計、RISC技術及MIPS指令集結構;第3章論述流水線及其性能分析、流水線中的相關和衝突及其解決方法、向量處理機;第4章論述指令級並行性開發,包括指令動態調度、指令分支預測、Tomasulo算法、前瞻執行、超標量、超流水以及超長指令字...

第2章講述計算機指令集的設計、RISC 技術以及 MIPS 指令集結構。第3章講述流水線及其性能分析、流水線中的相關和衝突及其解決方法、向量處理機的結構及其性能評價。第4章講述指令級並行性開發,包括指令動態調度、指令分支預測、超標量技術、超流水技術以及超長指令字技術等。第5章講述 Cache 的基本知識、降低 Cache ...

2.3.2 指令分支預測50 2.3.3 超順序執行技術51 2.3.4 超標量流水線52 2.3.5 超執行緒技術和多處理器技術54 2.4 本章小結55 2.5 習題55 第3章 80X86指令系統和彙編語言58 3.1 定址方式58 3.1.1 8086的定址方式59 3.1.2 80386及後續微處理器與數據有關的定址方式65 3.1.3 80386及後續微...

其實Pentium M 是以 Pentium III的處理器核心為基礎,在經過“(1)改善指令運行結構,(2)使用先進的指令分支預測技術,(3)二級快取容量提高一倍,增至1MB”等等而開發出的處理器。第一代0.13微米製程的PentiumM處理器,也就是指Banias核心,電晶體數量為7700萬顆,晶粒面積則為82.8mm2,最高的核心操作頻率為1....

特別是現代C語言程式,經編譯器最佳化生成的目標代碼中,分支指令所占的比例可達10-20%,對流水線處理器的影響會的更大。為此,現代高性能流水線處理器中一般都加入了分支預測部件,就是在處理器從存儲器預取指令時,當遇到分支(跳轉)指令時,能自動預測跳轉是否會發生,再從預測的方向進行取指,從而提供給流水線...

Nehalem還是基本建立在酷睿微架構(Core Microarchitecture)的骨架上,外加增添了SMT、3層Cache、TLB和分支預測的等級化、IMC、QPI和支持DDR3、新增加SSE4.2指令等技術。比起從Pentium 4的NetBurst架構到酷睿微架構的較大變化來說,從酷睿微架到Nehalem架構的基本核心部分的變化則要小一些,因為Nehalem還是4指令寬度的...

INTEL宣稱,Nehalem的LOCK CMPXCHG指令(其作用是使整個流水線串列化)的延遲是P4的約20%,Core 2的約60%。儘管降低了延遲,但行為仍然和以前的CPU還是一樣的,鎖定指令(Lock)並不是管道化的,即使後面的操作可以被提前到鎖定指令之前來執行。前端部分 (指令拾取和解碼)1、指令拾取(包括分支預測)在Nehalem的...

另外,Core採用改進後的分支預測設計,這使它擁有更優秀的分支預測能力,避免了流水線周期的浪費。這些都使得Conroe處理器的性能比基於前代核心的產品性能提高不少。超強的四組指令編譯器 Core微架構的最大變化之一,就是採用了四組指令編譯器,也就是四組解碼單元。這四組解碼單元由三組簡單解碼單元(Simple Decoder)...

而且標量程式要計算地址,循環變數和分支地址,而這些都是隱含在向量指令里的。執行代碼量的減少帶來了很多有益的結果,首先,指令數量減少使得主存和處理器之間的數據交換量也隨著減少;其次,向量操作中分支指令的執行被隱含起來,這樣也就減少了大部分由於分支預測失誤帶來的延時;再次,僅需一個很簡單的控制單元,在...

SSE2指令集增強了以前那些利用MMX技術和SSE技術的SIMD指令。這些新指令支持128位的SIMD整數操作和128位SIMD雙精度浮點操作。把所給的指令能操作的數據的數量加倍,則只有一半編碼循環里的指令需要被執行。微結構特性 超級管道技術:與P6微結構相比,NetBurst微結構的超級管道技術加倍了管道的深度。分支預測/恢復管道這個...

1997年1月8日:Intel在1996年推出的Pentium 系列的改進版本,內部代號P55C,也就是我們平常所說的Pentium MMX 。Pentium MMX在原Pentium的基礎上進行了重大的改進,增加了片內16KB數據快取和16KB指令快取,4路寫快取以及從Pentium Pro、Cyrix而來的分支預測單元和返回堆疊技術,特別是新增加的57條MMX多媒體指令。產品...

多能奔騰是繼Pentium後英特爾又一個成功的產品,其生命力也相當頑強。多能奔騰在原Pentium的基礎上進行了重大的改進,增加了片內16KB數據快取和16KB指令快取,4路寫快取以及分支預測單元和返回堆疊技術。特別是新增加的57條MMX多媒體指令,使得多能奔騰即使在運行非MMX最佳化的程式時,也比同主頻的Pentium CPU要快得多...

該架構並能提供分支預測與預測運行。它使用硬體暫存器更名結構而不是簡單的暫存器映射。這相同的結構也用於判斷允許並發運行循環。這些能力是可以被編譯器控制的:每個指令字包含許多此動作。這就是該架構的特點之一。此架構提供128個整數暫存器、128個浮點數暫存器、64個單比特預測器與8個分支暫存器。而浮點數暫存器的...

寬區動態執行可以讓每個時鐘周期執行更多指令,以縮短執行時間並改進能效。每個執行核心可同時獲取、分配、執行和返回4條完整指令。這項技術使得處理器的每一個核心可同時處理更多指令,增大了數據流量,無疑提升了數據處理能力。進一步提高效率的特性包括可以進一步提高執行靈活性的更準確的分支預測、更深的指令緩衝區等等...

7.5.1J指令的控制冒險及其硬體解決方法 7.5.2BEQ指令的控制冒險及其硬體處理方法 7.5.3分支預測 7.5.4延時槽技術 7.5.5中斷和異常 7.6總結 7.7拓展閱讀 7.7.1暫存器堆“先寫後讀”實現方式 7.7.2進一步提升流水線的性能 7.7.3其他的指令級並行技術 7.8習題 第8章存儲系統設計 8.1存儲器系統...

SSE2指令集增強了以前那些利用MMX技術和SSE技術的SIMD指令。這些新指令支持128位的SIMD整數操作和128位SIMD雙精度浮點操作。把所給的指令能操作的數據的數量加倍,則只有一半編碼循環里的指令需要被執行。特性 超級管道技術 與P6微結構相比,NetBurst微結構的超級管道技術加倍了管道的深度。分支預測/恢復管道這個關鍵的...