基本概念,微處理機晶片結構,微處理機晶片器的發展,CISC微處理器,RISC微處理器,EPIC微處理器,Alpha處理器,MIPS處理器,微處理器晶片的新發展,追隨CISC還是轉向RISC,PARROT基於RISC思想,分散式計算思想,讓PC同步執行兩套系統,更有效地利用能源,

基本概念

自從1971年Intel公司推出第一片微處理器晶片4004、尤其是1974年推出8位微處理機晶片8080以後,摩爾定律(即積體電路的集成度,性能大約每18個月翻一番)就開始。從90年代初開始,國際上採用主流的微處理機晶片研製高性能並行計算機已成為一種發展趨勢。

微處理機(又稱為CPU或中央處理單元)是裝配在單顆晶片上的一個完整的計算引擎。微處理機能完成取

指令、執行指令,以及與外界

存儲器和邏輯部件交換信息等操作,是

微型計算機的運算控制部分。它可與

存儲器和外圍

電路晶片組成

微型計算機。

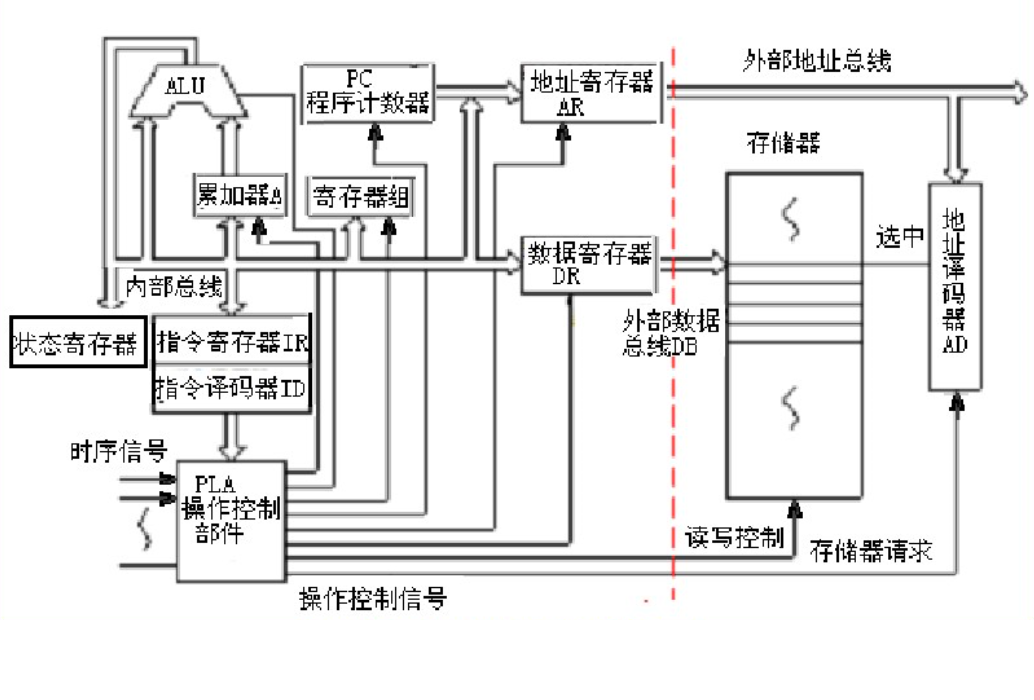

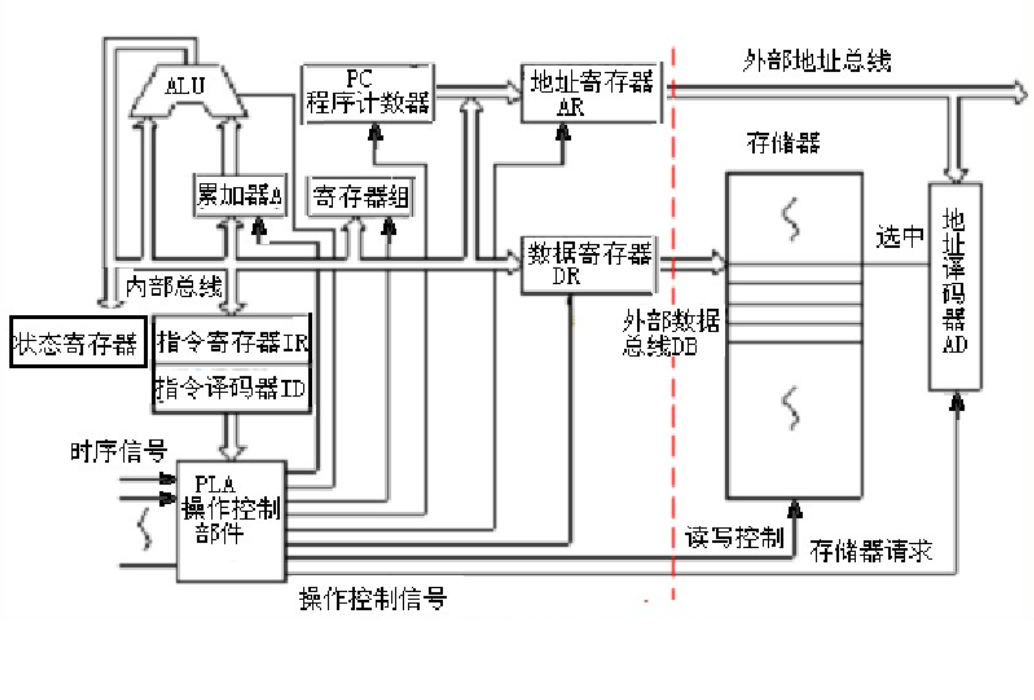

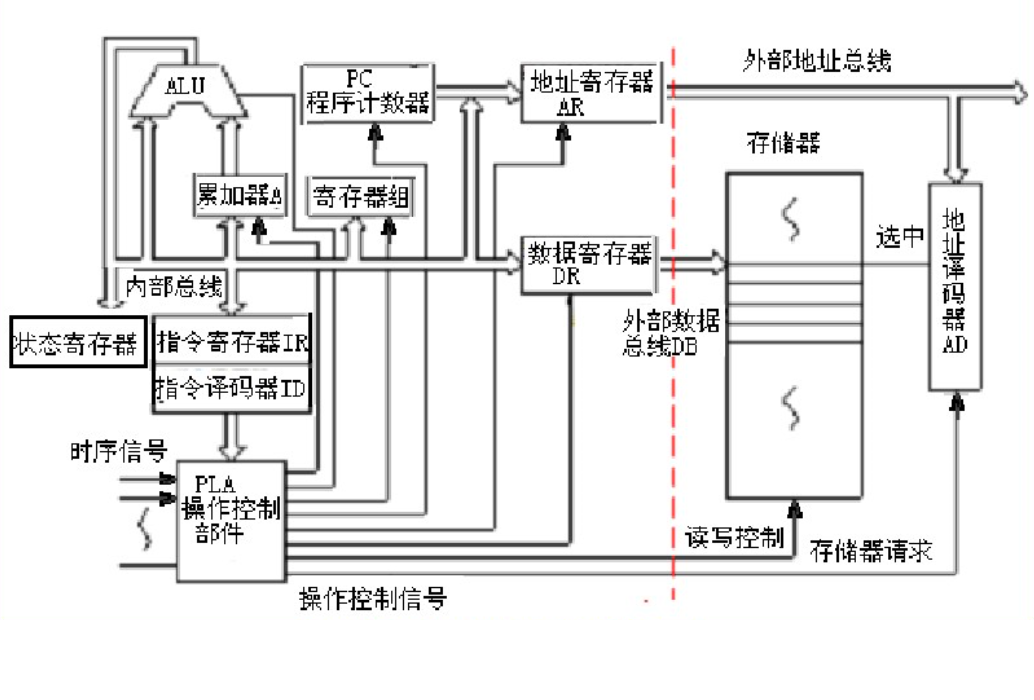

微處理機晶片結構

微處理器基本結構如圖:

這是一個進行了最大程度簡化的微處理器。此微處理器具有:

(1)一條地址匯流排(匯流排寬度可以8位、16位或32位),用於向記憶體傳送一個地址;

(2)一條數據匯流排(匯流排寬度可以是8位、16位或32位),能夠將數據傳送到記憶體或從記憶體取得數據;

(3)一條RD(讀)和WR(寫)線路,告訴記憶體它是希望寫入某個地址位置還是獲得某個地址位置的內容;

(4)一條時鐘線路,將時鐘脈衝序列傳送到處理器;

(5)復位線路,用於將程式計數器重置為零(或者其他內容)並重新開始執行。

微處理器執行一組機器指令,這組指令可向處理器告知應執行哪些操作。微處理器就會根據指令執行三種基本工作:

(1)通過使用ALU(算術/邏輯單元),微處理器可以執行數學計算。例如:加法、減法、乘法和除法。現代的微處理器包含完整的浮點處理器,它可以對很大的浮點數執行非常複雜的浮點運算。

(2)微處理器可以將數據從一個記憶體位置移動到另一個位置。

(3)微處理器可以做出決定,並根據這些決定跳轉到一組新指令。

微處理器能夠執行許多非常複雜的工作,但是所有工作都屬於這三種基本操作的範疇。

微處理機晶片器的發展

CISC微處理器

這種計算機為複雜指令系統計算機,簡稱CISC。這種計算機採用的微處理器屬於CISC結構的微處理器。在CISC微處理器中,程式的各條指令是按順序串列執行的;每條指令中的各個操作也是按順序串列執行的。順序執行的優點是控制簡單,但機器各部分的利用率不高,執行速度慢。Intel的80386系列就屬於CISC結構的微處理器。

對CISC機進行測試表明,各種指令的使用頻度相當懸殊,最常使用的是一些比較簡單的指令,它們僅占指令總數的20%,但在程式中出現的頻度卻占80%。複雜的指令系統必然增加微處理器的複雜性,使微處理器研製時間長、成本高。複雜指令需要複雜的操作,從而降低了機器的速度。

RISC微處理器

70年代末,John Cocke提出精簡指令的想法。80年代初史丹福大學研製出MIPS機,為精簡指令系統計算機(簡稱RISC)的誕生與發展起了很大作用。RISC機中採用的微處理器統稱RISC處理器。MIPS R3000,HP-PA8000系列,Motorola M88000等均屬於RISC微處理器。它們的指令數目只有幾十條。RISC微處理器不僅精簡了指令系統,還採用超標量和超流水線結構,大大增強了並行處理能力,並在構建並行精簡指令系統多處理機中起著核心的作用。由於RISC處理器指令簡單、採用硬布線控制邏輯、處理能力強、速度快,世界上絕大部分UNIX工作站和伺服器廠商均採用RISC晶片作CPU用。這些RISC晶片的時鐘頻率低,功率消耗少,溫升也少,機器不易發生故障和老化,提高了系統的可靠性。

EPIC微處理器

何謂64位計算機?現今工業界對64位計算機的描述,是指具有64位運算能力、64位定址空間和64位數據通路的計算機。

64位的硬體環境能提供的好處:

(1)64位的CPU和數據通路,可以提供快速雙精度的運算能力;

(2)64位的指針可以提供大於1TB的虛擬存儲空間,檔案長度可以大於1TB;

(3)物理地址空間大於1TB。

64位CPU可以快速而精確地執行應用程式,允許程式人員在設計程式時可以使用比以往更大的資料庫和存儲空間,可以處理很複雜的計算模型。簡單地說,EPIC處理器首先由編譯程式分析指令之間的依賴關係;然後將沒有依賴關係的指令組合成群;最後由內置的執行單元讀入指令群並分頭並行執行。由於各條指令究竟分配給哪個單元是由編譯器來決定的,而不是由硬體進行調度,因此降低了處理器的製造成本。

Intel的Intanium(安騰)處理器和AMD的Athlon(速龍)處理器均屬於64位的EPIC微處理器,兩者均採用0.18微米的CMOS製造工藝。不同的是IA- 64的奔騰處理器與IA-32應用程式不能完全兼容,而AMD的x86- 64可以運行IA-32的應用程式。因此在64位的EPIC處理器戰場上,Intel和AMD兩大廠商展開了激烈的競爭。

Alpha處理器

Alpha的設計思想可以用一句話來概括:一個聰明的編譯程式和一個聰明的處理器開發Alpha體系結構的明顯目標是實現在編譯程式、處理器體系結構和實際線路設計等方面都能夠創造性地提高性能。Alpha設計成能夠利用編譯時和運行時的信息。當編譯出錯時,設計了一個無序指令傳送機制使得計算機能夠適應程式的運行過程而不是阻塞計算機的運行。此外,編譯程式在程式中只有有限的視野,經常不能跨過子程式或模組的邊界進行最佳化。同時多執行緒允許Alpha處理器除了指令級並行外還能夠利用執行緒級並行。Alpha是為廣泛範圍的商業套用設計的。同時,多執行緒是Alpha無序指令執行的自然擴展,它也是在大多數套用負載下利用顯性並行的最有效機制。

MIPS處理器

MIPS 84000是最早推出的64位處理器之一。SGI在收購MIPS(後MIPS又獨立)之後繼續發展T系列的64位處理器,先後推出了R6000,R8000,R10000,R12000等型號。

MIPS 812000是超標量的RISC微處理器,它採用ANDES(無序動態執行和調度)的體系結構。在每個流水線周期內可對4條指令進行解碼。該微處理器有5條執行流水線分別連線到整數和浮點執行單元,並具有推理機制及無序動態執行機制。

H2是一種設計用於滿足用戶在今後十年使用的最苛求的技術和商業計算套用需要的新型微處理器系列。利用在處理單和多處理器環境中迅速將大數據集合從CPU輸出和輸入到CPU的技術,這種微處理器系列集成了消除處理器與系統設計之間存在的傳統瓶頸的創新記憶體。在保持編碼和指令集兼容性的同時,H2將為大型可伸縮伺服器級計算機到桌面系統提供動力。

微處理器晶片的新發展

過去的微處理器主頻大多比較低,不斷提高主頻、降低線寬、採用超流水、多發射等技術是提高處理器性能的主要設計方法,處理器主頻高低幾乎成為微處理器性能強弱的代名詞。隨著主頻持續增長在物理設計上出現了一些困難。特別是處理器性能增長速度遠低於處理器主頻的增長速度。以Intel公司微處理器發展歷史為例,從I486發展到Pentium 4,處理器主頻增長了15倍,但性能才提高5倍。另外傳統的提高性能方法易導致晶片面積增大、功耗過大、電晶體數量過多等一系列問題。隨著處理器設計技術和生產工藝的發展,處理器突破性的性能提升還必須依賴處理器的結構更新。

2001年以後微處理器微系統結構設計中出現了一些令人矚目的新變化。如主頻的增長不再符合摩爾定律,主頻高低不再是最關鍵的處理器性能評價指標,執行緒級並行變得更普遍,64位計算正在向低端用戶普及、支持無線上網且低功耗的處理器成為筆記本電腦的主流。新技術的原理是什麼?如何實現?是什麼原因導致要採用新技術而不是傳統的微系統結構技術?以上問題應從技術和套用需求等多個角度進行考察,主頻增長困難的前提下,確保微處理器性能繼續提高的新技術進行考察,對新技術的原理、效果、必要性以及套用需求進行介紹和分析。

追隨CISC還是轉向RISC

RISC(全稱Reduced Instruction Set Computer,精簡指令系統計算機)是一套最佳化過的指令架構,它是根據著名的80/20法則所訂立。計算機科學家們發現,計算機中80%的任務只是動用了大約20%的指令,而剩下20%的任務才有機會使用到其他80%的指令。如果對指令系統作相應的最佳化,就可以從根本上快速提高處理器的執行率。

IBM公司在1975年成功開發出第一款RISC處理器,從此RISC架構開始走進超級計算機中。由於指令高度簡約,RISC處理器的電晶體規模普遍都很小而性能強大,深受超級計算機廠商所青睞。

無論在執行效率、晶片功耗還是製造成本上,選擇RISC都比沿用X86更加英明。在工藝相同的情況下,晶片面積大小取決於所集成的電晶體規模。RISC處理器核心精簡、效率更高,只要很少的電晶體就能達到與X86產品媲美的效能,製造成本可大大低於現有的X86處理器。而小電晶體規模亦有助於保持較低的能耗值,RISC處理器在這方面表現相當傑出,現在的嵌入式設備幾乎都採用RISC產品,原因就在於這類產品的功耗值超低。

PARROT基於RISC思想

Intel在IDF技術峰會上提出的”PARROT'概念便充分體現了這種思想。PARROT的全稱是“Power Awareness through Selective Dynamically Optimized Traces”,從其名稱不難得知,PARROT是一項藉助”動態最佳化執行路徑”來提高處理器執行效率的技術。它的理論基礎也是著名的80/20法則,但與RISC不同,X86處理器無法從指令系統層面上實現這一點。Intel另闢蹊徑,提出了一個全新的發展思路,將20%的常用指令定義為“熱代碼(Hot Code)”,剩餘的80%指令使用頻率沒那么高,被定義為“冷代碼(Cold Code) ”。對應的CPU也在邏輯上被劃分為兩個部分:一是熱核(Hot印ot),只針對調用到熱代碼的程式;另一部分則是冷核(Cold Spot),負責執行20%的次常用任務。由於熱核部分要執行80%的任務,設計者便可以將它設計得較為強大,占據更多的電晶體資源。而冷核部分任務相對簡單,沒有必要在它身上花費同樣的功夫。

“PARROT”創造了一種嶄新的雙核概念,過去我們談論的雙核心是橫向維度的對等設計。而PARROT則是一種縱向維度的雙核理念,熱核與冷核地位並不對等,且無法獨立運作,只能說是一個CPU核心中的兩部分分立邏輯。它所起到的是提高CPU的硬體資源利用率,以高執行效率達到高效能的目的,這種做法顯然比目前業界鼓吹的“雙核心”更具革命意義。

PARROT的新奇思路令人耳目一新,通過對執行單元的結構性最佳化,X86處理器可以說是獲得了重生。設計者可以對“熱核”部分進行大大強化,使之擁有更高的效能,在執行多數任務時用戶都可感覺到立竿見影的性能提升,而對於冷核的必要壓縮則大幅度節省了電晶體資源,並可達到明顯降低晶片功耗的目的。設計者可以在電晶體規模不變的前提下,讓X86處理器獲得數倍的效能提升。毫無疑問,X86處理器將因此出現跨越性的技術進步。而換個角度看,PARROT完全可以說是RISC思想的偉大勝利,80/20法則再度成為魔法的關鍵。據悉,PARROT技術將在2007年開始進入實用,"Merom”將成為首款基於PARROT思想的處理器核心。大家一定看過這樣的新聞:2007年Intel的伺服器處理器、桌面處理器和移動處理器都將採用“Merom”核心,無論性能還是功耗都將有出色的表現,我們有足夠的理由對它寄以厚望。

分散式計算思想

分散式計算的核心思想很簡單:讓整個網路的計算機系統聯結為一體,使之可以用共同的計算力來執行同一個任務。分布計算網路內的計算機數量越多,該網路所擁有的計算力就越強大。

我們知道,PC的功能一直都在不斷延伸,所面對的任務也變得越來越複雜,而硬體技術的發展似乎永遠不夠一往往在你驚嘆某款X86處理器多快多快的時候,一項新出現的大型套用就足以讓它捉襟見肘,例如,將DVD壓縮成DIVX、編輯高解析度的複雜圖像、JD環境渲染生成、大檔案壓縮和解壓、HDTV編解碼、大型JD遊戲等等,一般的PC很難勝任這些任務,但如果處理器可直接支持分散式計算,問題便迎刃而解了。藉助分布計算網路,每一台計算機都有了強大的後盾,參與運算工作的並非只有本機,而是整個計算機網路,即便本機的性能不高,照樣可以很輕鬆完成高度複雜的任務。而計算網路的規模越龐大,所具有的計算力就越可觀,相信這不論對於大中型企業客戶,還是普通家庭用戶都有非常積極的意義。

讓PC同步執行兩套系統

在以往,這種多作業系統技術僅限於超級計算機領域,但Intel決定讓PC也擁有同樣的功能,並發展出一套名為“Van-derpool”的技術。要在同一個硬體平台上同時生成兩套操作環境並不容易,Vanderpool如何解決二者可能存在的衝突問題?Intel引入了一項名為“VMM (virtual machine monitor,虛擬機監控器)”的技術解決了問題。首先,Vanderpool在硬體平台上分別構建了隔絕的邏輯區,每個邏輯區都包含完整的運作狀態,它們包括處理器的運算資源和記憶體資源;其次,VMM可對處理器、記憶體和其他硬體資源進行統一的管理和分配,確保每個操作環境都可以獲得相應的計算資源,由此保證多個操作環境同步運作。這樣在用戶看來,他所面對的就是兩套同步運行,且完全獨立的操作環境。而常規的計算機系統只有三層邏輯結構,自上而下分別是套用軟體、作業系統和底層硬體,未有起銜接作用的”虛擬機”層。

更有效地利用能源

功耗過高可以說是目前X86處理器所遇到的最大問題。Pre Scott核心的Pentium 4處理器功耗突破100瓦大關,而Pentium 4 600系列更將達到130瓦的驚人水平,這不僅僅意味著大量的能源消耗,系統穩定性也成問題。

然而,CPU所消耗的這些能源絕大多數都沒有得到利用,其有效利用率竟然只有0.1%的低水平。在去年2月份召開的“國際固態電路年會”上,與會專家對此問題提出許多積極的意見。

其中,東京大學的Takayasau Sakurai在會上發表一項電壓和頻率縮放技術,該技術可根據軟體的負載情況來直接調整電晶體的閡值電壓,如果系統執行的是需要大量計算的任務,處理器便會以最快的時鐘頻率和最高的電壓運行。如果該技術能被未來的微處理器所採納,能源浪費現象將可得到很大程度的緩解。

全美達公司的技術總監戴維也在大力推銷自己的LongRun2節能技術,除了繼承上一代技術的動態調節電壓/頻率特性外,LongRun2最主要的新特性就是可對電晶體漏電流進行有效的控制。隨著半導體製造工藝的升級,電晶體線寬變得越來越小,各邏輯門間的障壁也越來越薄,漏電流現象就變得越發難以控制。90納米Pre Scott核心的功耗過高、漏電流是一個很重要的因素,這也是半導體業界所面臨的共同難題。而全美達的LongRun2技術卻從晶片設計角度上很好解決了這個問題。