同步狀態機相對於控制器,它將一項功能完成分成若干步驟,每一步對應於一個二進制的狀態。

基本介紹

- 中文名:同步狀態機

- 領域:計算機

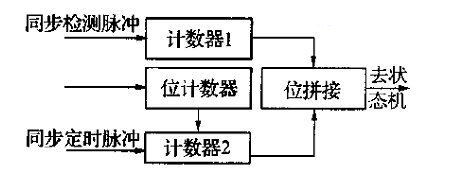

同步狀態的搜尋與接收系統定時

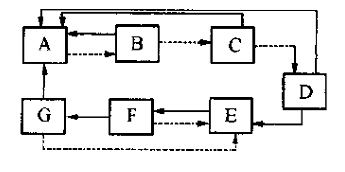

同步狀態轉移分析

狀態機的控制與編碼

同步狀態機相對於控制器,它將一項功能完成分成若干步驟,每一步對應於一個二進制的狀態。

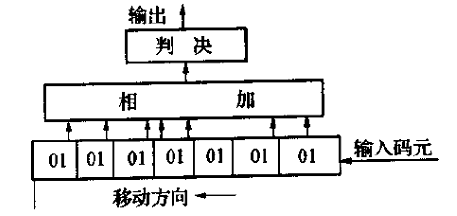

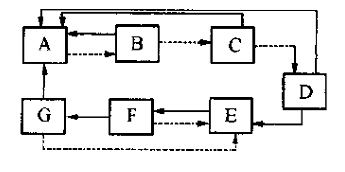

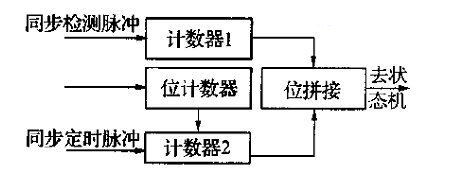

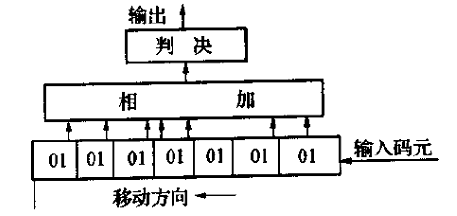

同步狀態機相對於控制器,它將一項功能完成分成若干步驟,每一步對應於一個二進制的狀態。同步狀態的搜尋與接收系統定時巴克碼的檢測同步狀態的搜尋是在對巴克碼檢測的基礎上實現的。我們採用7位移位暫存器、加法器和比較器實現巴克碼的...

一個為時序電路主要負責狀態變數的更新,此進程為同步電路,而另一個進程語句主要是描述下次態變數和輸出的更新。n 三個進程 第一個進程主要負責狀態變數的更新,第二個進程語句負責描述次態變數,而最後一個則是負責輸出信號的更新。有了以上的初步觀念,可以設計圖1四個狀態的Moore狀態機。範例 首先根據之前的狀態...

one-hot 狀態機有一個缺點,它的狀態每次發生跳轉,很多狀態位都會發生變化。首先,狀態機的輸出往往是由狀態位組合生成的。同時變化的狀態位越多,組合輸出穩定前所需的時間就越長,產生的毛刺就越多。如果該輸出不經同步就直接連線到暫存器的時鐘、使能、或鎖存器的使能等控制連線埠,將很容易導致數據的破壞(正統...

Leslie Lamport在1984年發表的關於“在分散式系統中使用時間而不是逾時”的論文中首次提出了狀態機方法。弗雷德·施耐德(Fred Schneider)後來在他的論文“使用狀態機方法實現容錯服務:教程”中闡述了這種方法。Ken Birman在1985年到1987年間發表的一系列論文中發展了虛擬同步模型。這項工作的主要參考文獻是“利用分散式...

3.1.1 實現狀態機的傳統方法 3.1.2 UML和visualSTATE狀態機設計規則 3.2 visualSTATE狀態機元素 3.2.1 visualSTATE中的狀態 3,2.2 visualSTATE中的轉換 3.2.3 visualSTATE中的激勵 3.3 visualSTATE狀態機的並髮結構 3.3.1 並發編程 3.3.2 交通燈控制器實例 3.3.3 狀態機同步 3.4 討論 第4章...

3.2 在Verilog HDL設計中啟用同步時序邏輯 思考題 第四講 同步狀態機的原理、結構和設計 概述 4.1 狀態機的結構 4.2 Mealy狀態機和Moore狀態機的不同點 4.3 如何用Verilog來描述可綜合的狀態機 思考題 第五講 設計可綜合的狀態機的指導原則 概述 5.1 用Verilog HDL語言設計可綜合的狀態機的指導原則 5.2...

主要有:有限自動機和無限自動機、線性自動機和非線性自動機、確定型自動機和不確定型自動機、同步自動機和異步自動機、級聯自動機和細胞自動機等。術語 自動機有如下基本概念:符號 有某種意義或在這個機器上有效的任意數據(datum)。符號有時就叫做“字母”。字 通過一些符號串接而形成的有限字元串。字母表 符號的...

5.3 時鐘同步狀態機分析 5.3.1 狀態機結構 5.3.2 輸出邏輯 5.3.3 特徵方程 5.3.4 使用D觸發器的狀態機分析 5.4 時鐘同步狀態機設計 5.4.1 狀態表設計舉例 5.4.2 狀態最小化 5.4.3 狀態賦值 5.4.4 採用D觸發器的綜合 *5.4.5 採用J-K觸發器的綜合 5.4.6 採用D觸發器的其他設計例子...

11.4 在Verilog HDL設計中啟用同步時序邏輯 11.5 數據接口的同步方法 小結 思考題 第12章 同步狀態機的原理、結構和設計 概述 12.1 狀態機的結構 12.2 Mealy狀態機和Moore狀態機的不同點 12.3 如何用Verilog來描述可綜合的狀態機 12.3.1 用可綜合Verilog模組設計狀態機的典型辦法 12.3.2 用可綜合的...

第12章同步狀態機的原理、結構和設計 概述 12.1狀態機的結構 12.2Mealy狀態機和Moore 狀態機的不同點 12.3如何用Verilog來描述可綜合的狀態機 12.3.1用可綜合Verilog模組設計狀態機的典型辦法 12.3.2用可綜合的Verilog模組設計、用獨熱碼錶示狀態的狀態機 12.3.3用可綜合的Verilog模組設計、由輸出指定的碼...

同步動態隨機存取記憶體(synchronous dynamic random-access memory,簡稱SDRAM)是有一個同步接口的動態隨機存取記憶體(DRAM)。通常DRAM是有一個異步接口的,這樣它可以隨時回響控制輸入的變化。而SDRAM有一個同步接口,在回響控制輸入前會等待一個時鐘信號,這樣就能和計算機的系統匯流排同步。時鐘被用來驅動一個有限狀態機,...

第1章和第2章為Verilog HDL基礎知識;第3章從一個典型數字電路實例入手,詳細介紹了Verilog HDL的常用建模方法;第4章介紹了一些常用的組合邏輯電路和時序邏輯電路;第5章從一個典型時序邏輯電路實例入手,引入同步有限狀態機,並進一步探討了同步狀態機的特徵;第6章則詳細介紹了VerilogHDL的仿真技術,並對ModelSim...

3.4 同步狀態機的原理與設計 3.4.1 什麼是狀態機 3.4.2 狀態機的設計原理 3.4.3 典型的狀態機實例 3.5 Verioog HDL可綜合的代碼風格 3.5.P 可綜合代碼編寫原則 3.5.2 FPGA設計時aoways語句塊使用注意事項 3.6 Verilog HDL仿真驗證平台 3.6.1 Modelsim仿真工具介紹 3.6.2 Modelsim的使用 3.6....

7.1.1同步時序電路的特點與結構 7.1.2同步時序電路的別名——同步狀態機 7.1.3同步時序電路的描述方法 7.2同步時序邏輯電路——狀態機的分析 7.2.1同步時序電路的分析步驟 7.2.2同步時序電路分析實例 7.3同步時序邏輯電路——狀態機的設計 7.3.1原始狀態圖(表)的建立——邏輯抽象 7.3.2...

4.4 有限同步狀態機 本章小結 思考題和習題 第5章仿真驗證與testbench編寫 5.1 Verilog HDL電路仿真和驗證概述 5.2 Verilog HDL測試程式設計基礎 5.2.1 Testbench及其結構 5.2.2 測試平台舉例 5.2.3 Verilog HDL仿真結果確認 5.2.4 Verilog HDL仿真效率 5.3 與仿真相關的系統任務 5.3.1 $dJsplay和...

有限狀態機的設計方法 在使用Verilog HDL進行電路輸入時,為了保證所編寫的代碼是可以綜合成數字電路的,以及綜合前和綜合後仿真的一致性,必須按照一定的原則編寫代碼。當時序邏輯比較複雜時,一般將其抽象成一個同步的有限狀態機(FSM: FiniteState Machine,以實現可綜合風格的Verilog HDL設計)可綜合的有限狀態機有...

第1章和第2章為Verilog HDL基礎知識;第3章從一個典型數字電路實例入手,詳細介紹了Verilog HDL的常用建模方法;第4章介紹了一些常用的組合邏輯電路和時序邏輯電路;第5章從一個典型時序邏輯電路實例入手,引入同步有限狀態機,並進一步探討了同步狀態機的特徵;第6章則詳細介紹了Verilog HDL的仿真技術,並對ModelSim...

EtherCAT(乙太網控制自動化技術)是一個開放架構,以乙太網為基礎的現場匯流排系統,其名稱的CAT為控制自動化技術(Control Automation Technology)字首的縮寫。EtherCAT是確定性的工業乙太網,最早是由德國的Beckhoff公司研發。自動化對通訊一般會要求較短的資料更新時間(或稱為周期時間)、資料同步時的通訊抖動量低,...

4.4 有限同步狀態機 105 本章小結 115 思考題和習題 115 第5章 仿真驗證與Testbench編寫 119 5.1 Verilog HDL電路仿真和驗證概述 119 5.2 Verilog HDL測試程式設計基礎 120 5.2.1 Testbench及其結構 120 5.2.2 測試平台舉例 123 5.2.3 Verilog HDL仿真結果確認 126 5.2.4 Verilog HDL仿真效率 128 ...

第9章狀態機圖 153 9.1狀態機概述 154 9.1.1狀態機及其構成 154 9.1.2狀態機圖示記符 154 9.2轉移 155 9.2.1轉移的定義 155 9.2.2事件 156 9.2.3動作 158 9.2.4轉移的類型 159 9.3組合狀態 160 9.3.1順序狀態 160 9.3.2並發子狀態 160 9.3.3同步狀態 161 9.3.4歷史狀態 161 9...

7.1.1 同步時序電路的特點與結構 211 7.1.2 同步狀態機 214 7.1.3 同步時序電路的描述方法 219 7.2 同步時序邏輯電路——狀態機的分析 226 7.2.1 同步時序電路的分析步驟 226 7.2.2 同步時序電路分析實例 227 7.3 同步時序邏輯電路——狀態機的設計 235 7.3.1 邏輯抽象 ...

USART 支持4 種模式的時鐘: 正常的異步模式,倍速的異步模式,主機同步模式,以及從機同步模式。USART 控制位UMSEL和狀態暫存器C (UCSRC) 用於選擇異步模式和同步模式。倍速模式( 只適用於異步模式) 受控於UCSRA 暫存器的U2X。使用同步模式 (UMSEL = 1) 時,XCK 的數據方向暫存器 (DDR_XCK)決定時鐘源是由內部...

第十二章 同步狀態機的原理、結構和設計 第十三章 設計可綜合狀態機的指導原則 第十四章 深入理解阻塞和非阻塞賦值 第十五章 較複雜時序邏輯電路設計實踐 第十六章 復時序邏輯電路設計實踐 第十七章 簡化的RISC CPU設計 第十八章 虛擬器件、虛擬接口模型、基於平台的設計方法及其在大型數字系統設計中的套用 參考文獻...

4.6.1 同步靜態RAM 100 4.6.2 DRAM 103 4.6.3 SDRAM 104 4.7 小結 109 第5章 同步狀態機設計與分析 110 5.1 引言 110 5.2 時序狀態機模型 112 5.3 全記錄狀態圖 115 5.4 基本記憶單元 118 5.4.1 置位優先基本單元 118 5.4.2 復位優先基本單元 120 5.4.3 激勵表...

第9章 狀態機圖 156 9.1 狀態機概述 156 9.1.1 狀態機及其構成 157 9.1.2 狀態機圖示記符 157 9.2 轉移 159 9.2.1 什麼是轉移 159 9.2.2 事件 160 9.2.3 動作 163 9.2.4 轉移的類型 164 9.3 組合狀態 165 9.3.1 順序狀態 165 9.3.2 並發子狀態 166 9.3.3 同步狀態 167 9....

4. 1 時鐘同步狀態機的設計 84 4. 1. 1 時鐘同步狀態機及其設計流程 84 4. 1. 2 時鐘同步狀態機設計方法構建序列發生器 86 4. 1. 3 狀態圖直接描述法實現序列發生器 90 4. 2 同步計數器74x163 的實現 94 4. 3 移位暫存器的實現和套用 97 4. 3. 1 74x194 的實現 97 4. 3. 2 使用...

9.3.8Moore?Mealy同步時序狀態機 9.3.9Moore同步時序狀態機 9.3.10Moore異步時序狀態機 9.3.11Moore脈衝模式異步時序狀態機 9.4習題第10章任務和函式 10.1任務 10.1.1任務聲明 10.1.2任務調用 10.2函式 10.2.1函式聲明 10.2.2函式調用 10.3習題第11章補充設計實例 11.1詹森計數器 11.2計數...

4. 1 時鐘同步狀態機的設計 84 4. 1. 1 時鐘同步狀態機及其設計流程 84 4. 1. 2 時鐘同步狀態機設計方法構建序列發生器 86 4. 1. 3 狀態圖直接描述法實現序列發生器 90 4. 2 同步計數器74x163 的實現 94 4. 3 移位暫存器的實現和套用 97 4. 3. 1 74x194 的實現 97 4. 3. 2 使用...

第9章 狀態機圖 143 9.1 狀態機圖概述 144 9.1.1 狀態機及其構成 144 9.1.2 狀態機圖示記符 144 9.2 轉移 146 9.2.1 轉移簡介 146 9.2.2 事件 147 9.2.3 動作 150 9.2.4 轉移的類型 151 9.3 組合狀態 152 9.3.1 順序狀態 153 9.3.2 並發子狀態 153 9.3.3 同步狀態 154 9....

第6章狀態圖 6.1概述 6.2狀態 6.2.1訊息 6.2.2狀態概念介紹 6.2.3狀態的種類 6.3狀態機 6.4狀態圖 6.5狀態遷移 6.5.1事件 6.5.2守衛條件 6.5.3動作表達式 6.5.4狀態遷移的種類 6.6並髮狀態圖 6.6.1並發子狀態 6.6.2同步 6.7狀態圖建模 6.7.1建立狀態圖 6.7.2狀態圖建模中應...