同或門(英語:XNOR gate或equivalence gate)也稱為異或非門,在異或門的輸出端再加上一個非門就構成了異或非門,是數字邏輯電路的基本單元,有2個輸入端、1個輸出端。當2個輸入端中有且只有一個是低電平(邏輯0)時,輸出為低電平。亦即當輸入電平相同時,輸出為高電平(邏輯1)。

基本介紹

- 中文名:同或門

- 外文名:equivalence gate

- 別名:異或非門

- 說明 :是數字邏輯電路的基本單元

- 邏輯:輸出同電平,輸出高電平

基本信息,實現,符號,

基本信息

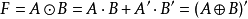

(1)邏輯表達式: (⊙為“同或”運算符)

(⊙為“同或”運算符)

(2)真值表:

| 輸入A | 輸入B | 輸出F |

|---|---|---|

0 | 0 | 1 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

同或門的邏輯特點是:當兩個輸入端一個為“0”,另一個為“1”時,輸出為“0”; 當兩個輸入端均為“1”或均為“0”時,輸出為“1”。該特點可簡記為:輸入相異,輸出 為“0”;輸入相同,輸出為“1”。

電路中較少使用“同或”門,並且“同或”門可用“異或”門串聯一個“非”門來實現。

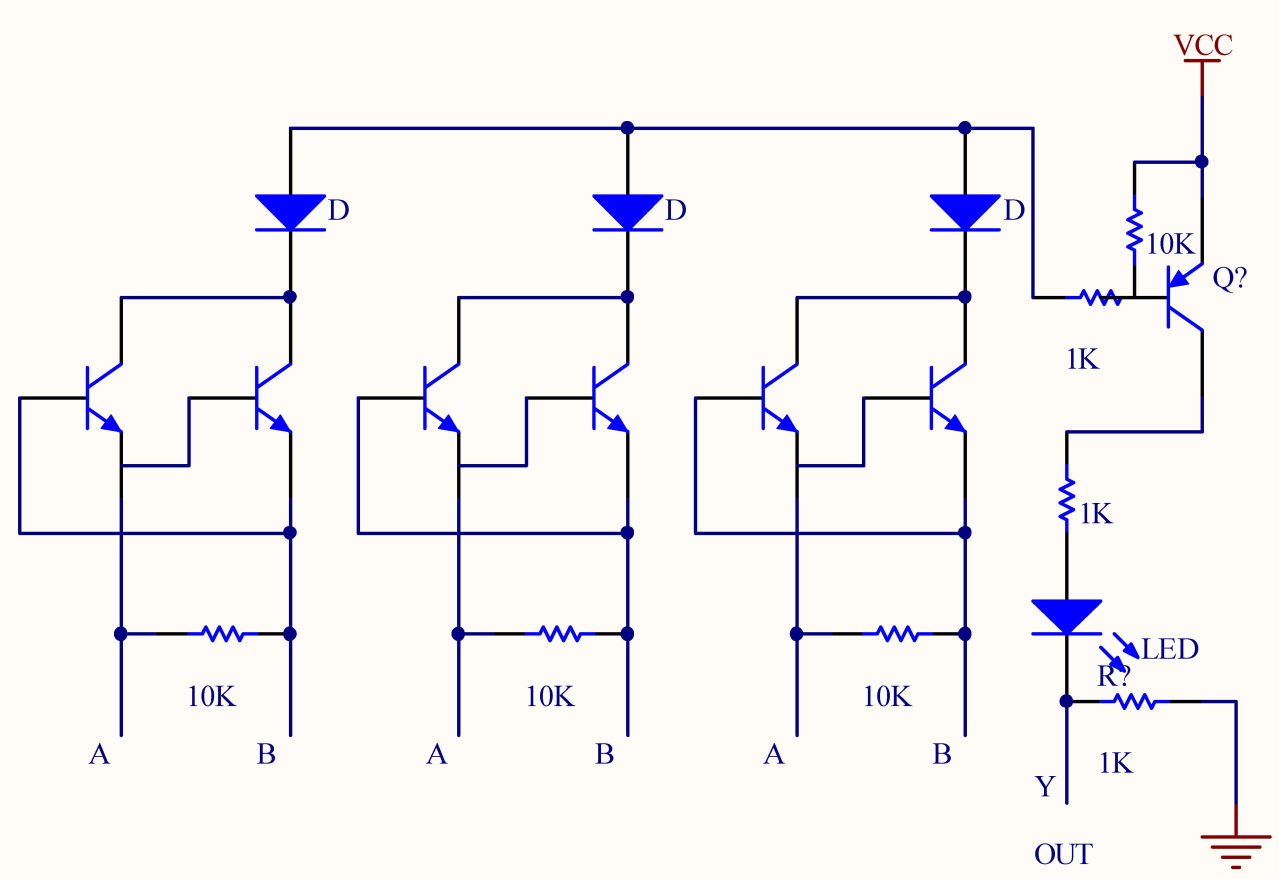

實現

同或門可以只有與非門或者或非門來構成。

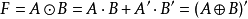

符號

ANSI/IEEE Std 91-1984

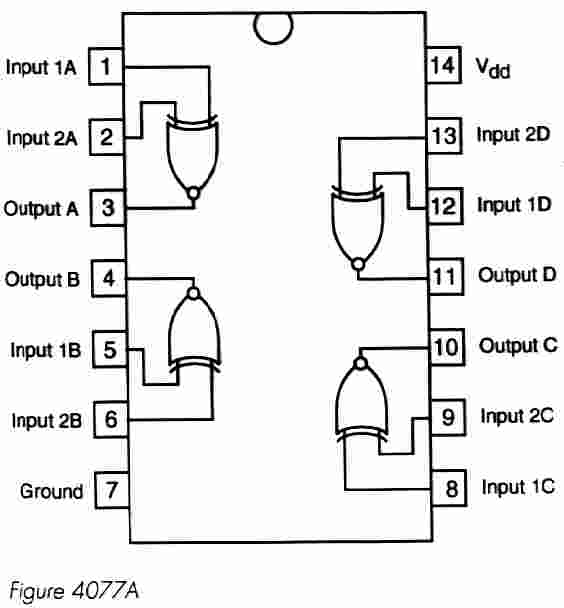

ANSI/IEEE Std 91-1984積體電路

積體電路的引腳分配圖

積體電路的引腳分配圖