簡介

可重構體系結構目前已成為學術界和工業界的研究熱點,並且已經有許多令人矚目的研究成果和工業產品面世。可重構計算系統提供了一種介於通用計算機和專用計算系統 ASIC之間的計算手段。通用計算機是面向通用套用領域進行設計的,其設計目標主要是能夠靈活地處理不同的計算任務,這使得通用計算機具有很大的靈活性和套用範圍,但對某些特殊的套用領域卻難以取得高性能。專用積體電路 ASIC 是針對某種特殊套用設計的計算系統,對於特定的計算任務,ASIC 表現出極高的性能,但無法處理特定計算任務之外的其它任務。通用計算機和 ASIC 代表了兩種極端的計算手段,通用計算機具有最大的靈活性和低性能,ASIC 具有最高的性能和最差的靈活性。而現在有許多套用需求既要求較高的性能,又需要一定的靈活性。例如,一個多媒體套用中可能包括數據並行處理、位處理、不規則計算、高精度字操作、具有實時要求的操作等子任務,要求處理系統能夠靈活地處理上述各個子任務並達到一定的性能。許多其它套用也具有類似的需求,如數據加密、人工智慧等,這些套用需求導致了可重構體系結構的產生。

可重構體系結構

如果某一計算系統能夠利用可重用的硬體資源,根據不同的套用需求,靈活的改變自身的體系結構,以便為每個特定的套用需求提供與之相匹配的體系結構,那么這一計算系統就稱為可重構的計算系統,其體系結構稱為可重構的體系結構。按照不同的分類標準,可以將可重構體系結構分為不同的類型,下面介紹一些常用的分類標準。

粒度

粒度是指系統中可重構成分(或稱可重構處理單元,RPU)的運算元的寬度。RPU 是功能可配置的邏輯塊,其內部連線關係是可重構的。在一個細粒度的可重構體系結構中,RPU 中的處理元素通常是邏輯門、觸發器、查找表等,它們進行位級操作,實現一個有限狀態機的布爾函式。而在粗粒度的可重構體系結構中,RPU 中的處理元素可能包括完整的功能單元,象算術邏輯單元 ALU、乘法器等,它們進行字(由多個位構成)級的操作。如果一個可重構體系結構中包括粗粒度和細粒度兩種RPU,則稱其為混合粒度的可重構體系結構。

編程深度

編程深度是指存儲在 RPU 中的配置程式或檔案的數量。一個 RPU 可能含有單個配置檔案或多個配置檔案。對於單配置檔案系統,只有一個配置檔案駐留在 RPU 內,因此 RPU 的功能局限於當前裝載的配置檔案。而在多配置檔案系統中,同時有多個配置檔案駐留在 RPU 內,這使得可以通過切換配置檔案很方便地實現不同的功能,而不必從外部重新裝載配置檔案。

可重構能力

在處理不同套用的過程中,一個 RPU 可能需要被頻繁地重構。重構實際上就是重新裝載配置檔案的過程。如果裝載配置檔案的過程必須在中斷程式執行的情況下進行,那么這種重構稱為靜態重構;如果裝載配置檔案的過程可以和程式執行同時進行,那么這種重構稱為動態重構。單配置檔案的可重構系統通常具有靜態重構的特性,而動態可重構系統往往基於多配置檔案的 RPU。動態重構系統中的 RPU,可以在運行部分配置檔案的同時,改變其它配置檔案。這一特性能夠大幅度地降低重新配置的時間開銷。

界面

如果一個可重構系統的主機和可重構處理單元 RPU 不在同一晶片上,那么稱這一可重構系統具有遠界面;反之,如果主機和可重構處理單元 RPU 在同一晶片上,則稱這一可重構系統具有本地界面。對於具有本地界面的可重構系統來說,RPU實際上已經融合在主機的數據通路中去了。

計算模型

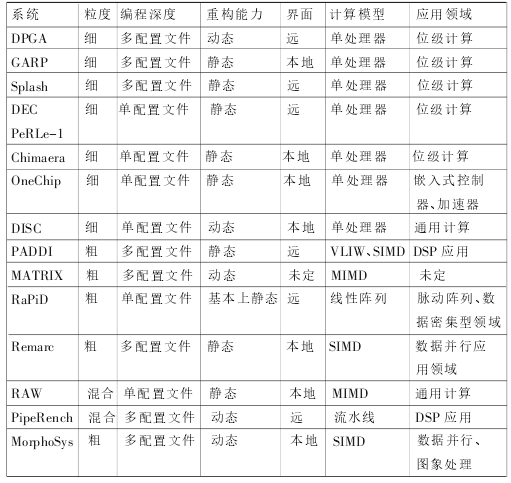

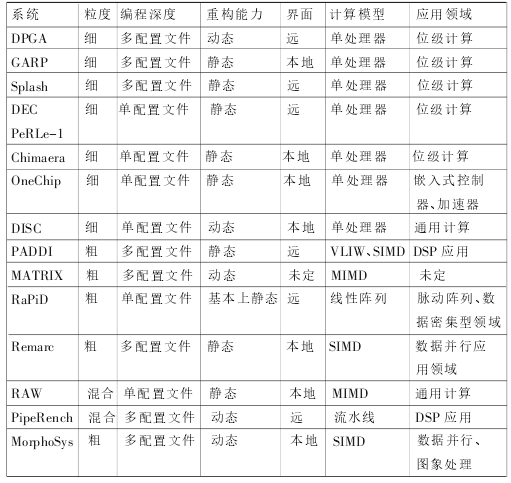

許多可重構系統遵循單處理器計算模型,有些可重構系統遵循單指令流多數據流 SIMD 或多指令流多數據流 MIMD 計算模型,另外還有一些可重構系統遵循 VLIW 計算模型。表列出了當前一些典型的可重構計算系統的主要特徵及套用領域。

特徵

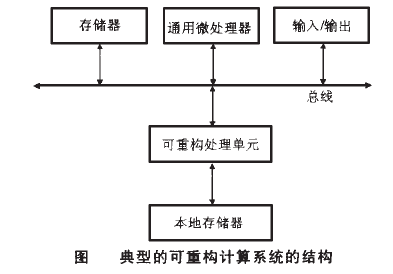

總體結構

可重構處理單元的結構

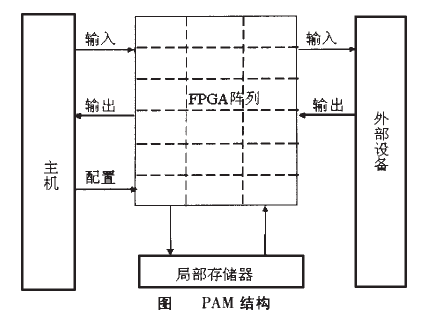

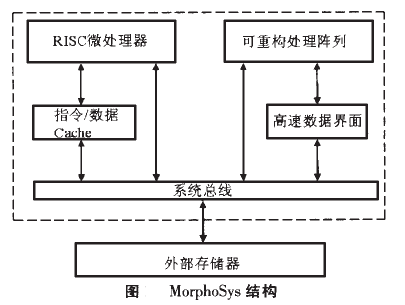

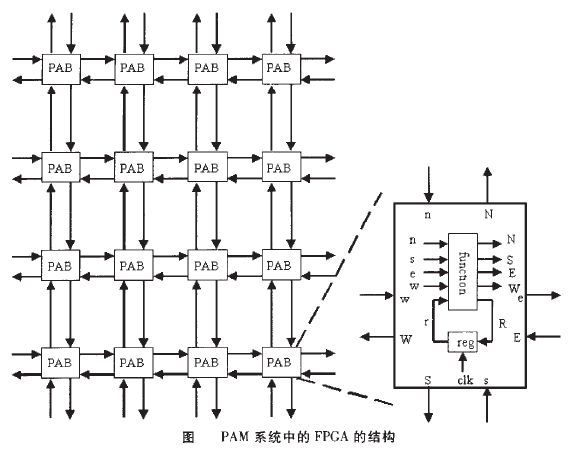

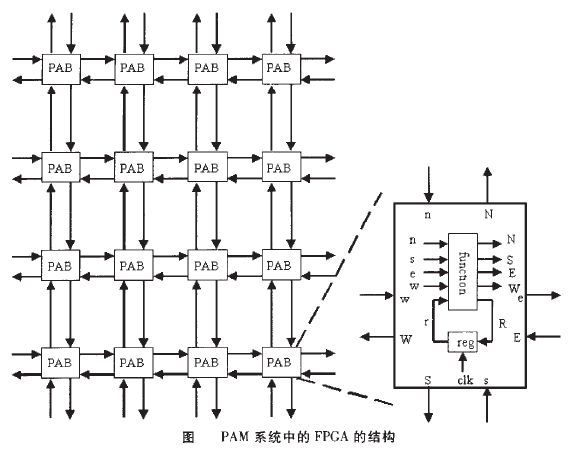

可重構計算系統的可重構處理單元 RPU (或者稱為可重構協處理器)主要有兩種類型,一種是現場可程式門陣列 FPGA,另一種是針對特定套用需求設計的可重構處理單元。例如上述 PAM 系統中採用 FPGA 作為可重構處理單元,而 MorphoSys 系統則採用了面向圖象處理、數據加密、DSP 變換等領域設計的可重構元素(RC)陣列作為它的可重構處理單元。它們的結構分別如圖所示。FPGA 的 基 本 組 成 成 分 是 可 配 置 的 邏 輯 塊 CLB(configurable logic block)或 者 稱 為 PAB(programmable active bits)。通常每個 CLB 包括組合函式模組、觸發器和內部連線,組合函式模組的輸入變數數通常在 2 到 6 之間,組合函式通常用查找表的方式實現,函式的真值表保存在局部暫存器,通過改寫真值表的內容,就可以改變函式關係;CLB 的內部連線關係是可重構的。各個 CLB 之間的連線結構通常採用二維格線(mesh)結構。

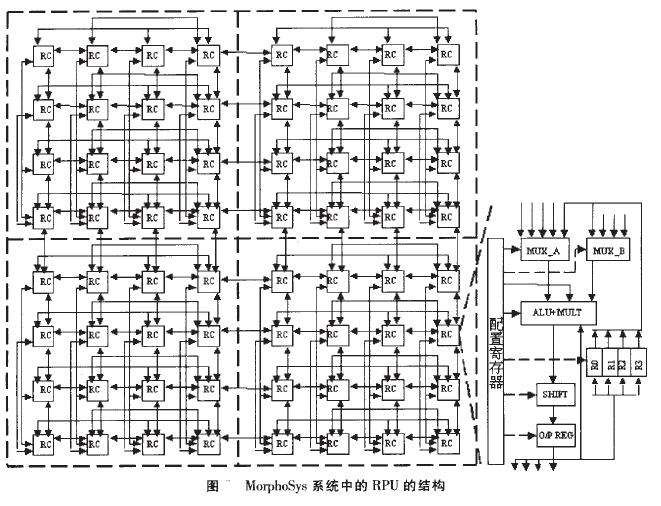

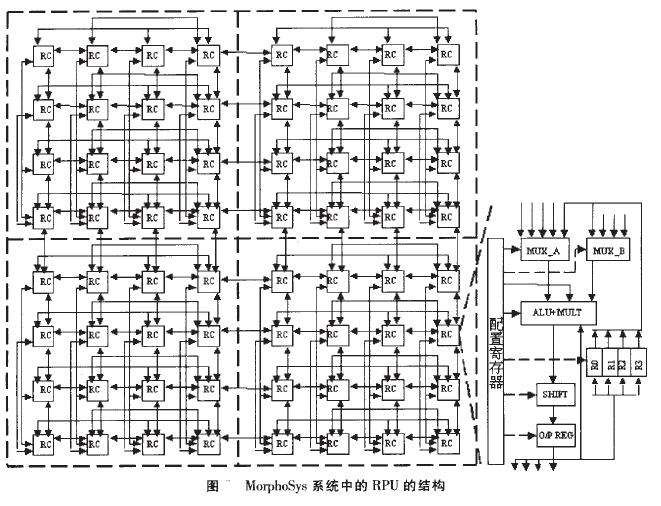

MorphoSys 系 統 中 的 RPU 是 由 可 重 構 元 素 RC(reconfigurable cell)構成的 8*8 陣列。每個 RC 包括一個配置。暫存器、兩個選通器、一個 ALU、一個乘法器、一個移位器、一個由 4 個 16 位暫存器構成的暫存器堆。8*8 陣列分成 4 個子陣列,4: 之間的連線採用二維格線連線和子陣列內的行 / 列完全連線。

可重構系統比較

所謂基於 FPGA 的可重構系統是指以 FPGA 為可重構處理單元的系統。FPGA 是細粒度的重構器件,其重構的基本元素是邏輯門、觸發器和連線,允許設計者使用門級的器件,因此FPGA 具有很大的靈活性,尤其適用於處理複雜的位計算。但是 FPGA 中的大量的可程式控制電路,在提供了很大的靈活性的同時,也使得寄生電容和數據傳輸路徑的長度增加,有效邏輯門的密度降低,從而增加了信號傳輸的延時,降低了運算速度。另外,FPGA 處理粗粒度操作的性能較差。基於 FPGA 的可重 構 系 統 的 例 子 有 :Splash、DEC PeRLe-1、Chimaera、DISC、PAM等。

問題

當前可重構體系結構的優點及存在的問題當前的可重構體系結構的優點可歸納如下:

能迅速地實現設計的硬體原型,進行邏輯模擬並可以作為ASIC的便宜的替代品。

能夠改變位寬(相反,常規的處理器一般具有固定的位寬)以便針對特定的套用提供相應的計算能力,因此具有達到最大並行性的潛力,能夠節省功耗。

對於多上下文的操作,能夠根據用戶的需求構成深度的空間或時間流水線。

硬體虛擬化允許多配置檔案和動態部分重構。

具有揭示數據流中的數據並行性的能力。

FPGA和其它成分的混合使用提供了從細粒度到粗粒度的多種不同粒度的操作。

當前的可重構體系結構中還存在下述問題:

浮點性能差。這可以通過集成一個具有良好的浮點性能的處理器核來解決。

有限的資源。這一問題將因百萬門的FPGA面世而得到緩解。

數據交換的效率低。製造商將在下一代產品中集成進存儲器來解決這一問題。

功耗大。如Xilinx 4003在20MHz的功耗達到2W。

細粒度的體系結構不能適應數據通路型的粗粒度的多媒體計算。將粗粒度和細粒度結合在一起的FPSC現場可程式片上系統(Field Programmable System on Chip)有可能適應上述情況。

90%的晶片面積被連線占用,這嚴重地降低了效率。

很長的配置時間和編譯時間。