基本介紹

- 中文名:十進制加法器

- 外文名:Decimal Adder

計算機中對十進制數的處理

計算機中常見的十進制表示

最常用的十進制加法器

加法器是常用的組合邏輯電路之一,可分為半加器和全加器。計算機對所有數據的處理本質上是對二進制數的處理。而人類熟悉的數據是十進制的,故我們需要設計出來十...

8位加法器就是實現兩個 8位二進制相加,其結果的範圍應該在00000000到111111110之間,八位二進制數換算成三位十進制數最大為255,也就是說要輸入兩個000到255之間...

進位信號代表在多位加法中需要溢出到更高一位的數字。因此,這兩個一位二級制數的和用十進制表示即等於2C+S。右圖是一個最簡單的半加器設計,使用一個異或門來...

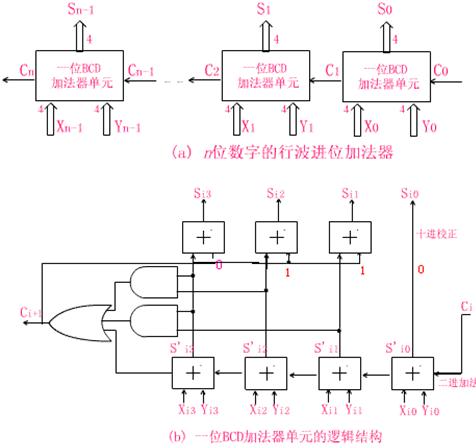

如果是BCD(用二進制表示的十進制數)碼加法器,和12中的個位2從∑輸出(BCD碼0010),十位1從輸出進位端C-out輸出。 加法運算 算術功能2.減法 ...

3.了解二—十進制全加器的工作原理。 【基本要求】 1.掌握半加器、全加器的工作原理; 2.掌握74LS283的工作原理及邏輯功能。 【實驗儀器、設備】 1.SXJ—3C...

數字電子技術(第十版)圖書內容 編輯 本書是一本關於數字電子技術的經典教材, ...6.1 基本加法器6.2 並行二進制加法器6.3 異步進位與超前進位加法器...

4.5.3陣列除法器1184.6規格化浮點運算1184.6.1浮點加減運算1194.6.2浮點乘除運算1214.6.3浮點運算器的實現1234.7十進制整數的加法運算123...

4.5.3陣列除法器1054.6規格化浮點運算1054.6.1浮點加減運算1054.6.2浮點乘除運算1084.6.3浮點運算器的實現1094.7十進制整數的加法運算109...

1642年,法國數學家帕斯卡採用與鐘錶類似的齒輪傳動裝置,製成了最早的十進制加法器。1678年,德國數學家萊布尼茲製成的計算機,進一步解決了十進制數的乘、除運算。...

6.2 並行二進制加法器 6.3 比較器 6.4 解碼器 6.5 編碼器 6.6 代碼轉換器 6.7 多路轉換器 6.8 多路復用器 6.9 奇偶發生器/校驗器 6.10 故障檢測 6...

【任務實施】加法器的設計與測試192【學習小結】193【自我評估】193【評價標準】194任務6 5一位十進制加法器的邏輯電路設計與製作194...

4.4 集成全加器 4.4.1 多位二進制數加法器 4.4.2 多位二進制數減法器 4.4.3 二一十進制(BCD碼)加法器 4.5 編碼器與解碼器 4.5.1 編碼器(Encoder...

3.10 硬體描述語言 3.11 習題 參考文獻 第4章 組合邏輯 4.1 引言 4.2 組合電路 4.3 分析步驟 4.4 設計步驟 4.5 二進制加減器 4.6 十進制加法器 4.7 二進制...