介質隔離(Dielectric isolation)技術是積體電路製造中的一種隔離元器件的方法。積體電路是由許多元器件構成的,各個元器件之間往往需要進行電絕緣體—隔離。常用的隔離技術有pn結隔離和介質隔離等。介質隔離是採用SiO2膜來實現隔離的,漏電小、耐壓高,性能優良,但是工藝比較複雜。

基本介紹

- 中文名:介質隔離技術

- 外文名:Dielectric isolation

- 目的:隔離元器件

- 優點:漏電小、耐壓高

- 屬於:隔離技術

- 其他:自隔離

簡介,隔離技術,PIC介質隔離技術,

簡介

採用絕緣性能好的電介質來消除各電子元件之間的相互影響的工藝方法稱為介質隔離技術。這種隔離方法的優點是各元件之間的漏電流和隔離區分布電容比P-N結隔離要小得多。它適於在高頻線性放大積體電路和高速數字積體電路中使用。但由於電介質的導熱性能較差,所以它在大功率積體電路中使用時,散熱能力比P-N結隔離法差。

隔離技術

在功率積體電路中,各器件做在同一個矽襯底上,由於矽襯底是導電的,為了避免各器件之間的相互影響,必須進行電隔離。並且,高壓電晶體與低壓電晶體之間的電隔離尤為重要。

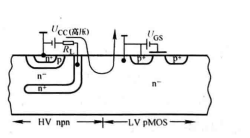

如下圖所示,如果在n-襯底上有一個高壓npn電晶體和一個低壓pMOS管,若兩者之間不隔離,不僅會產生一個微小的漏電流使功耗增加,而且柵氧化層(約lOOnm)很難承受pMOS柵極與襯底之間跨接的高電壓,因此兩者之間必須加以隔離。

隔離技術

隔離技術PIC介質隔離技術

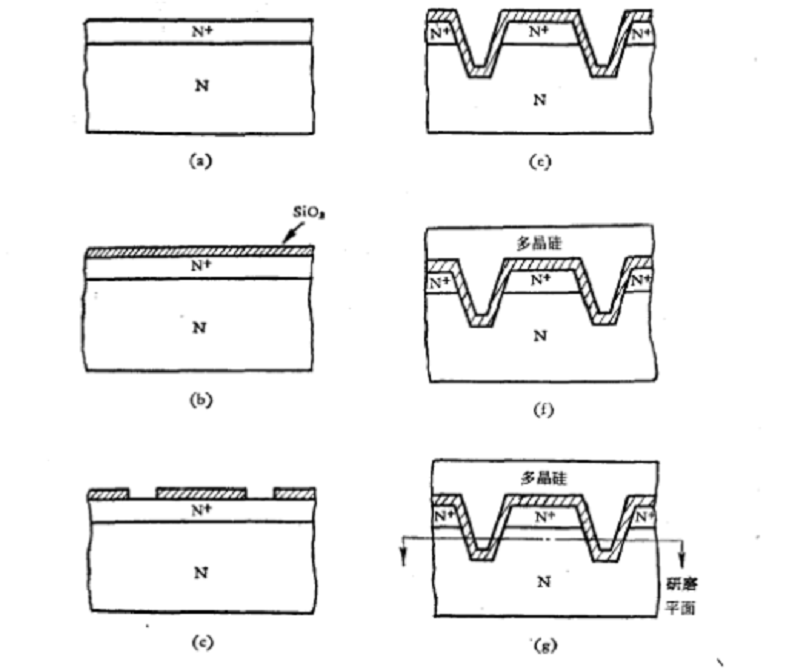

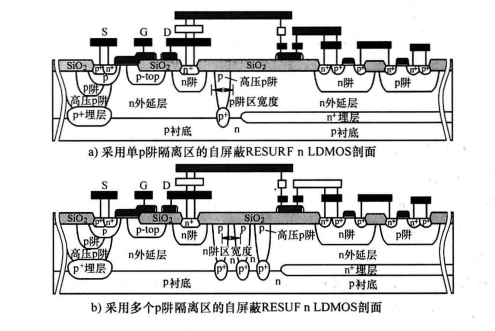

PIC中的介質隔離與VLIC中的基本相同,並可以利用介質隔離來改善器件的特性。如圖中a所示,採用常規的介質隔離,由於VDMOS的n-漂移區較厚,載流子在源、漏區之間傳輸時經歷的路徑較長,導致其導通電阻增大,漏極電流減小。如圖中b所示,若在底部增加V形槽後,可以縮短源、漏之間的距離,減小了n-漂移區的電阻,有利於提高電流密度,而且當A處源、漏之間的長度等於或大於B處源、漏之間的長度時,V形槽的引入不會影響其擊穿電壓。這種介質隔離可以通過調整刻蝕視窗的大小,利用離子注入形成n+漏區,通過熱生長形成隔離SiO2氧化層,之後可按照常規的介質隔離工藝來實現。

PIC介質隔離技術

PIC介質隔離技術採用介質隔離,器件之間絕緣隔離性能好,沒有漏電流,不會發生相互干擾和閂鎖現象。與結隔離相比,介質隔離區寬度可以做得很小,有利於減小晶片面積;由於SiO2絕緣性能好,故隔離電壓可高達lkV,且高溫漏電流小,但介質隔離的工藝比較複雜。