軟體簡介 把設計方法書放到一邊,然後回想一下會發生什麼。Altium Designer是一種單一的設計

軟體 ,卻能提供上百萬種的實現方法

不要把你的設計能力局限在某一個水平。讓自己從舊有的設計包中脫身,進入到全方位設計這種方法中。利用所有可用的的技術和工具來實現你的想法,讓這些想法變成日後被廣泛使用的聰明並相互關聯的產品。

Altium Designer要做的事情就是這樣:幫你衝破舊有設計思維的局限,打破限制,把你從原來的孤立而困難的方法中解放出來。Altium能幫助你不斷探索,用更多而且嶄新的方法做設計,並幫助你設計出前所未有的新玩意。

構思和設計時不用理會設備之間的界限。為你的客戶設計整個產品的歷程開啟了。探索出你在產品的軟硬體兩方面特性加入了什麼功能,並了解這個產品與更大的產品系統之間的關係。

新一代的電子設計工具,就是 Altium Designer.

英文名: altium designer summer

版本種類 7.0版本 Altium Designer Summer即Altium Designer 7.0,Altium Designer 7.0 不斷通過為高速設計提供各種功能來提高用戶生產力,這些功能包括互動式長度調整和 PCB 層片增強等功能。新增的庫工具和各種新功能將 Altium Designer 提升成為統一的電子產品開發解決方案。

這款最新的更新程式將進一步增強您的能力,讓您能夠在更短的“設計到製造”周期內生產更為尖端、更具創新性的電子產品。(Altium Designer完全取代了Protel)

Altium Designer Summer 08新增匯入Allegro PCB(*.brd)的轉檔案功能。

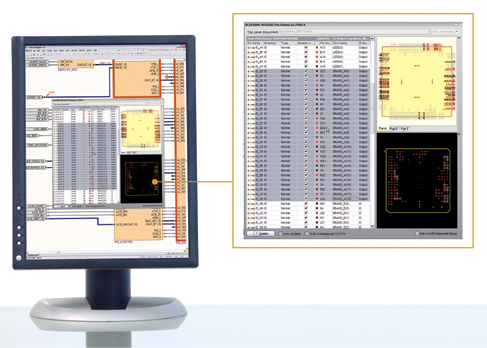

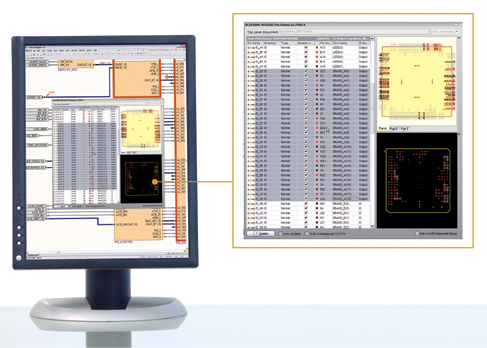

Altium Designer 提供了唯一一款統一的套用方案,其綜合電子產品一體化開發所需的所有必須技術和功能。Altium Designer 在單一設計環境中集成板級和FPGA系統設計、基於FPGA和分立處理器的嵌入式

軟體 開發以及PCB版圖設計、編輯和製造。並集成了現代設計數據管理功能,使得Altium Designer成為電子產品開發的完整解決方案-一個既滿足當前,也滿足未來開發需求的解決方案。

Altium Designer 7.0加強了FPGA-PCB

協同設計 能力

Windows電子設計

軟體 開發商Altium公司宣布其最新一體化電子產品開發系統Altium Designer 7.0極大地增強了FPGA-PCB

協同設計 的能力,工程師可以充分利用FPGA作為系統平台,而且簡化大型FPGA與物理PCB平台的集成。

雖然人們早就認識到了FPGA給邏輯開發帶來的好處,但把這些器件集成到PCB設計流程所帶來的挑戰,會使得PCB線路板設計變得十分複雜並導致整體設計時間超長。通常無需考慮PCB版圖即進行FPGA管腳分配,而在大規模可程式器件中使用的密集封裝技術將使得PCB板布線成為極大的挑戰。

Altium Designer打破了FPGA的使用障礙,把

硬連線 的PCB平台和

軟體 及軟連線的邏輯開發集成在一起,後者構成的嵌入式智慧型通過在PCB線路板上編程以創建完整的套用。

Altium Designer 6.0 改進了FPGA級設計和PCB級設計間的集成,開發了很多新功能,與現在的大型可程式器件相結合,它們精簡了產品開發。

“大型FPGA器件的可用性正改變著工程師的系統設計方法――產品中可以添加更多智慧型並同時縮短設計時間,減少製造成本。”Altium的創始人和CEO Nick Martin說,“Altium Designer 6.0可幫助工程師在嵌入式智慧型級和物理設計級充分利用FPGA提供的好處,系統的統一特性打破了在主流設計中廣泛採用可程式器件的障礙,這樣可以充分利用這些器件的擴展資源,簡化邏輯和物理設計。”

Altium Designer 6.0引入了

動態網路 重分配概念,PCB布線期間可線上交換FPGA管腳。這包括重新分配預先布線的子網和交換連結的差分信號對,差分信號對可利用FPGA器件上充分的LVDS資源。

動態網路 重分配在板級具有增強了的FPGA管腳最佳化引擎,允許工程師充分利用FPGA器件管腳的可重新編程特性,在PCB板極獲得最優的布線方案。Altium Designer系統的統一特性允許在板級完成的管腳交換和FPGA項目的自動同步,減少手動調整處理I/O的耗時。

通常帶有大量管腳的FPGA器件是密集BGA型封裝。這給原型階段的調試帶來很大困難,因為這些器件上的管腳不能直接探測。Altium Designer的LiveDesign開發方法允許工程師在開發中可與基於FPGA的設計直接互動。 Altium Designer 6.0具有改進的JTAG器件

瀏覽器 ,可提供系統中所有JTAG器件的管腳狀態顯示,在調試期間工程師可以實時檢測管腳信號狀態。管腳狀態也可以在源原理圖和PCB版圖動態顯示,‘定位’查看設計文檔內的信號狀態。另外還有Altium Designer的FPGA

虛擬儀器 ,可用來設定並監控FPGA內的信號,給

設計師 提供電路運行完整的

狀態圖 ,以進行系統的邏輯和物理調試。

FPGA系統的線上測試在Altium Designer 7.0中得到改進,提供增強的邏輯分析儀(LAX)

虛擬儀器 。可配置的LAX可監控FPGA內從8位到64位頻寬的匯流排,支持多重信號集的連線。任意信號都可用來觸發輸入或選定為數據源。當可配置的LAX連線到

處理器指令 匯流排時,匯流排數據可顯示為反彙編的代碼指令,代碼相關的問題可方便地在

虛擬儀器 輸出中進行跟蹤。

Altium Designer 7.0中32位的基於FPGA的處理器系統也有更多通用性,支持大量第三方的

軟核 和分立處理器,包括Xilinx MicroBlaze軟處理器、Sharp BlueStreak LH79520(基於ARM720T)和

AMCC PowerPC 405CR分立處理器。這些新器件的支持,對於已經有了8位和32位目標獨立軟處理器支持的Altium Designer設計系統來說,使設計者在使用FPGA進行

嵌入式系統開發 時更加靈活。Altium Designer 7.0提供的包裹連線器核心可幫助設計者定位支持的第三方處理器,同時保留Altium Designer環境的所有設計功能,包括使用Altium Designer

虛擬儀器 方便地連線基於FPGA外設和用LiveDesign進行調試。Altium基於Viper的

編譯器 工具鏈保證所有處理器間的

軟體 兼容性,包裹連線器

核心 提供硬體兼容性。這意味著嵌入式

設計師 無需花費高昂的重新設計工程的代價即可在處理器間進行設計移植。

通過世界範圍內的Altium銷售與支持中心,可以直接購買到Altium Designer 7.0。有關Altium Designers的靈活產品許可證選項定價及相關信息,客戶應與當地的Altium銷售與支持中心聯繫。

Altium Designer 7.0在FPGA開發方面有以下主要特點。

(1)支持不依賴於FPGA廠商即各個廠商通用的數字系統開發。

Altium Designer 7.0支持NanoBoard開發器。NanoBoard開發器標準配置有兩塊可以選擇的FPGA子板,分別為:Altera Cyclone(EP1C12-Q240C7)和Xilinx Spartan IIE(XC2S300E-PQ208C),由於各個廠家不同晶片引腳有些不同,Altium Designer 7.0提供了一個可以定義引腳之間連線的約束檔案(Constrain Files),可以定義不同FPGA與PCB上的引腳對應關係。這樣就可在NanoBoard上將設計好的FPGA邏輯關係換燒到不同的廠家生產的不同系列的FPGA上;就可以依賴於不同廠商的FPGA而進行開發,這一點在實際開發中有很大的好處。

Altium Designer 7.0實現了跨廠家FPGA設計,以前FPGA每一個廠家每一個系列的FPGA設計都需要有專門對應的

下載工具 ,但是現在Altium Designer 7.0克服了這種麻煩,實現了不受晶片廠家型號約束的設計方法。

(2)豐富的原理圖庫,有大量的預綜合元件,包括處理器。

在原理圖

庫里 有大量預綜合的元器件,設計者可以調用到FPGA設計上。包括很多IP模組可以直接調用。有大量免費使用的IP庫可以放心使用。在設計中需要的元件基本上都可以在IP

庫里 找到,包括51核和DSP模組等。這給IP資源復用(IP Reuse)帶來了很大的方便。

IP資源復用(IP Reuse)是指在

積體電路設計 過程中,通過繼承、共享或購買所需的智力產權核心,然後再利用EDA工具進行設計、綜合和驗證,從而加速

流片 設計過程,降低開發風險。IP Reuse已逐漸成為現代

積體電路設計 的重要手段,在日新月異的各種套用需求面前,超大規模

積體電路設計 時代正步入一個IP整合的時代。

Altium Designer 7.0把FPGA設計上升到IP核上來,可以不用以前的HDL語言進行描述。這就降低了FPGA設計的門檻。

(3)在工程的設計和調試階段都支持原理圖導向設計方法。

開發系統提供原理圖設計,在設計階段可以方便模組之間的連線;在調試階段可以很清楚地看出各模組之間的邏輯關係,方便調試。

以FPGA為核心的PLD產品是近幾年積體電路中發展得最快的產品。隨著FPGA性能的高速發展和設計人員自身能力的提高,FPGA將進一步擴大可程式晶片的領地,將複雜專用晶片擠向高端和超複雜套用。隨著處理器以IP的形式嵌入到FPGA中,ASIC和FPGA之間的界限將越來越模糊,未來的某些電路板上可能只有這兩部分電路:模擬部分(包括電源)和一塊FPGA晶片,最多還有一些大容量的存儲器。由於晶片設計的複雜性和產品面市時間對於保證終端市場的成功率至關重要,

設計師 不斷尋求縮短設計周期的方法,以及更有效的設計方式。隨著我們步入系統級晶片時代,利用IP核心和可程式邏輯進行設計復用顯得日趨重要。

虛擬邏輯分析儀、虛擬頻率發生器、頻率計數器、I/O模組、ROM

仿真器 ,為

嵌入式系統 開發提供很大的便利。

虛擬儀器 可以對FPGA裡面的模組或模組與模組之間的邏輯關係進行測試檢驗。

(5)為了方便在FPGA上設計

嵌入式系統 ,Altium Designer 6.0完全綜合了Altium獨特的基於FPGA的現場設計開發板——NanaBoard(Nano-level Breadoard)和一系列的混合到原理圖層的FPGA物理設備。一旦設計被綜合併下載到NanaBoard,設計者就可利用JTAG通信技術對任何核進行通信和控制。

JTAG是Joint Test Action Group的縮寫,是一個國際標準(IEE 1149.1-2001)。是為了測試PCB開發的。利用JTAG可以對晶片進行

邊界掃描 仿真。但是

邊界掃描 仿真器 不能提供真實的路徑,因為JTAG邏輯沒有通向內部地址和數據線單元。一般的JTAG仿真不能看到內部的邏輯情況。而Altium Designer 6.0利用其軟鏈——Nexus鏈,可以使用

虛擬儀器 看清FPGA的內部構造並對其進行調試。在開發調試過程中,可以很方便地看清楚FPGA內部的情況,也可以實時地觀察FPGA發生的情況,而且在Altium Designer 6.0平台上可以看到FPGA裡面燒寫進去的模組。

(6)支持軟硬體並行開發,克服以往

嵌入式系統 軟硬體開發的串列開發形式中的缺點。這種方法必將成為以後FPGA開發的主流方法。

傳統的

嵌入式開發 流程是:系統級設計→PCB板硬體製作→硬體調試→

嵌入式軟體開發 →

軟體調試 →整個系統的軟硬體綜合調試,發現問題後再從流程開始檢查調試。這是一個串列的開發流程,造成的問題是一個系統開發時間過長和調試不方便,發現問題再修改會很麻煩。現在很多

嵌入式開發 存在的問題是,在

硬體開發 階段,那些

軟體開發工程師 無從下手,非得等硬體PCB板做出來才可以基本進行開發,從而浪費了人力和時間。而Altium Designer 7.0提供了一個軟硬體並行的開發方法。當系統級設計完成以後,PCB板

硬體工程師 可以進行製作板子,

嵌入式軟體工程師 可以進行晶片級的

嵌入式軟體開發 ,而到最後調試時出現問題可以很方便地進行軟硬體各自的修改。這種軟硬體並行的開發方法已經在國外慢慢流行起來,在不久的將來將成為

嵌入式系統開發 的主流方法。

9.0版本 Altium Designer Summer 09 v9.1 (強大的電子開發系統)

為適應日新月異的電子設計技術,Altium於2009年7月在全球範圍內推出最新版本Altium Designer Summer 09 (Protel系列

軟體 最新版本)。Summer 09的誕生延續了連續不斷的新特性和新技術的套用過程。

Altium Designer 9.1 已發布,Altium Designer 9.1 不斷通過為高速設計提供各種功能來提高用戶生產力,這些功能包括互動式長度調整和 PCB 層片增強等功能。新增的庫工具和各種新功能將 Altium Designer 提升成為統一的電子產品開發解決方案。這款最新的更新程式將進一步增強您的能力,讓您能夠在更短的“設計到製造”周期內生產更為尖端、更具創新性的電子產品。(Altium Designer完全取代了Protel)

Altium Designer Summer 08新增匯入Allegro PCB(*.brd)的轉檔案功能。

Altium Designer 提供了唯一一款統一的套用方案,其綜合電子產品一體化開發所需的所有必須技術和功能。Altium Designer 在單一設計環境中集成板級和FPGA系統設計、基於FPGA和分立處理器的

嵌入式軟體開發 以及PCB版圖設計、編輯和製造。並集成了現代設計數據管理功能,使得Altium Designer成為電子產品開發的完整解決方案-一個既滿足當前,也滿足未來開發需求的解決方案。

產品功能 Altium Designer 9.1加強了FPGA-PCB協同設計能力

Windows電子設計軟體開發商Altium公司宣布其最新一體化電子產品開發系統Altium Designer 9.1極大地增強了FPGA-PCB協同設計的能力,工程師可以充分利用FPGA作為系統平台,而且簡化大型FPGA與物理PCB平台的集成。

雖然人們早就認識到了FPGA給邏輯開發帶來的好處,但把這些器件集成到PCB設計流程所帶來的挑戰,會使得PCB線路板設計變得十分複雜並導致整體設計時間超長。通常無需考慮PCB版圖即進行FPGA管腳分配,而在大規模可程式器件中使用的密集封裝技術將使得PCB板布線成為極大的挑戰。

Altium Designer打破了FPGA的使用障礙,把硬連線的PCB平台和軟體及軟連線的邏輯開發集成在一起,後者構成的嵌入式智慧型通過在PCB線路板上編程以創建完整的套用。Altium Designer 6.0改進了FPGA級設計和PCB級設計間的集成,開發了很多新功能,與現在的大型可程式器件相結合,它們精簡了產品開發。

FPGA器件的可用性正改變著工程師的系統設計方法――產品中可以添加更更多智慧型並同時縮短設計時間,減少製造成本。”Altium的創始人和CEO Nick Martin說,“Altium Designer 9.1可幫助工程師在嵌入式智慧型級和物理設計級充分利用FPGA提供的好處,系統的統一特性打破了在主流設計中廣泛採用可程式器件的障礙,這樣可以充分利用這些器件的擴展資源,簡化邏輯和物理設計。”

Altium Designer 9.1引入了

動態網路 重分配概念,PCB布線期間可線上交換FPGA管腳。這包括重新分配預先布線的子網和交換連結的差分信號對,差分信號對可利用FPGA器件上充分的LVDS資源。動態網路重分配在板級具有增強了的FPGA管腳最佳化引擎,允許工程師充分利用FPGA器件管腳的可重新編程特性,在PCB板極獲得最優的布線方案。Altium Designer系統的統一特性允許在板級完成的管腳交換和FPGA項目的自動同步,減少手動調整處理I/O的耗時。

通常帶有大量管腳的FPGA器件是密集BGA型封裝。這給原型階段的調試帶來很大困難,因為這些器件上的管腳不能直接探測。Altium Designer的LiveDesign開發方法允許工程師在開發中可與基於FPGA的設計直接互動。 Altium Designer 9.1具有改進的JTAG器件

瀏覽器 ,可提供系統中所有JTAG器件的管腳狀態顯示,在調試期間工程師可以實時檢測管腳信號狀態。管腳狀態也可以在源原理圖和PCB版圖動態顯示,‘定位’查看設計文檔內的信號狀態。另外還有Altium Designer的FPGA虛擬儀器,可用來設定並監控FPGA內的信號,給

設計師 提供電路運行完整的狀態圖,以進行系統的邏輯和物理調試。

FPGA系統的線上測試在Altium Designer 9.1中得到改進,提供增強的邏輯分析儀(LAX)虛擬儀器。可配置的LAX可監控FPGA內從8位到64位頻寬的匯流排,支持多重信號集的連線。任意信號都可用來觸發輸入或選定為數據源。當可配置的LAX連線到處理器指令匯流排時,匯流排數據可顯示為反彙編的代碼指令,代碼相關的問題可方便地在虛擬儀器輸出中進行跟蹤。

Altium Designer 9.1中32位的基於FPGA的處理器系統也有更多通用性,支持大量第三方的軟核和分立處理器,包括Xilinx MicroBlaze軟處理器、Sharp BlueStreak LH79520(基於ARM720T)和AMCC PowerPC 405CR分立處理器。這些新器件的支持,對於已經有了8位和32位目標獨立軟處理器支持的Altium Designer設計系統來說,使設計者在使用FPGA進行

嵌入式系統開發 時更加靈活。Altium Designer 9.1提供的包裹連線器核心可幫助設計者定位支持的第三方處理器,同時保留Altium Designer環境的所有設計功能,包括使用Altium Designer虛擬儀器方便地連線基於FPGA外設和用LiveDesign進行調試。Altium基於Viper的

編譯器 工具鏈保證所有處理器間的軟體兼容性,包裹連線器核心提供硬體兼容性。這意味著嵌入式設計師無需花費高昂的重新設計工程的代價即可在處理器間進行設計移植。

通過世界範圍內的Altium銷售與支持中心,可以直接購買到Altium Designer 9.1。有關Altium Designers的靈活產品許可證選項定價及相關信息,客戶應與當地的Altium銷售與支持中心聯繫。

Altium Designer 9.1在FPGA開發方面有以下主要特點。

(1)支持不依賴於FPGA廠商即各個廠商通用的數字系統開發。

Altium Designer 9.1支持NanoBoard開發器。NanoBoard開發器標準配置有兩塊可以選擇的FPGA子板,分別為:Altera Cyclone(EP1C12-Q240C7)和Xilinx Spartan IIE(XC2S300E-PQ208C),由於各個廠家不同晶片引腳有些不同,Altium Designer 9.1提供了一個可以定義引腳之間連線的約束檔案(Constrain Files),可以定義不同FPGA與PCB上的引腳對應關係。這樣就可在NanoBoard上將設計好的FPGA邏輯關係換燒到不同的廠家生產的不同系列的FPGA上;就可以依賴於不同廠商的FPGA而進行開發,這一點在實際開發中有很大的好處。

Altium Designer 7.0實現了跨廠家FPGA設計,以前FPGA每一個廠家每一個系列的FPGA設計都需要有專門對應的

下載工具 ,但是現在Altium Designer 9.1克服了這種麻煩,實現了不受晶片廠家型號約束的設計方法。

(2)豐富的原理圖庫,有大量的預綜合元件,包括處理器。

在原理圖

庫里 有大量預綜合的元器件,設計者可以調用到FPGA設計上。包括很多IP模組可以直接調用。有大量免費使用的IP庫可以放心使用。在設計中需要的元件基本上都可以在IP庫里找到,包括51核和DSP模組等。這給IP資源復用(IP Reuse)帶來了很大的方便。

IP資源復用(IP Reuse)是指在

積體電路設計 過程中,通過繼承、共享或購買所需的智力產權核心,然後再利用EDA工具進行設計、綜合和驗證,從而加速流片設計過程,降低開發風險。IP Reuse已逐漸成為現代積體電路設計的重要手段,在日新月異的各種套用需求面前,超大規模積體電路設計時代正步入一個IP整合的時代。

Altium Designer 9.1把FPGA設計上升到IP核上來,可以不用以前的HDL語言進行描述。這就降低了FPGA設計的門檻。

(3)在工程的設計和調試階段都支持原理圖導向設計方法。

開發系統提供原理圖設計,在設計階段可以方便模組之間的連線;在調試階段可以很清楚地看出各模組之間的邏輯關係,方便調試。

以FPGA為核心的PLD產品是近幾年積體電路中發展得最快的產品。隨著FPGA性能的高速發展和設計人員自身能力的提高,FPGA將進一步擴大可程式晶片的領地,將複雜專用晶片擠向高端和超複雜套用。隨著處理器以IP的形式嵌入到FPGA中,ASIC和FPGA之間的界限將越來越模糊,未來的某些電路板上可能只有這兩部分電路:模擬部分(包括電源)和一塊FPGA晶片,最多還有一些大容量的存儲器。由於晶片設計的複雜性和產品面市時間對於保證終端市場的成功率至關重要,設計師不斷尋求縮短設計周期的方法,以及更有效的設計方式。隨著我們步入系統級晶片時代,利用IP核心和可程式邏輯進行設計復用顯得日趨重要。

(4)豐富的虛擬儀器。

虛擬邏輯分析儀、虛擬頻率發生器、頻率計數器、I/O模組、ROM仿真器,為嵌入式系統開發提供很大的便利。虛擬儀器可以對FPGA裡面的模組或模組與模組之間的邏輯關係進行測試檢驗。

(5)為了方便在FPGA上設計嵌入式系統,Altium Designer 6.0完全綜合了Altium獨特的基於FPGA的現場設 計

開發板 ——NanaBoard(Nano-level Breadoard)和一系列的混合到原理圖層的FPGA物理設備。一旦設計被綜合併下載到NanaBoard,設計者就可利用JTAG通信技術對任何核進行通信和控制。

JTAG是Joint Test Action Group的縮寫,是一個國際標準(IEE 1149.1-2001)。是為了測試PCB開發的。利用JTAG可以對晶片進行邊界掃描仿真。但是邊界掃描仿真器不能提供真實的路徑,因為JTAG邏輯沒有通向內部地址和數據線單元。一般的JTAG仿真不能看到內部的邏輯情況。而Altium Designer 9.1利用其軟鏈——Nexus鏈,可以使用虛擬儀器看清FPGA的內部構造並對其進行調試。在開發調試過程中,可以很方便地看清楚FPGA內部的情況,也可以實時地觀察FPGA發生的情況,而且在Altium Designer 9.1平台上可以看到FPGA裡面燒寫進去的模組。

(6)支持軟硬體並行開發,克服以往嵌入式系統軟硬體開發的串列開發形式中的缺點。這種方法必將成為以後FPGA開發的主流方法。

傳統的

嵌入式開發 流程是:系統級設計→PCB板硬體製作→硬體調試→嵌入式軟體開發→

軟體調試 →整個系統的軟硬體綜合調試,發現問題後再從流程開始檢查調試。這是一個串列的開發流程,造成的問題是一個系統開發時間過長和調試不方便,發現問題再修改會很麻煩。現在很多嵌入式開發存在的問題是,在硬體開發階段,那些

軟體開發工程師 無從下手,非得等硬體PCB板做出來才可以基本進行開發,從而浪費了人力和時間。而Altium Designer 7.0提供了一個軟硬體並行的開發方法。當系統級設計完成以後,PCB板硬體工程師可以進行製作板子,

嵌入式軟體工程師 可以進行晶片級的嵌入式軟體開發,而到最後調試時出現問題可以很方便地進行軟硬體各自的修改。這種軟硬體並行的開發方法已經在國外慢慢流行起來,在不久的將來將成為嵌入式系統開發的主流方法。