20世紀90年代中期,因使用ASIC實現晶片組受到啟發,萌生應該將完整計算機所有不同的功能塊一次直接集成於一顆矽片上的想法。這種晶片,初始起名叫System on a Chip(SoC),直譯的中文名是系統級晶片。

基本介紹

- 中文名:系統級晶片

- 外文名:System on a Chip

- 萌生時期:20世紀90年代中期

- 設計分類: 軟硬

20世紀90年代中期,因使用ASIC實現晶片組受到啟發,萌生應該將完整計算機所有不同的功能塊一次直接集成於一顆矽片上的想法。這種晶片,初始起名叫System on a Chip(SoC),直譯的中文名是系統級晶片。

SOC設計流程編輯 鎖定 20世紀90年代中期,因使用ASIC實現晶片組受到啟發,萌生應該將完整計算機所有不同的功能塊一次直接集成於一顆矽片上的想法。這種晶片,初始起名叫...

同時它又是一種技術,用以實現從確定系統功能開始,到軟/硬體劃分,並完成設計的整個過程。 中文名 系統級晶片 外文名 System on Chip 縮寫 SoC 別稱 民航SOC...

《系統晶片SoC的設計與測試》是2009年科學出版社出版的圖書,作者是潘中良。本書詳細介紹了系統晶片SoC的設計與測試的關鍵技術和主要方法。...

《PSoC設計指南系列》是2012年出版的圖書,作者是何賓。...... 附贈光碟包含源程式和課件。[1] 參考資料 1. PSoC設計指南系列 .豆瓣讀書[引用日期2012-03-10 1...

第3章ZYNQ 7000 AP SoC設計與開發流程3.1ZYNQ 7000 AP SoC開發流程簡介3.2基於Vivado+SDK的設計與開發3.2.1使用Vivado構建硬體平台3.2.2使用SDK完成軟體開發...

並且從這些開發案例中最大程式地吸取經驗,在最短的時間內具備獨立開發的能力。 ...第14章 GPRS套用系統設計 第15章 嵌入式車載信息系統設計參考資料 1. SoC系統...

1.2.3 典型的FPGA開發流程1.2.4 基於FPGA的SoC設計方法1.2.5 FPGA晶片與設計的性能指標1.3 本章小結第2章 Xilinx FPGA資源簡介...

《Xilinx Zynq SoC與嵌入式Linux設計實戰指南:兼容ARM Cortex》是2014年11月1日清華大學出版社出版的圖書,作者是陸啟帥、陸彥婷、王地。...

《基於聚芯SoC的嵌入式系統設計》本書主要闡述“聚芯SoC”的組成原理及其嵌入式...12.2.4開發VxWorks套用程式12.3Windows CE12.3.1嵌入式作業系統Windows CE...

為方便讀者學習,《Cypress PSoC設計指南系列:混合信號嵌入式設計實驗指南》附贈光碟,包含書中改進的源程式。[1] 參考資料 1. 混合信號嵌入式設計實驗指南 .豆瓣...

1.4 基於FPGA的開發流程 1.4.1 典型FPGA開發流程 1.4.2 FPGA的配置 1.4.3 基於FPGA的SoC設計方法 第2章 硬體描述語言 2.1 VHDL硬體描述語言 2.1.1 程式基本...

《Xilinx Zynq SoC與嵌入式Linux設計實戰指南——兼容ARM Cortex-A9的設計方法》是2014年10月28日清華大學出版社出版的圖書,作者是陸啟帥、陸彥婷、王地。...

2.4ghz超低功耗無線soc晶片nrf24le1是專為超低功耗無線套用設計的單片無線收發...《超低功耗單片無線系統套用入門:基於2.4GHz無線SoC晶片nRF24LE1》提供所有程式...

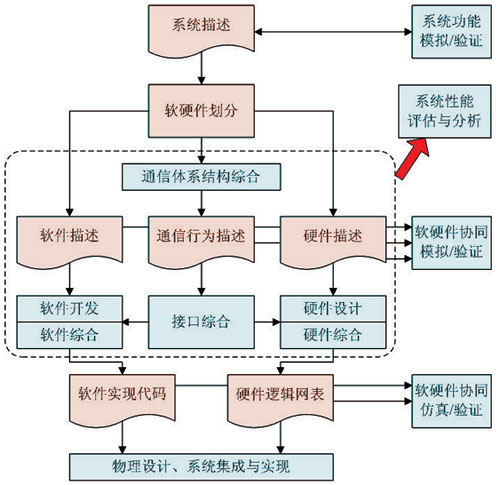

12.3.2 SoC中常用的匯流排標準 (362)12.4 SoC系統的設計流程 (365)12.4.1 SoC系統晶片的系統級設計(366)12.4.2 系統晶片的設計流程 (367) [1] ...