基本介紹

- 中文名:SSL加速卡

- 外文名:SSL acceleration card

- 前身:安全套接層(SSL)的硬體加速器

- 用途:減輕處理器過多參與傳輸層協定

- 學科:密碼學

- 領域:密碼學

導言,SSL淺析,第一代加速器,第二代加速器,部署方法,加速器的實現,結論,

導言

網路信息安全已經成為電子商務和網路信息業發展的一個瓶頸,安全套接層(SSL)協定能較好地解決安全處理問題,而SSL加速器有效地提高了網路安全處理的性能。第一代和第二代SSL加速器提高了安全處理性能,但卻不能滿足系統擴展要求,即將推出的第三代SSL加速器集成度將更高,並採用新一代匯流排技術實現更高的安全處理性能。

如何實現網際網路的安全性?這個簡單的問題一直困繞著網路的發展。隨著網上信用卡交易的普及與交易量的快速增長,黑客變得更為狡猾,網路互連的安全性已變得越來越重要。

那么怎樣才能提供最好的安全性呢?利用安全套接層(SSL)協定是個較好的解決方法。

由Netscape開發的SSL已在網路業得到廣泛的套用,它極大地促進了安全電子商務的發展,使各個公司能安全地開展基於網路的業務。但是,隨著網路設備速度的加快需要大量計算,而速度緩慢的SSL正日益顯示出不足之處,它無法以線速度(wire rate)進行安全性處理,而線速度正是當今系統設計工程師所追求的目標。

為了應對這種挑戰,通信設計工程師們已開發出加速器來加快SSL處理。但是這些解決方案仍然不能滿足當今網際網路設備的要求。

對於大多數通信業務來說,在系統設計中嵌入SSL技術,採用協定加速器而不是僅僅採用密碼加速器IC方案才是這個問題的解決方法。在這種想法的推動下,提出了第二代SSL加速器與新的SSL加速技術,下面將詳細討論並分析這些方案對今後系統設計流程的影響。

SSL淺析

握手階段也需要不少功能支持,如安全隨機數的產生、RSA解密,以及採用一系列散列函式產生主秘(master secret)與密鑰數據。記錄層將位元組數據流處理成記錄塊,並採用密碼套件(cipher suite,一對加密與散列算法)對其進行加密與認證。在記錄層階段採用對稱密碼對用戶數據加密,並採用某種散列算法對數據進行認證, 該算法是基於握手階段產生的密鑰。

為了解決這個問題,設計工程師們開發出第一代SSL加速器。這些加速器試圖將SSL握手部分的負載RSA解密移出網路伺服器,讓控制處理器來處理餘下的握手函式(用於密鑰創建的散列函式)以及記錄層處理函式(大量的加密與認證)。

一個典型的第一代SSL加速器包含一個帶很多SSL加速晶片的PCI板,每秒最多能處理200個解密算法,這比最初的SSL產品(不帶加速器)快30到40倍。

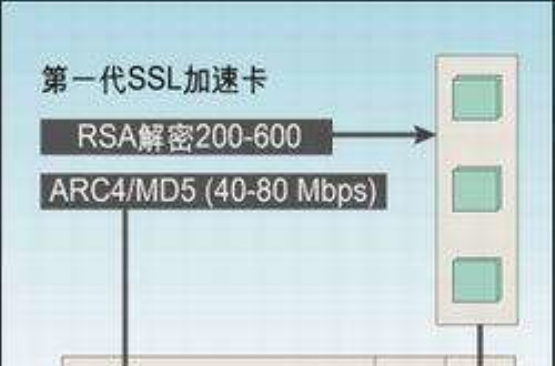

第一代加速器

第一代SSL加速器每秒能處理600個RSA解密算法。在全速運行條件下,一個每秒運行600個RSA解密算法的系統需要約85Mbps的加密處理能力,對於RC4/MD5密碼套件而言,其負載將占1GHz奔騰III CPU處理能力16%,而3DES/SHA-1密碼套件則需要144%的CPU處理能力。

當RSA解密功能由SSL加速器實現後,CPU就不會過載,並有足夠能力進行TCP/IP處理與記錄層處理。當兩個SSL功能單元之間建立平衡後,網路伺服器就能高速傳送加密的業務數據,雖然不能接近線速度,但遠遠好於不採用SSL加速器的性能。但是,可擴展性是第一代加速器所不能實現的性能。

為了在系統架構中增加更多的SSL加速器,設計工程師必須增加更多的伺服器卡。對於設計工程師與運營商來說,顯然是件很困難的事。由於每塊卡的價格要幾千美元,再加上上萬美元的額外伺服器費用,使得這種解決方案的成本迅速攀升。

從性能角度看,由於CPU仍要從事大量的加密工作,加速卡數量的增加所提高的效率非常有限。CPU既要執行越來越多的TCP/IP處理,同時又要負責加密計算,因此第一代系統的可擴展性極其有限。

由於上述問題的存在,設計工程師只好又重新尋求新的加速技術,最後他們用單個晶片開發出完整的SSL加速產品。

第二代加速器

雖然第一代產品通過SSL加速器處理RSA解密功能來提高性能,但系統級的總體性能仍不理想,而採用IC形式推出的第二代產品能增加每秒握手次數。

第二代SSL加速器設計工程師很快發現需要在握手與加密計算的吞吐量(異步與同步操作)之間取得均衡,一味地提高每秒內的握手次數只會產生新的瓶頸。隨著密碼套件處理量的增加,CPU資源很快就會耗盡,也削弱了對TCP/IP的處理能力。

例如,即使主處理器採用1GHz奔騰III處理器,一個每秒能傳送2,000次RSA握手的純RSA解密器也會給主處理器帶來沉重的負載。對於RC4-MD5密碼套件來說這些負載將消耗55%的CPU資源,而對於需要大量計算的3DES-SHA1密碼套件來說可能需要近500%的CPU資源。

迅速增加握手次數將使瓶頸後移到CPU,這時,只要記錄層存在大量加密處理就將產生系統阻塞。

為了避免這種瓶頸問題,晶片與系統設計工程師開始尋求用IC來實現SSL加速。這些通常被稱為網路安全處理器的IC會卸載主處理器的握手函式(RSA解密與密鑰生成)以及記錄層的大量加密與認證函式,使CPU能騰出更多的資源來執行包處理,從而提升系統總體性能。

為了進一步方便集成,製造商還需將安全處理器置於PCI板上。因此,製造商需要解決一般OEM廠商都會遇到的I/O困難,尤其在將這些IC置入PCI系統架構的時候。

部署方法

在你的基礎設施中的一些WAN最佳化設備上安裝和維護證書和密鑰。當證書到期時,僅更新伺服器上的證書是不夠的,你需要更新一個或多個WAN最佳化設備上的證書。

根據證書供應商的不同,除了伺服器證書外,你可能還需要安裝中間證書,以形成完整的證書鏈。最常見的中間證書可能已經被預先安裝在你的WAN最佳化設備的證書存儲中,但有些供應商可能沒有提供。

企業對承載證書的設備制定了物理安全政策,你需要讓伺服器端WAN最佳化設備遵守這項政策。如果沒有明確的政策,企業最好的做法是,確保存儲證書的設備在物理上是安全的。這種方法的好處是,並不需要為了Riverbed改變分支機構的物理安全要求,因為遠程WAN加速設備不會存儲證書或密鑰。

監控你的設備是如何有效地最佳化HTTPS連線,正如你監控HTTP連線一樣。Riverbed Steelhead具有HTTP自動調諧算法,該算法能夠確定對給定HTTP會話應該採用何種最佳化。這種調整可能或者可能不是你的套用的理想選擇,所以你應該對這種算法進行審查以確保你的套用為WAN傳輸進行了最佳化,儘可能完全不影回響用的行為。

加速器的實現

在目前典型的IP網路結構中,業務是通過L4/L7智慧型負載均衡交換機進入數據中心。輸入的網路客戶機請求將被分配到後端的若干網路伺服器或網路緩衝器中。L7套用數據在送入網路伺服器之前要做一定的解析。由於SSL要加密L4以上的所有數據,在數據被完全解密前無法執行對套用層數據的智慧型內容交換。

在目前的架構中,SSL加速功能很可能以單個PCI插卡的形式配置於SSL設備和網路伺服器中。交換機將SSL業務直接轉移到該設備中並在那裡執行解密,然後設備將未加密的業務數據送回到交換機,這些數據與解密的套用數據進行負載均衡。

緊密集成的下一步是將SSL加速器直接集成到L4/L7交換機中。要做到這一點,網路安全處理器可以附加在代理卡上(而不是一塊簡單的PCI板),在代理卡上還應安裝運行SSL代理程式的控制處理器。這種設備基本上能代替加速設備,可直接集到進交換機連線埠。

在當前架構中,SSL加速功能很可能以單個SSL插卡的形式配置在網路伺服器中。從發展的角度看,某些情況下的SSL加速器配置可以移植到用戶卡,因為加速系統會更直接地集成到總體系統設計中。