基本介紹

- 中文名:CPU匯流排

- 外文名:CPU bus

- 別名:FSB

CPU匯流排,是PC系統中最快的匯流排,也是晶片組與主機板的核心。這條匯流排主要由CPU使用,用來與高速快取、主存和北橋(或MCH)之間傳送信息。綜述CPU匯流排可看到的PC系統中使用的CPU匯流排工作頻率為66、100、133或2...

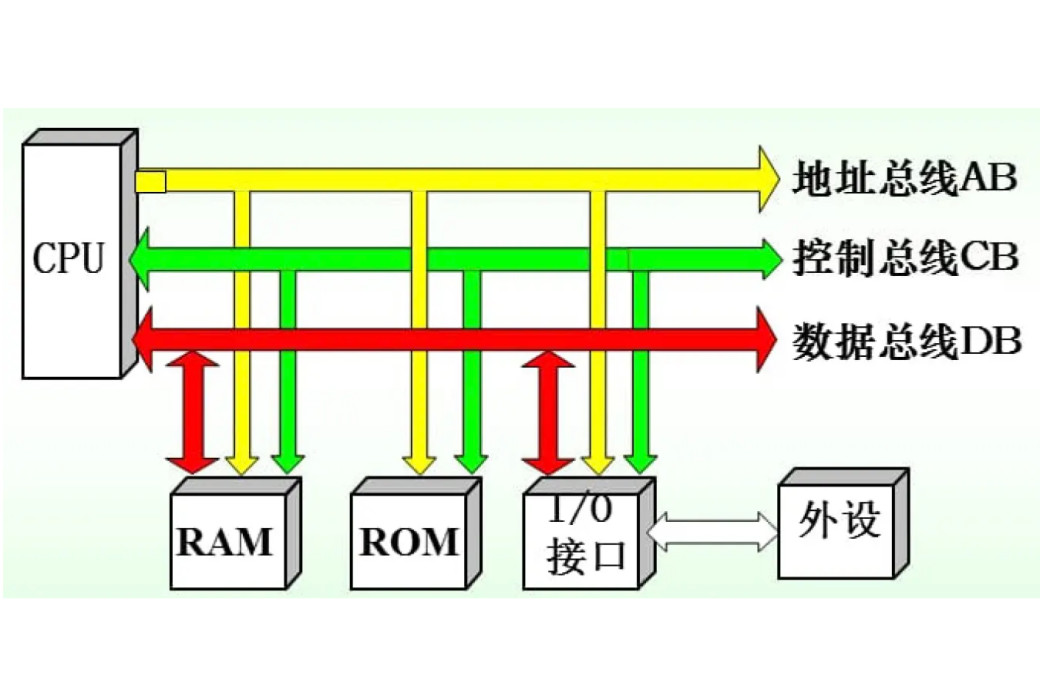

匯流排是一種內部結構,它是cpu、記憶體、輸入、輸出設備傳遞信息的公用通道,主機的各個部件通過匯流排相連線,外部設備通過相應的接口電路再與匯流排相連線,從而形成了計算機硬體系統。在計算機系統中,各個部件之間傳送信息的公共通路叫匯流排,微型...

FSB(匯流排)是計算機的組件之一,指的是CPU和北橋晶片間匯流排的速度,更實質性的表示了CPU和外界數據傳輸的速度。外頻是CPU乃至整個計算機系統的基準頻率,單位是MHz(兆赫茲)。在早期的電腦中,記憶體與主機板之間的同步運行的速度等於外頻,...

所謂匯流排技術就是CPU與外設的通訊標準,是一種很具體的通訊協定,包括很複雜的技術指標和參數,只要在設計和生產製造中遵守這些協定,就能很好地兼容各種外設,充分發揮計算機系統的性能。描述匯流排技術的性能指標主要有:匯流排寬度:傳輸線路的...

⑴ CPU匯流排:包括CPU地址線(CAB),CPU數據線(CDB)和CPU控制線(CCB),其用來連線CPU和控制晶片。⑵ 存儲器匯流排:包括存儲器地址線(MAB)、存儲器數據線(MDB)和存儲器控制線(MCD),用來連線記憶體控制器(北橋)和記憶體。⑶ ...

外部數據匯流排是中央處理器CPU(Central Processing Unit)的一部分,是CPU與外部數據傳輸的通道。外部數據匯流排一次可傳輸二進制數據的位數越大,CPU與外部交換數據的能力越強。基本介紹 CPU主要由三個部分組成:算術邏輯單元(ALU,Arithmetic ...

內部匯流排是一種內部結構,是cpu、記憶體、輸入、輸出設備傳遞信息的公用通道。定義 內部匯流排,將處理器的所有結構單元內部相連。它的寬度可以是8、16、32、64或128位。如在CPU內部,暫存器之間和算術邏輯部件ALU與控制部件之間傳輸數據所用...

新一代計算機採用高配置處理器作為控制中心,CPU在結構功能方面有了很大的提升空間。中央處理器以運算器、控制器為主要裝置,逐漸擴散為邏輯運算、暫存控制、程式編碼、信號收發等多項功能。這些都加快了CPU調控性能的最佳化升級。CPU匯流排 CPU...

匯流排介紹 播報 編輯 主機板圖片前端匯流排是處理器與主機板北橋晶片或記憶體控制集線器之間的數據通道,其頻率高低直接影響CPU訪問記憶體的速度;BIOS可看作是一個記憶電腦相關設定的軟體,可以通過它調整相關設定。BIOS存儲於板卡上一塊晶片中,這塊晶片的...

它的推出為微機系統匯流排體系結構的革新奠定了基礎。該匯流排系統考慮到CPU與主存和Cache的直接相連,通常把這部分匯流排稱為CPU匯流排或主匯流排,其他設備通過VL匯流排與CPU匯流排相連,所以VL匯流排被稱為局部匯流排。PCI匯流排 PCI(Peripheral Component ...

存儲匯流排由許多條並行排列的傳輸數據的線路組成,細分為三組:數據匯流排(用於傳遞數據);地址匯流排(用於傳遞主存儲器的地址);控制匯流排(用於各種內部控制指令的傳遞)。CPU和主存儲器之間的信息交換是通過數據匯流排和地址匯流排進行的。當...

AGP 匯流排 (Accelerated Graphics Port)PCI 匯流排是獨立於CPU 的系統匯流排,可將顯示卡、音效卡、網卡、硬碟控制器等高速的外圍設備直接掛在CPU 匯流排上,打破了瓶頸,使得CPU 的性能得到充分的發揮。可惜的是,由於PCI 匯流排只有133MB/s 的...

匯流排架構指的是自己其內部的通用線路。眾所周知,CPU工作時需要與外圍硬體設備進行數據、命令的交換,如果每種設備都分別引入一組線路直接與CPU相連,則可能導致系統線路雜亂無章,甚至不可能實現。為了簡化硬體電路和系統結構,人們引入了一...

地址匯流排是專門用來傳送地址的。在設計過程中,見得最多的應該是從CPU地址匯流排來選用外部存儲器的存儲地址。地址匯流排的位數往往決定了存儲器存儲空間的大小,比如地址匯流排為16位,則其最大可存儲空間為216(64KB)。數據匯流排是用於傳送數據...

它的推出為微機系統匯流排體系結構的革新奠定了基礎。該匯流排系統考慮到CPU與主存和Cache 的直接相連,通常把這部分匯流排稱為CPU匯流排或主匯流排,其他設備通過VL匯流排與CPU匯流排相連,所以VL匯流排被稱為局部匯流排。它定義了32位數據線,且可通過擴展...

⑤8位ISA匯流排在存儲器讀/寫周期可用到20位地址,而16位ISA匯流排在存儲器讀寫周期中可使用24位地址。但由於受I/O指令的限制。8位和16位ISA匯流排的I/0讀/寫周期都只能使用低16位地址。⑥BALE在CPU匯流排周期的T1期間有效,它的基本...

ISA(Industry Standard Architecture)工業標準體系結構匯流排.EISA(Extension Industry Standard Architecture)擴展標準體系結構匯流排.MCA(Micro Channel)微通道匯流排.此外,為了解決CPU與高速外設之間傳輸速度慢的"瓶頸"問題,出現了兩種局部匯流排,它們...

我們通常所說的匯流排大多是指片外匯流排。有的資料上也把片內匯流排叫做內部匯流排或內匯流排(Internal Bus),把片外匯流排叫做外部匯流排或外匯流排(External Bus)。CPU匯流排、系統匯流排和外設匯流排 CPU匯流排是從CPU引腳上引出的連線線,用來實現CPU與外圍...

PCI匯流排是32位同步復用匯流排。其地址和數據線引腳是AD31~AD0。PCI的工作頻率為33MHz。PCI匯流排結構 PCI匯流排是一種樹型結構,並且獨立於CPU匯流排,可以和CPU匯流排並行操作。PCI匯流排上可以掛接PCI設備和PCI橋片,PCI匯流排上只允許有一個PCI...

HT是HyperTransport的簡稱。HyperTransport本質是一種為主機板上的積體電路互連而設計的端到端匯流排技術,目的是加快晶片間的數據傳輸速度。HyperTransport技術在AMD平台上使用後,是指AMD CPU到主機板晶片之間的連線匯流排(如果主機板晶片組是南北橋架構...

通常把CPU通過匯流排對微處理器外部(存貯器或I/O接口)進行一次訪問所需時間稱為一個匯流排周期。一個匯流排周期一般包含4個時鐘周期,這4個時鐘周期分別稱4個狀態即T1狀態、T2狀態、T3狀態和T4狀態。二、匯流排時序 所謂匯流排時序,即CPU...

前端匯流排是CPU和外界交換數據的最主要通道,因此前端匯流排的數據傳輸能力對計算機整體性能作用很大,如果沒足夠快的前端匯流排,再強的CPU也不能明顯提高計算機整體速度。數據傳輸最大頻寬取決於所有同時傳輸的數據的寬度和傳輸頻率,即數據頻寬=...

在機器視覺領域中廣泛使用的匯流排接口主要是基於PCI的各種匯流排:PCI、PCI-X、PCI EXPRESS。PCI匯流排是獨立於CPU的系統匯流排,採用了獨特的中間緩衝器設計,可將高速的外圍設備直接掛在CPU匯流排上,打破了瓶頸,使得CPU的性能得到充分的發揮。圖...

CPU的根本任務就是執行指令,對計算機來說最終都是一串由“0”和“1”組成的序列。CPU從邏輯上可以劃分成3個模組,分別是控制單元、運算單元和存儲單元,這三部分由CPU內部匯流排連線起來。如下所示:控制單元 控制單元是整個CPU的指揮控制...