分類 隨著計算機技術發展,記憶體控制器分為傳統型和整合型兩種。

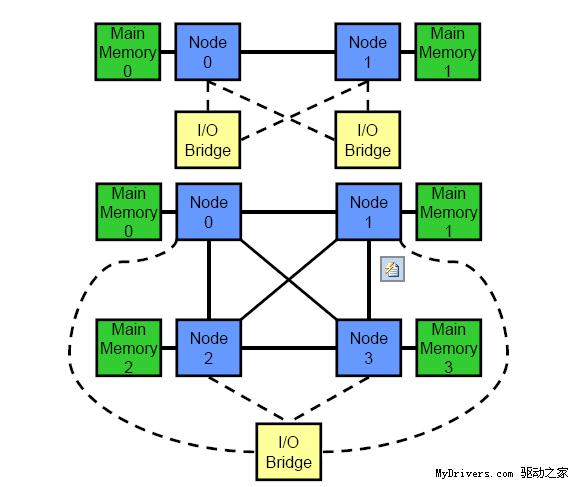

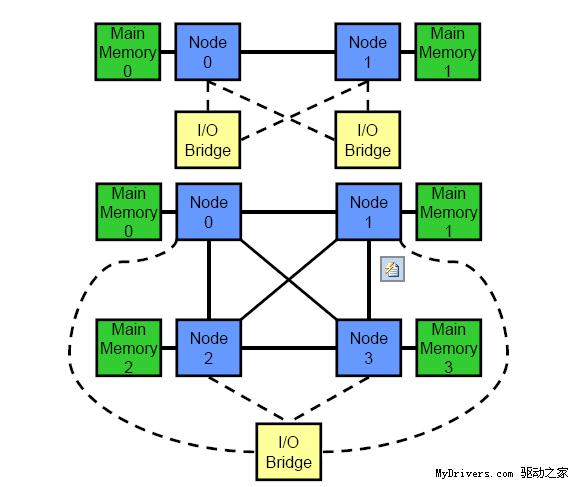

記憶體控制器 傳統型 傳統計算機系統其記憶體控制器位於主機板晶片組

北橋晶片 內部,

CPU 要與記憶體進行數據交換,需要經過“

CPU-- 北橋 --記憶體--北橋--CPU ”5個步驟,在該模式下數據經由多級傳輸,數據延遲顯然比較大從而影響計算機系統整體性能;

整合型 集成記憶體控制器,就是在CPU的基板上內置一個記憶體控制器,先說說沒有記憶體控制器時系統是如何工作的。26個數據A~Z,要傳送到CPU,這時候CPU就向

北橋 發出指令(因為記憶體控制器是集成在北橋上,所以說要經過北橋),記憶體通過記憶體控制器接受到了指令,這個指令就是把記憶體上b單元的A~Z

數據傳送 到CPU,記憶體這個時候開始取數據,也就是平常所說的定址。當記憶體找到了這個數據,而這26個數據每個數據為500MB,所有數據總和就約為12GB,假設記憶體為雙通道R2 800,數據傳輸率就為800MHZ乘以128BIT除以8比特每位元組=12GB每秒,通過分析,認為只需一秒就能傳送到CPU,此時的數據在一秒的時間內只傳送到了

北橋 ,記憶體控制器在北橋,在北橋的數據如何傳送到CPU呢,這就要通過FSB前端匯流排了,假設FSB的頻率為800MHZ,那么數據傳輸率就為800MHZ乘以64BIT除以8

比特每秒 =6.4GB每秒,從北橋到CPU要2秒,所以

數據傳送 到CPU的總時間為3秒,接下來再來看看CPU集成記憶體控制器的時候系統是如何工作的;數據從記憶體傳輸到控制器後,同樣為1秒,所不同的是這個時候不用再通過慢吞吞的前端匯流排了,CPU直接從記憶體控制器讀取數據就行了,因為記憶體控制器在CPU的門口,打個比方,一件東西在你門口的時候,大家就可以直接拿了,就是這個原理,算了一下,集成記憶體控制器的CPU讀取12GB的數據是才用了1秒的時間,所以大大節省了運算時間,也充分發揮了CPU的性能。

最後總結一下:CPU沒有記憶體控制器時,數據以記憶體控制器---

北橋 ----CPU的方式傳輸;有記憶體控制器時,數據以記憶體控制器------CPU的方式傳輸,一步到位。

工作原理 CPU內部整合記憶體控制器的優點,就是可以有效控制記憶體控制器工作在與CPU核心同樣的頻率上,而且由於記憶體與CPU之間的數據交換無需經過北橋,可以有效降低傳輸延遲。打個比方,這就如同將貨物倉庫直接搬到了加工車間旁邊,大大減少原材料和製成品在貨物倉庫與加工車間之間往返運輸所需要的時間,極大地提高了生產效率。這樣一來系統的整體性能也得到了提升。

記憶體頻率 和CPU一樣,記憶體也有自己的工作頻率,頻率以MHz為單位記憶體主頻越高在一定程度上代表著記憶體所能達到的速度越快。記憶體主頻決定著該記憶體最高能在什麼樣的頻率正常工作。最為主流的記憶體類型為DDR3和DDR4,作為DDR2的替代者,DDR3記憶體頻率已經達到了1600MHz,而DDR4的記憶體頻率則為2133MHz。

記憶體容量 記憶體的容量不但是影響記憶體價格的因素,同時也是影響到整機系統性能的因素。過去Windows XP平台,512M的記憶體還是主流,1GB已經是大容量;64位系統開始普及,

Windows Vista 、

Windows 7 、Windows10越來越多人使用,沒有2GB左右的記憶體都不一定能保證操作的流暢度。單根記憶體的容量主要有1GB、2GB、4GB,最高已經達到單根8GB和單根16GB。

工作電壓 記憶體正常工作所需要的電壓值,不同類型的記憶體電壓也不同,但各自均有自己的規格,超出其規格,容易造成記憶體損壞。DDR2記憶體的工作電壓一般在1.8V左右,而DDR3記憶體則在1.5V或1.35V左右。為了超頻,記憶體需要工作在高於標準的電壓值下,具體到每種品牌、每種型號的記憶體,則要看廠家了。只要在允許的範圍內浮動,略微提高記憶體電壓,有利於記憶體超頻,但是同時發熱量大大增加,因此有損壞硬體的風險。

時序參數 tCL : CAS Latency Control(tCL)

一般我們在查閱記憶體的時序參數時,如“8-8-8-24”這一類的數字序列,上述數字序列分別對應的參數是“CL-tRCD-tRP-tRAS”。這個第一個“8”就是第1個參數,即CL參數。

CAS Latency Control(也被描述為tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“記憶體讀寫操作前列地址控制器的潛伏時間”。CAS控制從接受一個指令到執行指令之間的時間。因為CAS主要控制十六進制的地址,或者說是記憶體矩陣中的列地址,所以它是最為重要的參數,在穩定的前提下應該儘可能設低。

記憶體是根據行和列定址的,當請求觸發後,最初是tRAS(Activeto Precharge Delay),預充電後,記憶體才真正開始初始化RAS。一旦tRAS激活後,RAS(Row Address Strobe )開始進行需要數據的定址。首先是行地址,然後初始化tRCD,周期結束,接著通過CAS訪問所需數據的精確十六進制地址。期間從CAS開始到CAS結束就是CAS延遲。所以CAS是找到數據的最後一個步驟,也是記憶體參數中最重要的。

這個參數控制記憶體接收到一條數據讀取指令後要等待多少個時鐘周期才實際執行該指令。同時該參數也決定了在一次記憶體突發傳送過程中完成第一部分傳送所需要的時鐘周期數。這個參數越小,則記憶體的速度越快。必須注意部分記憶體不能運行在較低的延遲,可能會丟失數據。而且提高延遲能使記憶體運行在更高的頻率,所以需要對記憶體超頻時,應該試著提高CAS延遲。

該參數對記憶體性能的影響最大,在保證系統穩定性的前提下,CAS值越低,則會導致更快的記憶體讀寫操作。

tRCD : RAS to CAS Delay

該值就是“8-8-8-24”記憶體時序參數中的第2個參數,即第2個“8”。RAS to CAS Delay(也被描述為:tRCD、RAS to CAS Delay、Active to CMD),表示"行定址到列定址延遲時間",數值越小,性能越好。對記憶體進行讀、寫或刷新操作時,需要在這兩種脈衝信號之間插入延遲時鐘周期。在JEDEC規範中,它是排在第二的參數,降低此延時,可以提高系統性能。如果你的記憶體的超頻性能不佳,則可將此值設為記憶體的默認值或嘗試提高tRCD值。

tRP : Row Precharge Timing(tRP)

該值就是“8-8-8-24”記憶體時序參數中的第3個參數,即第3個“8”。Row Precharge Timing (也被描述為:tRP、RAS Precharge、Precharge to active),表示"記憶體行地址控制器預充電時間",預充電參數越小則記憶體讀寫速度就越快。tRP用來設定在另一行能被激活之前,RAS需要的充電時間。

tRAS : Min RAS Active Timing

該值就是該值就是“8-8-8-24”記憶體時序參數中的最後一個參數,即“24”。Min RAS Active Time (也被描述為:tRAS、Active to Precharge Delay、Row Active Time、Precharge Wait State、Row Active Delay、Row Precharge Delay、RAS Active Time),表示“記憶體行有效至預充電的最短周期”,調整這個參數需要結合具體情況而定,一般我們最好設在24~30之間。這個參數要根據實際情況而定,並不是說越大或越小就越好。

如果tRAS的周期太長,系統會因為無謂的等待而降低性能。降低tRAS周期,則會導致已被激活的行地址會更早的進入非激活狀態。如果tRAS的周期太短,則可能因缺乏足夠的時間而無法完成數據的突發傳輸,這樣會引發丟失數據或損壞數據。該值一般設定為CAS latency + tRCD + 2個時鐘周期。

對於大多數人來說,記憶體這個小硬體選好容量和

頻率 ,然後插上

主機板 用上就行了,對它的很多小參數完全不在意。所以,行業廠商也會提供比較傻瓜式的讀取記憶體SPD晶片的參數信息,自動設定各項小參,簡單好用;更有簡單的超頻設定——

XMP 技術,讓普通用戶也能簡單地享受超頻增值的樂趣。

發展過程 發展方向 把記憶體控制器整合到CPU內部顯然是今後的發展方向,而且其技術也一定越來越完善。

AMD的在K8系列CPU及其之後的產品(包括

Socket 754 /939/940等接口的各種

處理器 ),CPU的內部則整合了記憶體控制器,CPU和記憶體之間的數據交換過程簡化為“CPU--記憶體--CPU”三個步驟,省略兩個步驟,和傳統的記憶體控制器方案相比顯然具有更低的數據延遲,有助於提高計算機系統的整體性能。

發展歷程 Intel在

45納米 Penryn系列之後推出全新微架構,代號

Nehalem ,屆時將看到多項全新技術,其中整合的記憶體控制器無疑非常吸引人。AMD一直在自身的

處理器 內集成記憶體控制器,因而取得了很好的記憶體性能,但也導致每次記憶體規格升級都必須更新處理器接口;相反,Intel堅持把記憶體控制器放在

北橋晶片 里,同時對處理器本身的調整更多地依賴於快取容量的增減。雖然Intel曾經列舉了多項理由,表示不集成記憶體控制器好處多多,但隨著形勢的發展變化,Intel自然也不會一條路走到黑,到了下一代新架構。記憶體控制器就將與圖形核心一起走入Intel處理器的內部。顯然,Intel所做的不僅僅是簡單集成。

Nehalem架構下的原生 四核心處理器 Bloomfield將具備 三通道 DDR3記憶體控制器,支持DDR3-1600規格,可提供38.4GB/s的巨大 頻寬 ,相比雙通道20GB/s左右幾乎翻了一番,同時內建的圖形核心也能因此獲得更好的性能表現,尤其是在3D遊戲裡。不過,

Nehalem 下的雙核心

處理器 還會只配備

雙通道記憶體 控制器,以拉開市場差距。

運算 到了DDR2時代的

AM2處理器 ,雖然核心方面同樣內置了DDR2的記憶體控制器, 但與過去的Socket 939接口不同的是,它所支持的記憶體頻率被更新至DDR2-800的水平。CPU主頻再也不能與CPU的倍頻直接相除,而是除以倍頻數二分之一後的整數(不能被整除取整數部分再加1).以4600+和4800+ CPU為例:

即記憶體運行頻率=(CPU主頻÷倍頻/2)×2

X2 4800+ ,主頻為2.5GHz,倍頻為12.5。所以記憶體的除頻數為7,此時記憶體運行的頻率 =(2500M÷7)×2=714M

X2 4600+主頻為2.4GHz,

倍頻 為12 . 所以記憶體的除頻數為6,此時記憶體運行的頻率 = (2400M÷6)×2=800M

4600+完美的支持DDR2-800

簡單的來說就是,如果CPU的主頻倘若不能被400整除的話,就說明該AM2

處理器 在默認的頻率下無法運行在DDR2-800的模式下。

控制器 CPU記憶體集成記憶體控制器優點 CPU記憶體集成記憶體控制器有很多優點 比較突出的是三點:

第一CPU內部整合記憶體控制器

傳統的計算機系統的記憶體控制器位於主機板晶片組的

北橋晶片 內部,CPU是要和記憶體進行

數據交換 ,是需要經過“CPU--北橋--記憶體--北橋--CPU”五個步驟,在此模式中數據經由多級傳輸,數據延遲顯然較大從而影響計算機系統的整體性能;而

AMD 的K8系列CPU(包括Socket754/939/940等接口各種

處理器 )內部則整合記憶體控制器,CPU與記憶體之間的數據交換過程就簡化成“CPU--記憶體--CPU”3個步驟,省略了2個步驟,與傳統記憶體控制器方案相比顯然具有更低數據延遲,這有助提高計算機系統的整體性能。

第二記憶體控制器同頻於CPU頻工作

CPU內部集成記憶體控制器可以使記憶體控制器同頻於CPU頻工作(CPU

工作頻率 一般都在2G以上) ,而

北橋 的記憶體控制器一般就要大大低於CPU工作頻率,系統延時就更加少。

第三CPU內部集成記憶體控制器

CPU內部集成記憶體控制器,由於記憶體數據不經過北橋有效的降低了北橋的工作壓力,為北橋減低可負擔。

CPU內部集成記憶體控制器是K8 ,CPU的一大設計亮點,雖然在總體性能上酷睿遠遠超過K8,但是在記憶體性能上酷睿相對於K8來說還是望塵莫及。

整合記憶體控制器的特徵

CPU內部

整合記憶體控制器 的優點,是可以有效控制記憶體控制器工作在和

CPU核心 同樣的頻率上,而且因為記憶體與CPU之間的數據交換無需經過北橋,能有效降低

傳輸延遲 。打個比方,這就如同將貨物倉庫直接搬到加工車間旁邊,大大減少原材料和製成品在貨物倉庫和加工車間之間往返運輸所需要的時間,極大地提高生產效率。這樣一來系統的整體性能也得到提升。

CPU內部整合記憶體控制器最大缺點,就是對記憶體適應性比較差,靈活性比較差,只能使用特定類型記憶體,而且對記憶體的容量與速度也有限制,要支持新類型的記憶體、一定更新CPU內部整合的記憶體控制器,也就是說一定更換新的CPU;比如AMD的K8系列CPU、就只能支持

DDR ,而不能支持更高速DDR2。而傳統方案的記憶體控制器因為位於主機板晶片組的

北橋晶片 內部,就沒有這方面問題,只需要更換主機板,甚至不更換主機板也可以使用不同類型的記憶體,比如Intel

Pentium 4 系列CPU,假如原來配的是不支持

DDR2 的主機板,那么只要更換一塊支持DDR2的主機板就可以使用DDR2,如果配的是同時支持DDR和DDR2主機板,則不必更換主機板就可以直接使用DDR2。

通常,對於整個PC系統來說,我們往往只關注於CPU的主頻、系統前端匯流排的頻率、記憶體的

工作頻率 和它們之間的

匯流排頻寬 等,但是

記憶體延遲 對系統性能的影響也相當大。

那么,什麼是記憶體延遲呢?通俗來講,系統要對某些數據進行操作時,會由CPU發出指令,存儲在硬碟里的數據將傳送到記憶體里,由記憶體轉送給CPU。但是通常記憶體控制器是集成在主機板晶片組的

北橋晶片 內,數據經由多級傳輸,往往會產生一定延遲。因而CPU發出指令後並不能及時獲得數據,對其並進行處理。記憶體延遲對系統性能有著重要的影響,記憶體系統的總體延遲大約為120~150ns,在這段時間內CPU所能做的只有等待。因而,儘可能的降低記憶體延遲無疑對系統性能的提升有著莫大的幫助。傳統的

處理器 要和記憶體進行數據交換,需要經過“CPU-

北橋 -DIMM-北橋-CPU”。而處理器核心

整合記憶體控制器 ,進程就會簡化為“CPU-DIMM-CPU”,省略了兩個步驟。

這恐怕是AMD

64位處理器 在32位套用環境下也能表現出強勁性能的主要原因之一。處理器內部集成記憶體控制器的好處,就是可以有效控制記憶體控制器工作在與

處理器核心 同樣的頻率上,而且由於記憶體與處理器之間的數據傳輸無需經過北橋,能有效降低傳輸延遲。打個比方,這就如同將貨物倉庫直接搬至加工車間旁邊,大大減少了原材料/製成品在貨物倉庫和加工車間之間往返運輸所需時間,極大地提高了生產效率。這樣一來系統的整體性能也得到了提升。在實際測試中,

Athlon 64 等待記憶體數據的

時鐘周期 比

Athlon XP 減少了30~40%,帶來系統整體性能的提升高達25~30%。

整合記憶體控制器 雖然可以達到高寬頻和低延遲,但是其升級換代不就成了一個大問題嗎?通常,如果一種新的記憶體標準推出,

晶片組 廠商可以直接開發支持新記憶體的晶片組來支持。而記憶體控制器整合到

處理器核心 中,就造成升級的困難,因為改一下支持記憶體的規格就需要改核心。但就情況來看,這個疑慮似乎可以打消了。

發展方向:

將記憶體控制器整合到CPU內部顯然是今後的發展方向,而且其技術也會越來越完善。以後Intel也推出整合記憶體控制器的CPU的產品。

優缺點 優點 1.CPU內部整合記憶體控制器的優點,就是可以有效控制記憶體控制器工作在與CPU核心同樣的頻率上,而且由於記憶體與CPU之間的數據交換無需經過北橋,可以有效降低傳輸延遲。這就如同將貨物倉庫直接搬到了加工車間旁邊,大大減少了原材料和製成品在貨物倉庫和加工車間之間往返運輸所需要的時間,極大地提高了生產效率。這樣一來系統的整體性能也得到了提升。

2.減輕北橋晶片的負擔,由於CPU與記憶體的數據交換量在整個電腦數據交換中所占的比例較大,所以整合之後北橋晶片的工作量極大第減少,進而可以為SATA、PCI-E等其它數據交換通道提供更高效的支持。

缺點 CPU內部整合記憶體控制器的最大缺點,就是對記憶體的適應性比較差,靈活性比較差,只能使用特定類型的記憶體,而且對記憶體的容量和速度也有限制,要支持新類型的記憶體就必須更新CPU內部整合的記憶體控制器,也就是說必須更換新的CPU;例如AMD的K8系列CPU就只能支持DDR,而不能支持更高速的DDR2。而傳統方案的記憶體控制器由於位於主機板晶片組的北橋晶片內部,就沒有這方面的問題,只需要更換主機板,甚至不更換主機板也能使用不同類型的記憶體,例如Intel Pentium4系列CPU,如果原來配的是不支持DDR2的主機板,那么只要更換一塊支持DDR2的主機板就能使用DDR2,如果配的是同時支持

DDR 和

DDR2 的主機板,則不必更換主機板就能直接使用DDR2。

總結 許多應用程式擁有更為複雜的讀取模式(幾乎是隨機地,特別是當cache hit不可預測的時候),並且沒有有效地利用

頻寬 。典型的這類應用程式就是業務處理軟體,即使擁有如

亂序執行 (out of order execution)這樣的CPU特性,也會受

記憶體延遲 的限制。這樣CPU必須得等到運算所需數據被除數裝載完成才能執行指令(無論這些數據來自CPU cache還是主記憶體系統)。當前低段系統的記憶體延遲大約是120-150ns,而CPU速度則達到了3GHz以上,一次單獨的記憶體請求可能會浪費200-300次CPU循環。即使在

快取命中率 (cache hit rate)達到99%的情況下,CPU也可能會花50%的時間來等待記憶體請求的結束- 比如因為

記憶體延遲 的緣故。

可以看到Opteron整合的記憶體控制器,它的延遲,與

晶片組 支持雙通道DDR記憶體控制器的延遲相比來說,是要低很多的。

英特爾 也按照計畫的那樣在

處理器 內部

整合記憶體控制器 ,這樣導致

北橋晶片 將變得不那么重要。但改變了處理器訪問主存的方式,有助於提高

頻寬 、降低記憶體延時和提升處理器性能。

傳統的計算機系統其記憶體控制器位於主機板晶片組的北橋

晶片 內部,CPU要和記憶體進行

數據交換 ,需要經過“CPU--北橋--記憶體--北橋--CPU”五個步驟,在此模式下數據經由多級傳輸,數據延遲顯然比較大從而影響計算機系統的整體性能;而AMD的K8系列CPU(包括Socket 754/939/940等接口的各種處理器)內部則整合了記憶體控制器,CPU與記憶體之間的數據交換過程就簡化為“CPU--記憶體--CPU”三個步驟,省略了兩個步驟,與傳統的記憶體控制器方案相比顯然具有更低的數據延遲,這有助於提高計算機系統的整體性能。

記憶體控制器

記憶體控制器

記憶體控制器

記憶體控制器