基本介紹

- 中文名:8088晶片

- 推出時間:1979年

- 公司:INTEL公司

- 屬於:16位微處理器

- 時鐘頻率:4.77MHz

晶片介紹,匯流排介紹,匯流排周期介紹,基本工作方法,

晶片介紹

1981年8088晶片首次用於IBM PC機中,開創了全新的微機時代。也正是從8088開始,PC機(個人電腦)的概念開始在全世界範圍內發展起來。

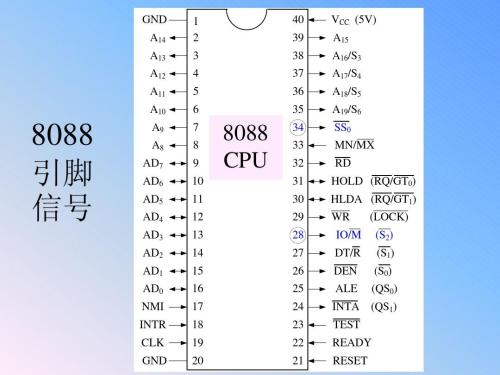

8088為40條引線、雙列直插式封裝。它們的40條引線排列如圖5.1所示。8088有最小組態(單微處理器組成的小系統)和最大組態(多處理器系統)兩種工作模式,如下圖所示,大部分引腳在兩種組態下功能是一樣的,只有8根引腳的名稱及功能不同(24腳~31腳)。由於在PC機內,8088工作於最大組態,所以在引腳功能介紹時,為了突出重點我們只介紹最大模式的引腳功能。

匯流排介紹

AD7~AD0:8位地址/數據匯流排,分時復用、雙向、三態。

A15~A8:地址線,三態輸出。

A19/S6~A16/S3:地址/狀態線,分時復用、輸出、三態。在匯流排周期的T1狀態作地址線用,A19~A16輸出高4位地址。在匯流排周期的T2~T4狀態作狀態線用,S6~S3輸出狀態信息,其中:S6恆為0。S5指示中斷允許標誌IF的當前狀態,S5 = 1,表示當前允許可禁止中斷請求,S5=0,則禁止一切可禁止中斷。S4和S3用以指示是哪一個段暫存器正在使用,其編碼和使用的段暫存器如下:00為ES,01為SS,10為CS,11為DS。

匯流排周期介紹

1. 指令周期: CPU執行一條指令的時間(包括取指令和執行完該指令所需的全部時間)稱為一個指令周期。

3. 時鐘周期:也就是系統主時鐘頻率的倒數,它是CPU的基本時間計量單位,例如,某CPU的主頻為5MHz,則其一個時鐘周期就是200ns,若主頻為10MHz,則一個時鐘周期為100ns。

8086/8088CPU的一個基本匯流排周期由4個時鐘周期(T1,T2,T3,T4)組成,時鐘周期也稱為時鐘狀態,即T1狀態、T2狀態、T3狀態和T4狀態。每一個時鐘周期(時鐘狀態)內完成一些基本操作。例如:

在T1狀態,CPU往數據/地址多路復用匯流排上發出訪問存儲器或I/O連線埠的地址信息。

在T2狀態,CPU從匯流排上撤銷地址,若為讀周期發出“RD”控制信號,使數據/地址多路復用匯流排的低8位處於高阻抗狀態,以便CPU有足夠的時間從輸出地址方式轉變為輸入數據方式,接著在T3~T4期間,CPU從匯流排上接收數據。若為寫周期發出“WR”控制信號,由於輸出數據和輸出地址都是寫匯流排過程,因而不需要緩衝時間,CPU在T2~T4期間把數據放到匯流排上。

基本工作方法

RESET:復位信號,輸入、高電平有效。

READY:準備就緒信號,輸入、高電平有效。CPU在每個匯流排周期的T3狀態檢測Ready信號線,如果Ready為低電平,表示數據末準備好,則在T3狀態結束後CPU插入一個或幾個TW等待狀態,直到Ready信號有效後,才進入T4狀態,完成數據傳送過程。

TEST:測試信號,輸入、低電平有效。TEST信號是和等待指令WAIT配合使用的信號。

QS1、QS0:指令佇列狀態信號,輸出,高電平有效。這兩個信號的組合用來指示CPU中指令佇列的當前狀態。QS1、QS0的代碼組合與對應的操作定義如表5.1所示。

S2、S1、S0:匯流排周期狀態信號,三態、輸出。在最大模式系統中,匯流排周期狀態信號S2、S1、S0用來指示當前匯流排周期所進行的操作類型。S2、S1、S0的編碼與匯流排操作類型的對應關係如表5.2所示。

LOCK:匯流排封鎖信號,三態、輸出、低電平有效。LOCK信號可由指令前綴LOCK來設定。

RQ/GT0、RQ/GT1:匯流排請求信號(輸入)/匯流排請求允許(輸出),雙向、低電平有效。在最大模式中,這兩個信號用來供CPU以外的兩個協處理器發出匯流排請求(RQ)和接收CPU對其匯流排請求信號的回響信號(GT0,GT1)。其中RQ/GT0比RQ/GT1有更高的優先權。

RD:讀信號,三態、輸出、低電平有效。RD信號有效,表示CPU正在對存儲器或I/O連線埠進行讀操作。

MN/MX:最小/最大工作模式控制信號,輸入。當MN/MX接高電平時,則CPU工作在最小模式。當MN/MX接低電平時,則CPU工作在最大模式。

SSO:系統狀態輸出信號,輸出。在最小模式下,該信號與其它兩個信號一起反應8088匯流排操作類型。在最大模式下,該引腳輸出恆為高電平。