簡介

存儲器是存儲指令和數據的計算機部件。有多種類型。中央處理器從存儲器中取出指令,按指令的地址從存儲器中讀出數據,執行指令的操作。存儲容量和存儲器讀寫數據周期是存儲器的兩個基本技術的指標。

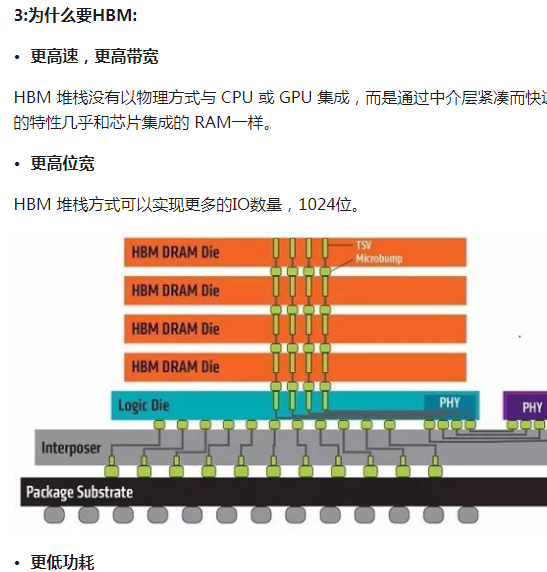

高頻寬存儲器是一種CPU/GPU 記憶體晶片(即 “RAM”),其實就是將很多個

DDR晶片堆疊在一起後和GPU封裝在一起,實現大容量,高位寬的DDR組合陣列。HBM 堆疊沒有以物理方式與 CPU 或 GPU 集成,而是通過中介層緊湊而快速地連線,HBM 具備的特性幾乎和晶片集成的 RAM一樣,因此,具有更高速,更高頻寬。

發展

第一,早期,AI處理器架構的探討源於學術界的半導體和體系架構領域,此時模型層數較少,計算規模較小,算力較低。

第二,模型逐漸加深,對算力需求相應增加,導致了頻寬瓶頸,即IO問題,此時可通過增大片內快取、最佳化調度模型來增加數據復用率等方式解決

第三,雲端AI處理需求多用戶、高吞吐、低延遲、高密度部署。計算單元劇增使IO瓶頸愈加嚴重,要解決需要付出較高代價(如增加DDR接口通道數量、片內快取容量、多晶片互聯)

此時,片上HBM(High Bandwidth Memory,高頻寬存儲器)的出現使AI/深度學習完全放到片上成為可能,集成度提升的同時,使頻寬不再受制於晶片引腳的互聯數量,從而在一定程度上解決了IO瓶頸。

雙倍數據率同步動態隨機存取存儲器

雙倍數據率同步動態隨機存取存儲器(Double Data Rate Synchronous Dynamic Random Access Memory,簡稱DDR SDRAM)為具有雙倍數據傳輸率的SDRAM,其數據傳輸速度為系統時鐘頻率的兩倍,由於速度增加,其傳輸性能優於傳統的SDRAM。DDR SDRAM 在系統時鐘的上升沿和下降沿都可以進行數據傳輸。JEDEC為DDR存儲器設立速度規範,並分為以下兩個部分:按記憶體晶片分類和按記憶體模組分類。DDR SDRAM模組部分與SDRAM模組相比,改為採用184針(pin),4~6 層印刷電路板,電氣接口則由「LVTTL」改變為「SSTL2」。在其它組件或封裝上則與SDRAM模組相同。DDR SDRAM模組一共有184個接腳,且只有一個缺槽,與SDRAM的模組並不兼容。 DDR SDRAM在命名原則上也與SDRAM不同。SDRAM的命名是按照時鐘頻率來命名的,例如PC100與PC133。而DDR SDRAM則是以數據傳輸量作為命名原則,例如PC1600以及PC2100,單位 MB/s。所以 DDR SDRAM中的DDR200 其實與 PC1600 是相同的規格,數據傳輸量為 1600MB/s(64bit×100MHz×2÷8=1600MBytes/s),而 DDR266與PC2100 也是一樣的情形(64bit×133MHz×2÷8=2128MBytes/s)。

DDR SDRAM 在規格上按信號延遲時間(CL;CAS Latency,CL是指記憶體在收到訊號後,要等待多少個系統時鐘周期後才進行讀取的動作。一般而言是越短越好,不過這還要看記憶體顆粒的原始設定值,否則會造成系統的不穩定)也有所區別。按照電子工程設計發展聯合協會(JEDEC)的定義(規格書編號為JESD79):DDR SDRAM一共有兩種CAS延遲,分為2ns以及2.5ns(ns為十億分之一秒)。較快的 CL= 2 加上 PC 2100 規格的 DDR SDRAM稱作 DDR 266A,而較慢的 CL= 2.5 加上PC 2100規格的DDR SDRAM 則稱作 DDR 266B。另外,較慢的 PC1600 DDR SDRAM 在這方面則是沒有特別的編號。