在電路設計中,網表(netlist)是用於描述電路元件相互之間連線關係的,一般來說是一個遵循某種比較簡單的標記語法的文本檔案。門級(gate-level)指的是網表描述的電路綜合級別。顧名思義,門級網表中,描述的電路元件基本是門(gate)或與此同級別的元件。

基本介紹

- 中文名:門級網表

- 外文名:Gate-Level netlist

- 關係:同級別元件

- 用途:用於描述電路元件相互連線關係

解析

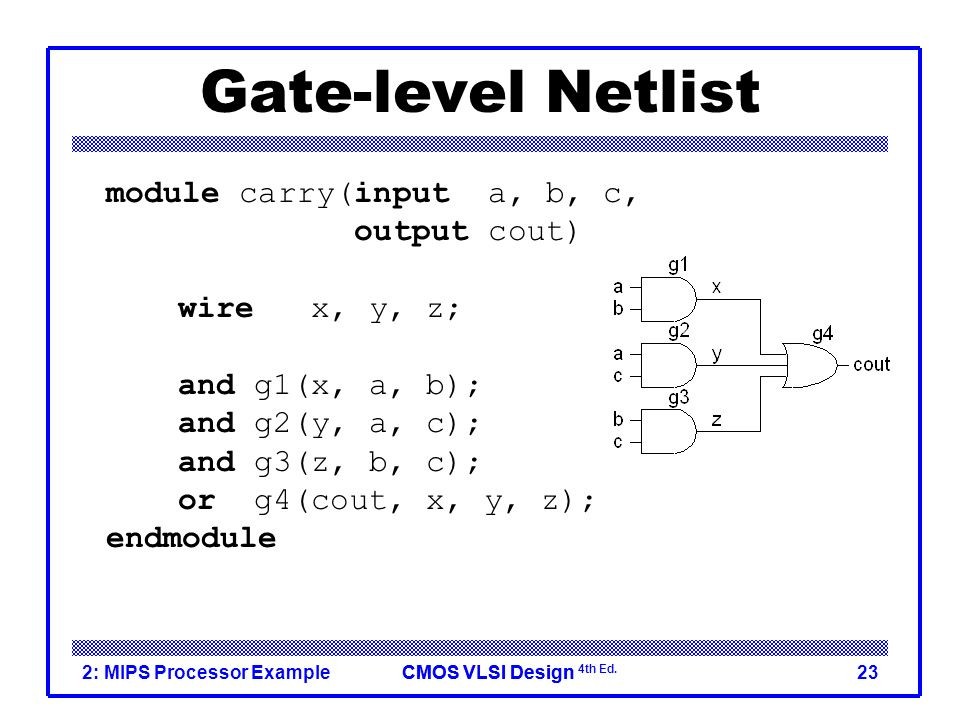

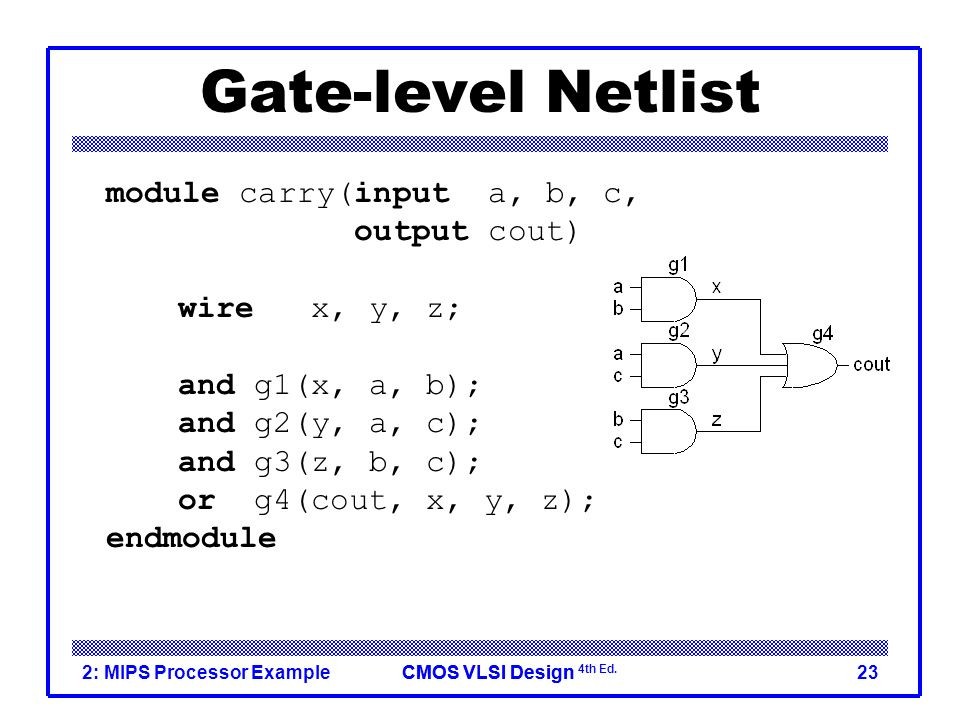

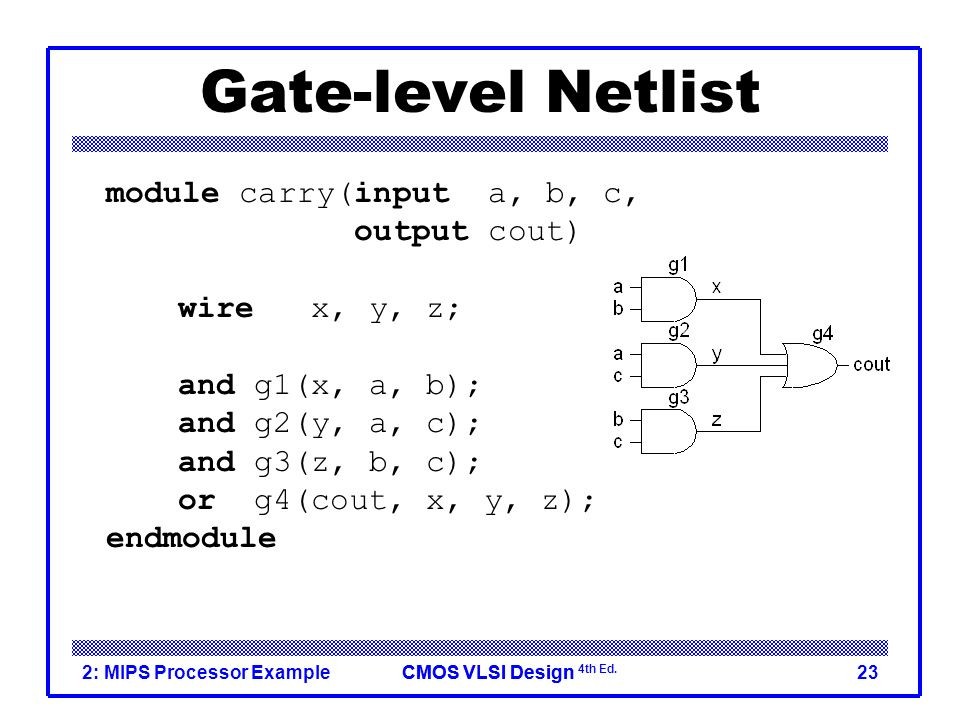

門級網表示意圖

在電路設計中,網表(netlist)是用於描述電路元件相互之間連線關係的,一般來說是一個遵循某種比較簡單的標記語法的文本檔案。門級(gate-level)指的是網表描述的電路綜合級別。顧名思義,門級網表中,描述的電路元件基本是門(gate)或與此同級別的元件。

在電路設計中,網表(netlist)是用於描述電路元件相互之間連線關係的,一般來說是一個遵循某種比較簡單的標記語法的文本檔案。門級(gate-level)指的是網表描述的電路...

設計人員編寫的Verilog代碼通常是在較高抽象級別的,例如暫存器傳輸級。這一抽象級別包含了對電路信號在暫存器之間傳輸情況的描述。但是邏輯門級的網表,即邏輯門的相互...

形式驗證主要驗證數字IC設計流程中的各個階段的代碼功能是否一致,包括綜合前RTL代碼和綜合後網表的驗證,因為如今IC設計的規模越來越大,如果對門級網表進行動態仿真,...

的系統級(有人也稱之為行為級),使用硬體描述語言或高級建模語言來描述電路的邏輯、時序功能,而邏輯綜合可以自動將暫存器傳輸級的硬體描述語言轉換為邏輯門級的網表...

固核在EDA 設計領域指的是帶有平面規劃信息的網表;具體在FPGA 設計中可以看做...虛擬器件往往只提供門級和RTL級的Verilog HDL或VHDL原始碼,而虛擬接口模型往往...

邏輯綜合得到門級網表。4.門級驗證(Gate-Level Netlist Verification)門級功能驗證是暫存器傳輸級驗證。主要的工作是要確認經綜合後的電路是否符合功能需求,該工作...

7.3.3 暫存器傳輸級對暫存器傳輸級的驗證7.3.4 暫存器傳輸級對門級網表的驗證7.3.5 從門級網表到門級網表驗證7.3.6 調試...

門級建模與仿真;電路級和系統級單粒子效應建模與仿真;硬體故障注入;採用加速測試...5.4.2 門級網表SEE仿真5.4.3 行為級/RTL/HLS SEE仿真5.5 靜態SEE分析...