解擾碼器是一種為了恢復原始信號對擾碼信號進行處理的器件。在數位訊號傳輸中,傳送端往往要加擾碼器,相應的接收端要加解擾碼器。解擾碼器在接收端將被擾亂後的序列還原為傳送機的數字序列。擾碼加擾和解擾碼利用了擾碼的正交性。一般使用的擾碼是偽隨機序列碼,只要在接收端有相同擾碼的發生器,就能實現解碼的功能。

| 中文名稱 | 解擾碼器 |

| 英文名稱 | descrambler |

| 定 義 | 為恢復原始信號而對擾碼信號進行處理的器件。 |

| 套用學科 | 通信科技(一級學科),通信原理與基本技術(二級學科) |

基本介紹

- 中文名:解擾碼器

- 外文名:descrambler

- 定義:對擾碼信號進行處理的器件

- 學科:通信

主要內容,分類,基於CPLD的擾碼解擾碼器,光同步數字傳輸系統解擾碼器,基於FPGA的解擾碼器,實例,

主要內容

在數字通信系統接口中,某些碼流經過擾碼處理以後,不再是原來的內容,但經過解碼後,又可以恢復原來的內容。只要擾碼器的級數選擇適當,則經擾碼以後的碼流則可以是充分隨機的,從而改善中繼線路的抖動等方面。在數位訊號傳輸中,傳送端往往要加擾碼器,相應的接收端要加解擾碼器。解擾碼器在接收端將被擾亂後的序列還原為傳送機的數字序列。擾碼加擾和解擾碼利用了擾碼的正交性。一般使用的擾碼是偽隨機序列碼,只要在接收端有相同擾碼的發生器,就能實現解碼的功能。現階段的解擾碼器通常是在接收機端使用相同的擾碼序列與收到的被擾信息進行模二和, 就可將原信息恢復。

在數字通信中,當數據信息連“0”碼或者連"1"碼過長將會影響接受端位定時信息的恢復質量,造成抽樣判決時刻發生變化,對系統的誤碼率產生影響,甚至有可能接受全錯的信息。採用有冗餘的傳輸編碼可以消除數據源一部分信息模式對系統性能的影響,但是要以增加傳輸符號速率為代價。在實際的套用中,常使用擾碼器將數據源變成近似於白噪聲的數據序列,以增加定時的同步信息,消除信息模式對系統誤碼的影響。在系統光發射機的調製之前,需要附加一個擾碼器,將原始的二進制碼序列加以變換,使其接近於隨機序列。相應的,在光接收端的判決之後,附加一個解擾碼器,以恢復原始序列。擾碼與解碼可以由反饋移位暫存器和對應的前饋移位暫存器實現。

分類

基於CPLD的擾碼解擾碼器

將待傳送的信息序列與發端產生的m序列進行模二加(擾碼),擾碼序列通過傳輸信道傳送到接受端,接受端通過同步模組提取位定時信息,驅動本地m序列發生器產生與發端一樣的m序列,然後再跟接受到的擾碼序列進行模二加,恢復原來信息。

m序列具有類似於隨機信號較好的自相關特性。m序列由線性反饋移位暫存器加權產生。根據反饋係數的取值不同,電路可以產生出各種具有不同特性的數字序列。對於一定的移位暫存器級數r,存在一些特殊的Ci取值,使得輸出序列的周期達到最長,即為2?1。這樣的序列被稱為最長線性反饋移位暫存器序列,即m序列。

光同步數字傳輸系統解擾碼器

同步數字傳輸系統一般由傳輸設備和網路節點兩種基本設備組成,對於光同步數字傳輸系統,傳輸設備就是光纜系統,網路節點則比較複雜,包含終結設備(TM)、交叉連線設備(DXC)、復用設備(ADM)等。光同步數字傳輸系統中最基本的模組信號是STM-1信號,線速率為155.520Mbit/s,STM-N信號是將基本模組信號STM-1同步復用、經位元組間插後的結果,線速率是N×155.520Mbit/s;這些信號在傳輸過程中都是按比特串列傳送信號,但沒有傳送本節點的時鐘信號。各節點的接收端所需的數據接收及後續處理的時鐘都是從接收到的數據信號中恢復出來的。根據常用的時鐘數據恢復(CDR)原理,時鐘恢復是依靠數據信號的變化沿完成,如果接收到的數據流中有長連0或長連1序列出現,則按該原理恢復出的時鐘不再精準,用這樣恢復出來的時鐘處理數據會導致數據信息的丟失或錯誤,因此為了保證在接收端能精準地進行數據接收和時鐘提取,必須杜絕傳輸的數據流中有長連0或長連1序列出現。

光同步數字傳輸系統SDH加/解擾碼器包括:比特擾碼電路,位元組擾碼電路,選擇器,暫存器組1,暫存器組2,解碼器1,解碼器2,解碼器3。比特擾碼電路的輸入來自暫存器組2的輸出,結果輸出到選擇器的1端,位元組擾碼電路的輸入來自暫存器組1的輸出,結果輸出到選擇器的0端,選擇器控制選擇位來自解碼器1的輸出,其結果輸出到暫存器組1,暫存器組1的使能位來自解碼器2的輸出,暫存器組1的輸出就是整個擾碼器電路的輸出,同時也輸出到暫存器組2和位元組擾碼電路,暫存器組2的使能位來自解碼器3的輸出。如上所述的SDH加/解擾碼器大大降低了處理速率,並簡化了邏輯,使得的電路的規模大大降低,更易於工藝實現。

基於FPGA的解擾碼器

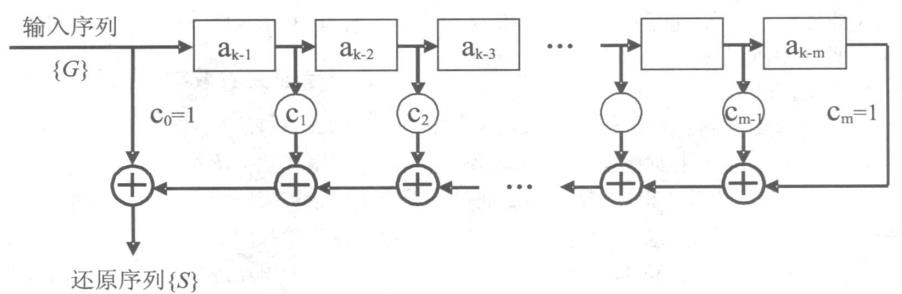

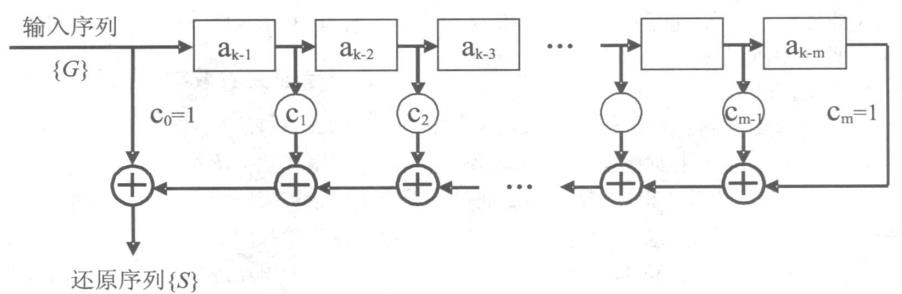

在通信中採用擾碼技術必須保證對信息的透明性 :即在發端擾碼的加入,在接收端可以從加擾的碼流中恢復出原始的數據流,而對輸入信息的模式無特殊要求。常用擾碼器的可採用 m序列來實現。擾碼器是在傳送端使用移位暫存器產生m序列,然後信息序列{S}與m序列進行模二和,其輸出即為加擾的隨機序列 {G}。 一般擾碼器的結構如右圖所示,其中 Ci (i = 0, 1…n)是反饋係數,只能取 0、1兩個值,0表示不參與反饋,1表示參與反饋。 解碼器結構

解碼器結構

解碼器結構

解碼器結構FPGA的解擾碼器選用了基於“ PC + DSP + FPGA ” 技術的結構,具有一些獨立的功能開發模組電路,有獨立外部輸入信號和測試連線埠,基於FPGA技術 ,採用MAX7000系列器件,主要包括EPM7128SLC80 - 15、EPM7064SLC44 - 10、EPM7032SLC44 - 10器件 。

實例

下面通過一個實例分析擾碼與解碼的作用。

數據序列 10101011101111100000011

隨機序列 10010011001010001101010

加擾序列 00111000100101101101001

對數據序列與隨即序列進行模2運算,就得到加擾序列。擾碼雖然擾亂了數字序列的原有形式,但只要這種擾亂有人為規律,就可以解除。

在收端做相反的變換,即解擾碼,就可恢複數字序列的原始形式。如果傳輸過程中沒有產生誤碼,適用於傳送端相同的隨即序列對接收的序列進行模2運算,就可恢復原來的數據序列。

加擾序列00111000100101101101001

隨機序列10010011001010001101010

數據序列 10101011101111100000011