藍寶石上外延矽工藝是在藍寶石片上外延生長一層矽薄膜以製作半導體積體電路的技術,簡稱 SOS。

基本介紹

- 中文名:藍寶石上外延矽工藝

- 外文名:SOS

詳細介紹

分類

藍寶石上外延矽工藝是在藍寶石片上外延生長一層矽薄膜以製作半導體積體電路的技術,簡稱 SOS。

藍寶石上外延矽工藝是在藍寶石片上外延生長一層矽薄膜以製作半導體積體電路的技術,簡稱 SOS。...

合成藍寶石或尖晶石的成本超過同尺寸的矽wafer太多了,所以大多數外延生長沉積還是在矽底層上生長矽薄膜。 有幾種不同的方法來生長外延(epi)層。一種比較粗糙的...

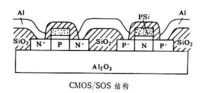

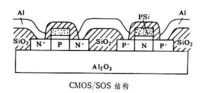

生長外延層有多種方法,但採用最多的是氣相外延工藝。圖1為矽(Si)氣相外延的...這樣就能在一個襯底上外延生長出不同的晶膜,如在藍寶石或尖晶石襯底上外延生長...

第六節特種表面活性劑的生產工藝108一、氟碳表面活性劑108二、矽表面活性劑109...三、藍寶石上外延矽片(SOS)227四、陶瓷基片227第三節光致抗蝕劑227...

·藍寶石(Al2O3)、矽(Si)、碳化矽(SiC)·藍寶石襯底藍寶石 編輯 通常,GaN基材料和器件的外延層主要生長在藍寶石襯底上。藍寶石襯底有許多的優點:首先,藍寶石...

工業生產常用的氣相外延工藝有:四氯化矽(鍺)外延,矽(鍺)烷外延、三氯氫矽及...金屬源化學氣相外延法在c面藍寶石上生長的ZnO膜及其表征[C]// 全國化合物...

外延片是在矽單晶片襯底(或尖晶石、藍寶石等絕緣襯底)上外延生長矽單晶薄層而...矽是地殼上最豐富的元素半導體, 性質優越而工藝技術比較成熟,已成為固態電子器件...

中文名稱 SOS外延片 英文名稱 silicon on sapphire epitaxial wafer,SOS expitaxial wafer 定義 在藍寶石襯底上外延生長的矽單晶薄膜材料。 套用學科 材料科學...

LED外延片紅黃光 編輯 紅光LED以GaP(二元系)、AlGaAs(三元系)和AlGaInP(四元系)為主,主要採用GaP和GaAs作為襯底,未產業化的還有藍寶石Al2O3和矽襯底。1、...

現有的三條LED照明技術路線,分別是藍寶石、碳化矽和矽襯底GaN基LED技術路線。...結構和工藝技術,在國際上率先研製成功高內量子效率矽襯底藍光LED外延材料和高取光...

後獨立開創了以下三方面的工作:從異質外延界面結合能考慮,提出藍寶石上異質外延矽(矽/藍寶石或SOS)的成核半徑小於矽/尖晶石,SOS薄膜的質量要高於矽l尖晶石,重新...

後獨立開創了以下三方面的工作:從異質外延界面結合能考慮,提出藍寶石上異質外延矽(矽/藍寶石或SOS)的成核半徑小於矽/尖晶石,SOS薄膜的質量要高於矽l尖晶石,重新...