端接簡介

見

對接,在高速PCB設計中,高速電路中由阻抗不匹配引起的信號反射現象,通過端接電路在抑制攻擊線上反射,是減輕反射信號影響的一種有效可行的方式。

源端端接

即在靠近晶片的傳送端

串聯電阻,使得該串聯電阻與晶片的內阻之和儘量與傳輸線

阻抗一致。該端接簡單功耗小,不會給驅動器帶來額外的

直流負載,只需要一個電阻就可以抑制驅動端到負載端的二次反射,常用於點對點的拓撲上;但同時它會增加

RC時間常數,減緩負載端信號上升時間,因此不適合用於

高頻信號通路。

終端端接

即在末端並聯一個與傳輸線特性阻抗一致的電阻到

GND或者電源上。該端接的優點是在信號能量反射回源端之前在負載端消除反射,可以減小噪聲、

電磁干擾(EMI)及射頻干擾(

RFI)。同時也是有缺點的,首先末端端接電阻會增加直流功耗,所以

功耗較大,不適用於使用電池供電的產品,此外在邏輯高狀態下,對器件的驅動能力要求較高。

端接電阻方式詳解

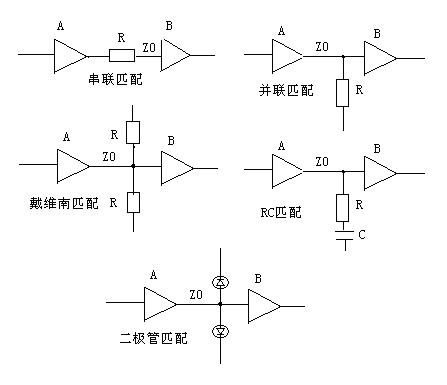

常用的端接電阻方式有以下幾種:

源端串聯匹配

源端串聯匹配就是在輸出BUFFER上串接一個電阻,使BUFFER的輸出阻抗與傳輸線阻抗一致;此電阻在

PCB設計時應儘量靠近輸出

BUFFER放置 ,常用的值為:33歐姆。

對於TTL或CMOS驅動,信號在邏輯高及低狀態時均具有不同的輸出阻抗,而一些

負載器件可能具有不同的輸入輸出阻抗,不能簡單的得知,所以在使用串聯端接匹配時,在具有輸入輸出阻抗不一致的條件下,可能不是最佳的選擇;在布線終端上存在集匯流排型負載或單一元件時,串聯匹配是最佳的選擇;

串聯電阻的大小由下式決定:

R=ZO-R0 ZO--傳輸線阻抗 R0--BUFFER輸出阻抗

串聯匹配的優點:提供較慢的上升時間,減少反系量,產生更小的EMI,從而降低過沖,增加信號的傳輸質量;

串聯匹配的缺點:當

TTL/

CMOS出同一網路上時,在驅動分布負載時,通常不能使用串聯匹配方式。

終端並聯匹配

由在走線路徑上的某一端連線單個電阻構成,這個電阻的阻值必須等於傳輸線所要求的電阻值,電阻的另一端接電源或地;簡單的並聯匹配很少用於

CMOS與

TTL設計中;

並聯匹配的優點:可用於分布負載,並能夠全部吸收傳輸波以消除反射;

並聯匹配的缺點:需額外增加電路的功耗,會降低噪聲容限。

戴維南匹配

Vref=R2/(R1+R2)*V

Vref--輸入負載所要求的電壓

當R1=R2時,對高低邏輯的驅動要求均是相同的,對有些邏輯系列可能不能接受;

當R1>R2時,邏輯低對電流的要求比邏輯高大,這種情況對TTL與COMS器件是不能工作的;

當R1<R2時,這種對大多數的設計比較合適;

戴維南匹配的優點: 能夠全部吸收傳輸波以消除反射,尤其適合用於匯流排使用;

戴維南匹配的缺點:需額外增加電路的功耗,會降低噪聲容限;

RC網路匹配

端接電阻應該等於傳輸線的阻抗Z0,而電容一般非常小(20PF--600PF);RC網路的時間常數必須大於兩倍的信號傳輸延時時間;

RC端接匹配的優點:可在分布負載及匯流排布線中使用,它完全吸收傳送波,可以消除反射,並且具有很低的直流功率損耗;

RC端接的缺點:它將使非常高速的信號速率降低,RC電路的時間常數選擇不好會導致電路存在反射,對於高頻、快速上升的信號應多加注意。

二極體匹配

二極體匹配方式常用於

差分或成對網路上,採用二極體匹配會使其負載變成非線性,可能會增加EMI的問題。

各種匹配方式的特徵如下表所示:

終端類型

| 元件數

| 延時情況

| 電源要求

| 元件值

| 備註

|

並聯

| 1

| 小

| 高

| R=Z0

| 功耗很大

|

戴維南

| 2

| 小

| 高

| R=2Z0

| |

RC

| 2

| 小

| 中

| R=Z0,C很小

| |

二極體

| 2

| 小

| 高

| 根據電源電壓寶

| |