發展歷程 DMI的首次套用是作為2004年推出的英特爾900系列北橋晶片與

ICH6 南橋晶片之間的連線接口。此前英特爾推出的晶片組採用一種名為集線器接口(Hub Interface)的接口來連線南橋和北橋,而

伺服器 用途的晶片組使用與之類似但頻寬更高一些的企業南橋接口(Enterprise Southbridge Interface,縮寫ESI)。DMI儘管命名可追朔自ICH6,但英特爾為了列出晶片的設備兼容性詳細數據,而專門使用了“Direct Media Interface”的命名,因此DMI並不能保證允許特定的南橋-北橋晶片的搭配。

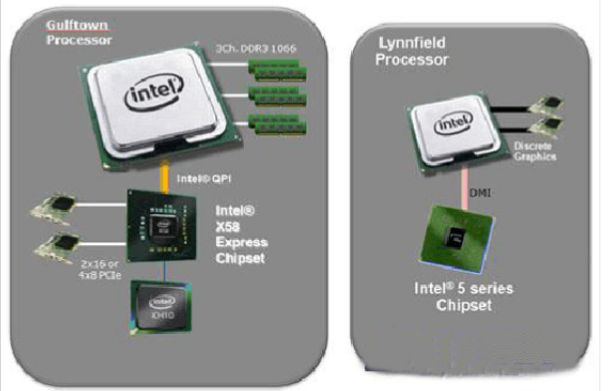

隨著Intel Nehalem微架構處理器的發布,老邁的FSB(前端匯流排)被QPI(快速通道互連)匯流排(如Bloomfield/Gulftown,Core i7-900系列)、DMI匯流排(如Lynnfield/Clarkdale,Core i7-800系列、Core i5-700/600系列、Core i3-500系列)取代,為新一代的處理器提供更快、更高效的數據頻寬,FSB的系統瓶頸問題也隨之得以解決。

技術概況 DMI與PCIe匯流排共用了大量的技術特性,像是多通道、

差分信號 、點對點連線、

全雙工 、

8b/10b 編碼等。大部分DMI的通信布局類似於PCIe x4規格,不過,最初一些

移動計算機 平台上則是使用接近PCIe x2的規格,頻寬減半,例如915GMS、945GMS/GSE/GU以及Atom N450。DMI使用x4鏈路時在一個傳輸方向上能提供10Gbit/s(1.16GB/s)的頻寬。

DMI 2.0於2011年發表,使用x4鏈路布局是能提供2GB/s的頻寬,接近兩倍於DMI。此時英特爾用它來連線CPU與PCH。

2015年3月9日,英特爾宣布完成了

PCH 和CPU的融合,使x86 PC

SoC 配置成為現實,這種設計首次使用在基於

Broadwell 微架構的Xeon D上。在原本認為DMI會因x86 SoC化而成為歷史時,DMI 3.0於2015年8月發布規格,每通道可擁有最大8GT/s的吞吐量,x4規格時有3.93GB/s的頻寬。也用於CPU與PCH的連線。部分Skylake的處理器連帶PCH集成進CPU晶片上,連線也採用DMI 3.0,不過此時是片上連線,即OPI(On Package DMI interconnect Interface,封裝的DMI互聯接口),是一個

片上系統 的布局。

相關技術 實現 支持DMI的北橋晶片有英特爾的915系列、925系列、945系列、955系列、965系列、975系列、G31/33/P35/X38系列、G41/43/P45/X48系列以及英特爾最後的獨立北橋晶片X58。

而支持DMI的處理器,是從集成到處理器上的北橋部分引出,這些處理器有

Atom 、第一代

Core i3 /i5/i7(除了

Core i7 9xx系列)。到DMI 2.0時,英特爾已經沒有新的獨立北橋晶片了,由CPUUncore部分提供DMI界面,使用Sandy Bridge微架構的第二代Core i3/i5/i7、

奔騰 和

賽揚 系列及以後的新型號全數支持DMI 2.0,直到使用Skylake微架構的第6代Core系列為止。

支持DMI的南橋晶片有ICH6、ICH7、ICH8、ICH9、

ICH10 、NM10,支持DMI的PCH:P55/H55、H57/Q57、PM55/HM55、HM57/QM57/QS57。

支持DMI 2.0的PCH設備有Z68、P67/H67/Q67、Q65/B65、H61、HM65、HM67/QM67/QS67、Z77/H77/Q77、Z75/Q75/B75/X79、HM75/HM76/HM77/UM77/QM77/QS77、H81、B85/Q85、Q87/H87/Z87、H97/Z97、C222/C224/C226/X99以及H110。

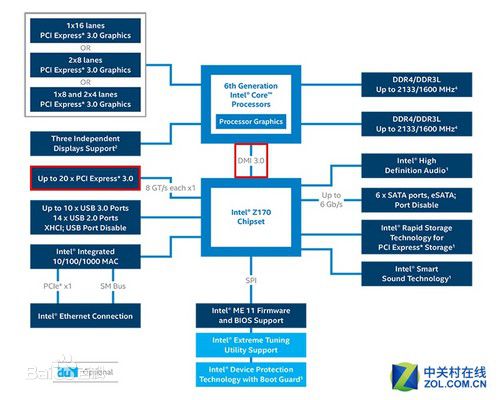

支持DMI 3.0的PCH有Z170/H170/HM170/Q170、QM170、Q150/B150、C236、CM236以及C232。後續發表的英特爾200系列晶片組也支持DMI 3.0。

具體介紹 在4系列晶片組沒有取消前端匯流排FSB時,DMI 是Intel(英特爾)公司開發用於北橋(G)MCH(Graphics & Memory controller hub)和南橋ICH10/ICH7之間的晶片連線匯流排。DMI實現了上行與下行雙向數據傳輸率,單通道單向傳輸速率達到2.5GT/s,採用8bit/10bit編碼,總計4條通道。這個高速接口集成了高級優先服務,允許並發通訊和真正的同步傳輸能力。它的基本功能對於軟體是完全透明的,因此早期的軟體也可以正常操作。

從5系列晶片組開始的新構架設計中,前端匯流排被取消,北橋晶片的功能被整合進CPU中。顯示卡採用了PCI-E ×16的通道直連CPU,當多卡交火時分為×8+×8(雙卡)或×8+×4+×4(三卡)(具體分配方式要參考主機板設計)。因為PCI-E2.0的套用,DMI升級到DMI2.0,單通道單向傳輸速率達到5GT/s。同時DMI2.0也不再用於南北橋晶片的連線,而是用於CPU和晶片組(原南橋晶片組)的連線。

從100系晶片組開始,DMI升級到DMI3.0,單通道傳輸速率達到8GT/s,採用128bit/130bit編碼,有效碼率高達98.46%,比8/10編碼的80%提高了很多。

DMI匯流排頻寬的計算:

理論最大頻寬(GB/s)=(傳輸速率*編碼率*通道數)/8(bit/byte轉換)

DMI理論最大頻寬=(2.5GT/s*8/10*4)/8=1GB/s

DMI2.0理論最大頻寬=(5GT/s*8/10*4)/8=2GB/s

DMI3.0理論最大頻寬=(8GT/s*128/130*4)/8=3.94GB/s

隨著Intel Nehalem微架構處理器的發布,老邁的

FSB (前端匯流排)被

QPI (快速通道互連)匯流排(如Bloomfield/Gulftown,Core i7-900系列)、DMI匯流排(如Lynnfield/Clarkdale,Core i7-800系列、Core i5-700/600系列、Core i3-500系列)取代,為新一代的處理器提供更快、更高效的數據頻寬,FSB的系統瓶頸問題也隨之得以解決。

例如在P55主機板上,已經完全看不到北橋晶片的蹤影,只剩下了一個名為PCH(平台控制器中樞)的晶片用來支持外設。原來,在P55平台中,北橋功能已經完全被整合在了CPU當中,就連最後的PCI-E匯流排也被整合到其中。這樣一來,CPU對PCI-E匯流排和記憶體的控制權就完全交給了自己,這也是LGA1156與LGA1366最大的不同,當然其內部通信依然是數據量驚人的QPI匯流排。而PCH晶片部分雖然相比原來的南橋晶片功能上更為豐富,但其性質大體相同,它與CPU間同樣不需要交換太多數據,因此連線匯流排採用DMI已足夠了。所以,看似只有2.5GT/s的DMI匯流排實質上是徹底釋放了北橋壓力,換來的是更高的性能。 雖然Lynnfield(Core i7-800系列/Core i5-700系列)平台在物理上由“CPU-北橋-南橋”的三晶片連線變為“CPU-PCH”的雙晶片連線,但是QPI匯流排連線還是存在的,它連線著Lynnfield處理器的“Core(核心)”和“UnCore(外圍核心,如L1/L2/L3 Cache、MCH、PCI-E控制器等)”兩部分,而通過DMI匯流排和PCH晶片通信的是處理器的UnCore部分而不是Core部分,這實際上還是之間那種“CPU到北橋晶片用QPI或FSB匯流排,北橋晶片到南橋晶片用DMI匯流排”的連線方式,三晶片與雙晶片的連線方式本質上並沒有改變。 當然也不能把PCH晶片和ICH南橋晶片相等同,因為除了繼承傳統南橋晶片的輸入輸出功能外,PCH晶片還承擔了傳統北橋晶片諸如Dispaly單元、Management Engine單元、NVRAM單元以及Clock Buffers單元等任務。不過雖然PCH晶片的功能要比傳統ICH南橋晶片的功能要複雜一些,但是其和處理器的UnCore部分之間是不需要進行太多通信的,因此一條“古老”的DMI匯流排足以滿足其數據交換

需求 。

DMI是否取代QPI QPI和DMI對比 答案是否定的。 在發現了 DMI的優勢之後還不能忽略的是, 在 CPU內部集成了如此多的控制器,在數據傳輸方面的要求更高,所以 intel 在 CPU內部依然保留了 QPI 匯流排,用於 CPU內部的數據傳輸。這樣,這兩個匯流排的傳輸任務就分工明確了, QPI 主管內, DMI主管外 ,全新的 Lynnfield 核心的 Core i7/i5 處理器離不開高效快速的匯流排連線,內外如一。

在這裡還需要注意一點的是,在 Bloomfield 核心的 i7 系列上, QPI 匯流排的高速度是為雙 PCI-E X16 準備的,需要保證的是整個平台的性能優勢,當 PCI-E 控制器移到 CPU內部後,那么這個高速的傳輸匯流排當然就可以免去了, 而且從 CPU內部直連 L2 快取的效果更佳, 低速的 DMI匯流排也完全可以勝任 CPU與外部晶片的連線。

總之,從技術的發展上來講, DMI 占據主導地位說明了技術的進步,但是 QPI 仍然是 intel追求技術創新的衍生物,不可被忽視。

QPI和DMI對比

QPI和DMI對比