時鐘信號延滯是指時鐘源插入延遲和時鐘網路插入延遲。

基本介紹

- 中文名:時鐘信號延滯

- 外文名:Clock signal delay

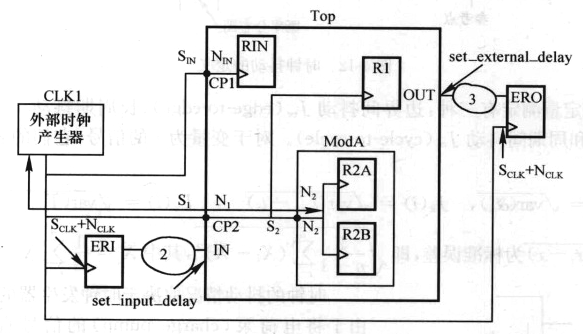

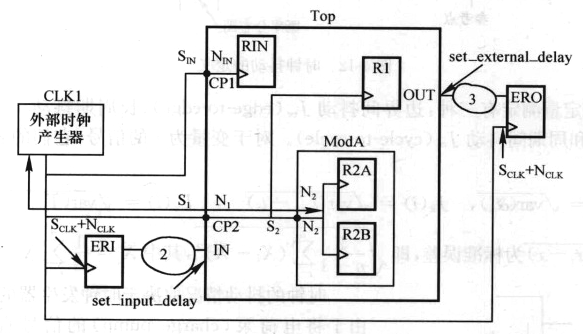

圖1 定義的時鐘插入延遲(Sxx為時鐘源延遲;Nxx為時鐘網路延遲)

圖1 定義的時鐘插入延遲(Sxx為時鐘源延遲;Nxx為時鐘網路延遲)時鐘信號延滯是指時鐘源插入延遲和時鐘網路插入延遲。

圖1 定義的時鐘插入延遲(Sxx為時鐘源延遲;Nxx為時鐘網路延遲)

圖1 定義的時鐘插入延遲(Sxx為時鐘源延遲;Nxx為時鐘網路延遲)時鐘信號延滯是指時鐘源插入延遲和時鐘網路插入延遲。時鐘信號延滯(latency)又被稱為插入延遲(insertion delay),它包括兩部分,即時鐘源(clock source)插入延遲和時鐘網路(clock network)插入延遲。時鐘源插入延遲是來自系統(即時鐘...

時鐘抖動(jitter)定義為指信號時間與理想事件時間的偏差(deviation),抖動中含有確定抖動(DJ, deterministic jitter)成分和隨機抖動(RJ, random jitter)成分,理想事件的參考點可以選在時鐘信號的50%處(圖1)。確定抖動通常由串擾、電磁干擾...

時鐘信號是計算機科學以及相關領域用語,時鐘信號通常被用於同步電路當中,扮演計時器的角色,保證相關的電子組件得以同步運作。簡介 時鐘信號(Clock Signal)是時序邏輯的基礎,用於決定邏輯單元中的狀態何時更新,是有固定周期並與運行無關...

時鐘抖動的測量方法,並根據時鐘抖動與adc採樣信號信噪比之間的關係,提出利用信噪比測量時鐘抖動的兩種方法: (1)通過信噪比與信號頻率之間的關係計算時鐘抖動的頻率掃描法。 (2)通過信噪比與信號幅度之間的關係計算時鐘抖動的幅度掃描法.同時...

時鐘控制信號(clock control signal),又稱“定時信號”是指通過“關”和“開”控制雙時鐘交替倒換的信號。定時信號是保證整個數字通信系統能完全同步工作的關鍵。對再生中繼器來說,如何獲得定時信號,以便在均衡波的峰值出對均衡波進行...

具體來說,2.0GHz意味著每秒鐘它會產生20億個時鐘脈衝信號,每個時鐘信號周期為0.5納秒。而Pentium 4 CPU有4條流水線運算單元,如果負載均勻的話,CPU在1個時鐘周期內可以進行4個二進制加法運算。這就意味著該Pentium 4 CPU每秒鐘...

圖1 時鐘信號單元的組成 時鐘信號單元還產生一個實時時鐘(即電子鐘),用於例如計費、記錄等需要當地時間(時、分、秒)信號的部分。有的時鐘信號單元也產生交換機所需用的各種數位訊號音。組成 時鐘信號單元結構如圖所示。圖中由時鐘發生...

在MCS-51中時鐘周期也稱振盪周期,振盪周期也稱為晶振周期,振盪周期是單片機的基本時間單位。8051把一個振盪周期定義為一個節拍(用P表示),兩個節拍為一個狀態周期。振盪器脈衝信號經過時鐘電路二分頻之後產生的單片機時鐘信號的周期(用...

時鐘饋通效應 MOSFET用作開關時gate端接時鐘信號而source和drain端通過信號由於存在cgs和cgd時鐘信號可能會耦合到source和drain端從而影響信號這就是時鐘饋通

時鐘信號偏差是指同一時鐘到達該時鐘域內的不同暫存器器之間的偏差。所謂時鐘信號的偏差(skew)指的是同一時鐘到達該時鐘域內的不同暫存器之間的偏差,也即skew=max(|t-t|),其中t和t分別為時鐘根節點到達葉節點的時間,0 偏差的...

時間脈衝信號(英語:Clock signal),計算機科學及相關領域用語。此信號在同步電路當中,扮演計時器的角色,並組成電路的電子組件。只有當同步信號到達時,相關的觸發器才按輸入信號改變輸出狀態,因此使得相關的電子組件得以同步運作。

時鐘同步是通過各個能產生時鐘的器件線連線到SCL線上來實現的,上述的各個器件可能都有自己獨立的時鐘,各個時鐘信號的頻率、周期、相位和占空比可能都不相同,由於“線與”的結果,在SCL 線上產生的實際時鐘的低電平寬度由低電平持續時間...

石英晶體振盪器是高精度和高穩定度的振盪器,被廣泛套用於彩電、計算機、遙控器等各類振盪電路中,以及通信系統中用於頻率發生器、為數據處理設備產生時鐘信號和為特定系統提供基準信號[1] 。石英晶體振盪器是利用石英晶體(二氧化矽的結晶體...

像素時鐘信號是一個非常重要的時鐘信號。像素時鐘信號的頻率與液晶面板的工作模式有關,液晶面板解析度越高,像素時鐘信號的頻率也越高。簡介 只要是數位訊號處理電路,就必須有時鐘信號。在一行內,像素時鐘的個數與液晶面板一行內所具有的...

時鐘觸發器,指的是凡是有時鐘信號控制的觸發器。數字電路中要實現各部分協同工作,需要有統一的時鐘脈衝來控制動作,簡稱為時鐘CP,凡是有時鐘信號控制的觸發器均稱為時鐘觸發器。時鐘觸發器又可分為同步觸發器、主從觸發器、邊沿觸發器...

時鐘饋通 時鐘饋通,金屬-氧化物-半導體場效應電晶體(MOSFET)用作開關,柵極端接時鐘信號,而源極和漏極端通過信號時,由於存在柵源電容(Cgs)和柵漏電容(Cgd),時鐘信號可能會耦合到源極和漏極端從而影響信號的現象。

高速外部時鐘信號HSE(High Speed External Clock signal)相應的還有HSI(High Speed Internal Clock signal)、LSE(Low..)、LSI(Low..)。產生來源 HSE時鐘是 STM32、STM8等系列MCU中的高速外部晶體振盪器,可由下面兩個時鐘源產生:1....

時鐘提取(clock extraction),又稱為時鐘恢復、碼元同步,屬於通信系統中同步(Synchronization)問題。 在接收數字信號時,為了對接收碼元積分以求得碼元的能量以及對每個接收碼元抽樣判決,必須知道每個接收碼元的起止時刻。這就是說在接收端需要...

時鐘發生器是用來產生時鐘信號的器件。常用於數字產品中,產品中所有的組件將隨著所產生的時鐘信號來同步進行運算動作。數字產品必須有時鐘的控制,才能精確處理數位訊號。若時鐘不穩定,輕則造成數位訊號傳送上的失誤,重則導致數字設備無法...

時鐘分配 時鐘分配(clock distribution)是2018年公布的計算機科學技術名詞。定義 在同步數字系統中,把時鐘信號從一個公共的時鐘源同時保真地傳送給所有使用時鐘信號的時序部件的方法和機制。出處 《計算機科學技術名詞 》第三版。

以鎖相環為基礎的時鐘產生結構:外部25MHz的參考時鐘信號或匯流排時鐘(BusCLK)先進入到一個接收緩衝器,在進入鑒頻鑒相器(PFD)之前要經過一個分頻器,分頻係數為M1,得到φi,然後與從分頻器M6來的內部反饋信號Фo在PFD中比較,得到...

1 基準時鐘電路原理 2 性能 3 分類 基準時鐘電路原理 編輯 時鐘信號經過U39分頻以後輸出不同的頻率,分別提供給CPU、晶片組、匯流排、I/0接1:3和存儲器等設備。為主機板各部件工作提供所需的時鐘頻率。當...

時鐘偏移(英語:clock skew)或稱時鐘偏斜,是指時鐘信號到達數字電路各個部分所用時間的差異。對於大多數數字積體電路系統,例如計算機系統,各種信號都是根據系統時間脈衝信號的時鐘頻率進行同步的,這樣這些信號就能在相同的步調上工作。...

脈衝信號可以用來表示信息,也可以用來作為載波,比如脈衝調製中的脈衝編碼調製(PCM),脈衝寬度調製(PWM)等等,還可以作為各種數字電路、高性能晶片的時鐘信號。基本概念 在電子技術中,脈衝信號是一個按一定電壓幅度,一定時間間隔連續...

在內部循環周期小於最壞情況下的內部傳播延遲時,大多數足夠複雜積體電路使用時鐘信號同步電路的不同部分。一些情況下,超過一個時鐘周期需要執行可預測的行為。隨著積體電路變得越來越複雜,向所有電路提供精確且同步的時鐘的問題變得越來越...