應力記憶技術( Stress Memorization Technique,SMT),是90nm邏輯技術節點以下興起的一種著眼於提升NMOS器件速度的應力工程。SMT的特點在於,該技術憑藉拉應力作用,可以顯著加快NMOS器件的電子遷移率,從而提高NMOS器件的驅動電流;然而,SMT在積體電路製造技術中如同一個“隱形人”,在整個工藝流程完成之後,該項技術不會對器件產生任何結構性的變化。

基本介紹

- 中文名:應力記憶技術

- 外文名: Stress Memorization Technique

- 簡稱:SMT

- 套用:NFET,NMOS等

- 優點:有效提高電子輸運性能

- 步驟:多晶矽無定型化,快速退火等

簡介,應力記憶技術的分類,應力記憶的工藝流程,

簡介

應力記憶技術是一種套用於NFET,NMOS等中的局部應力引入技術,可以有效提高電子輸運性能,降低漏電流。應力記憶技術屬於半導體工業應變工程的一種技術手段。該方法可以在半導體器件中引入應力,從而改變半導體中能帶結構,以及電子輸運性能。

這種方法主要包括以下幾個步驟:多晶矽無定型化,沉積具有拉伸應力的襯層,快速退火,襯層移除。雖然拉伸層移除,但是通過退火過程,應力被記憶下來,從而移除襯層之後溝道仍保留應力。這種方法主要適用於n型半導體器件,而不適用於p型器件。

應力記憶技術的分類

在業界早期的探索中,SMT出現了許多流派:

①源、漏極離子注入完成之後,採用低應力水平的膜層(如二氧化矽)作為保護層,對多晶矽柵極進行高溫退火;

②源、漏極離子注入完成之後,採用高應力水平的膜層(如高應力氮化矽)作為保護層,再對多晶矽柵極進行高溫退火‘蹦;

③沉積高應力水平的膜層之後,直接做高溫退火,而不採用預先的離子注入非晶化過程。

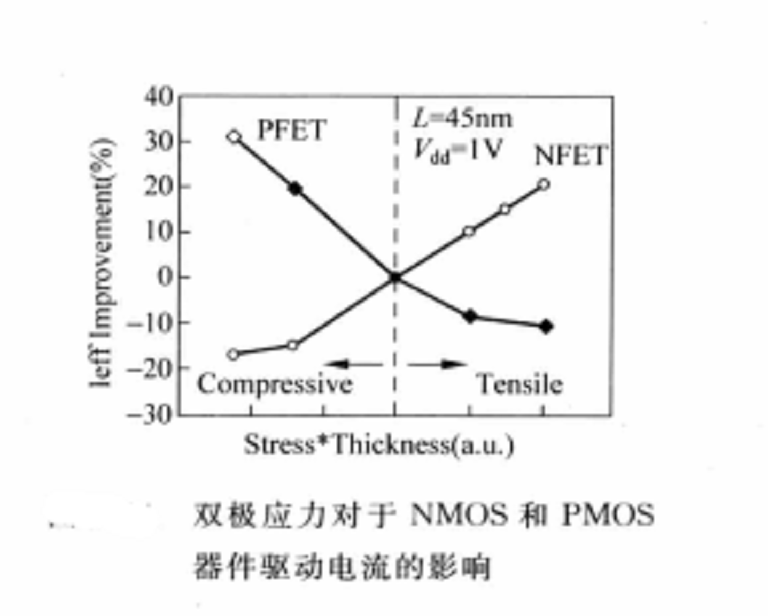

在這三大流派下面,還有很多具體的分支,諸如離子注入的條件差異、應力膜系的選擇、退火條件的不同等。隨著研究的逐步深入以及工業套用的反饋,上述第二種流派被越來越多的業者青睞,已經成為SMT的主流技術。而事實上,在這一分支下,仍有許多探索和實驗在進行。有研究表明傳統的SMT技術會降低PMOS器件的驅動電流,如下圖所示。

相關研究

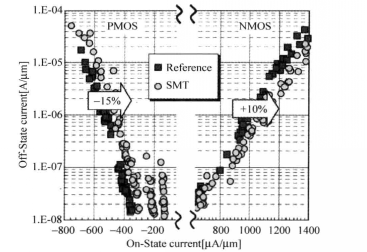

相關研究NMOS速度可以提高10%以上,而PMOS卻有15%的衰減。那么如何解決SMT的這種負面效應呢?研究者再次給出了不同的答案:比較傳統的思路是,在完成高應力膜層(通常是氮化矽)沉積之後,額外增加一層光刻和刻蝕,去除PMOS區域的薄膜,再進行高溫退火。但這種方法會消耗更多的製造成本,而且引入多一層光刻和刻蝕,也會給工藝控制帶來更多的變異,因此有學者提出通過改善應力膜層自身特性的方法,達到既可以提高NM()S的器件速度,又不損傷PMOS性能。

應力記憶的工藝流程

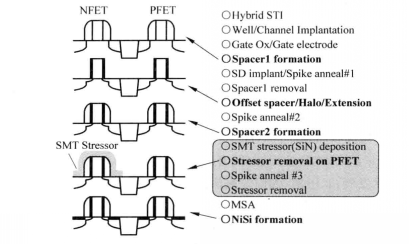

由於傳統SMT對於NMPS器件性能有顯著提升,而對PMOS性能卻有一定程度的損害。通常的思路是選擇性去除PMOS區域的高應力氮化矽,,具體工藝流程如下圖所示

工藝流程

工藝流程SMT實際上是在側牆(spacer)和白對準矽化物(salicidc)之間安插進去的一段獨立的了藝,在做完側牆之後,通常會對源、漏極進行非晶化的離子注入,生長完一層很薄的二氧化矽緩衝層之後,會在整個晶片上沉積一層高應力氮化矽。然後通過一次光刻和乾法刻蝕的工藝,去除掉PMOS區域的氮化矽,通過酸槽洗掉露出來的二氧化矽,接下來就是非常關鍵的高溫退火過程了。因為溫度預算的限制,通常會採用快速高溫退火技術,甚至是毫秒級退火。通常來講,會在第一次尖峰退火(spike anneal)之後,用磷酸將剩餘氮化矽全部去除,再做一次毫秒級退火。但也有人傾向於在兩次退火都做完之後,再去除氮化矽。

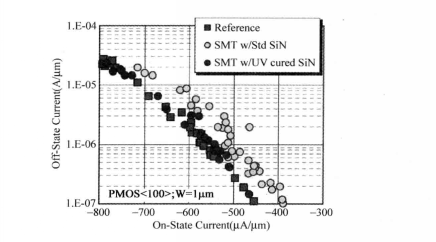

通過改善應力膜層自身特性的方法,達到既可以提高NMOS的器件速度,又不損傷PMOS性能的目的,這種方法由於可以節省一道光刻和刻蝕工藝的消耗,又被稱為低成本應力記憶技術。具體下藝流程如下:在做完側牆之後,會對源、漏極進行非晶化的離子注入,生長完一層很薄的二氧化矽緩衝層之後,再在整片晶片上沉積一層拉應力氮化矽。然後直接進行高溫退火,最後才用磷酸將氮化矽一次性去除。為了減少SMT對PMOS的副作用,氮化矽沉積後加紫外光照射。紫外光照射可以減少氮化矽薄膜中的氫含量,由其引起的硼離子損失(Bloss)得到減輕,因而減少對PMOS的副作用。

改善工藝流程

改善工藝流程總體來講,這兩種方法都有業者在使用,也各有利弊。前一種工藝更為成熟,工藝整合風險低,但存在成本高,工藝複雜的缺點;後一種工藝的優點是丁序簡單,成本更低,但對氮化矽薄膜的工藝要求較高,工藝整合的可靠性還有待時間的驗證。