一種堆疊型Java處理器的流水線設計

針對嵌入式系統特點,設計了一種四段流水線堆疊型Java微處理器核。使用

雙口RAM作為Java棧,減小了存儲資源的消耗。通過硬體在一個時鐘周期內直接執行

Java虛擬機(JVM)中大多數簡單的算術/邏輯指令;通過微代碼模擬在若干時鐘周期內完成中等複雜指令處理;提供硬體陷阱機制,以支持;JVM中非常複雜和面向對象指令的軟體仿真。綜合硬體資源和運行效率兩方面的需求可靈活選擇不同的指令實現方式,為Java處理器在PFGA中的移植實現提供方便。

Java虛擬機及其指令系統

Java是由面向對象語言規範、標準API及Java虛擬機規範構成的系統,其中Java虛擬機是經過

Java編譯器編譯後的位元組碼與目標機之間的標準接口。Java虛擬機指令系統包括大約200條不同的指令,該指令系統與傳統的微處理器指令系統有很大區別,主要表現在:

(1) 面向堆疊:JVM的堆疊的作用類似於RISC處理器中的暫存器,是整個系統數據操作和數據交換的核心,指令默認的源運算元和目的地址都位於堆疊頂部的若干單元,因此消除了指令中的暫存器地址,使得Java程式的平均動態指令長度為1.38個位元組回;

(2) 面向對象的特性:主要包括對象創建、訪問對象域、方法調用和返回、對象類型和異常檢查等面向對象特性的指令 ,這類似於高級語言特性的指令給JVM的硬體移植帶來了較大的困難;

(3)虛擬地址訪問特性:JVM在訪問指令空間和數據空間時都採用虛擬地址,根據指針索引 採用相對定址方式或者字元串匹配的查找方式訪問存儲器。

每個

Java虛擬機執行緒都有它自己的

程式計數器(PC),對應一 個Java棧(Java Stack)。在任何時間,每個Java虛擬機執行一個方法的代碼。該方法是該執行緒的方法。每個Java方法調用將創建一個新的框架(Frame),JVM框架用於存儲數據和部分結果以及進行動態連結、返回方法的值和異常調度。

框架包含的一組稱為它的局部變數的字,可以從該數組的根按照字偏移定址。框架包含的運算元棧是方法的工作棧。另據研究發現JVM中對象訪問指令的動態頻度與運行時間比較都較大,另 外一類複雜指令方法調用與返回指令的動態頻度雖然比較 小,但是占用了較大比例的運行時間,需要進行有效的支持圖。

JVM-0 的流水線設計

JVM指令集中各條指令有很大差別。有一些很簡單的如在棧頂操作的算術和邏輯運算指令,另外也有一些具有高級語言特性的指令例如new和invokestatic這樣的類裝載和校驗指令。由於這些差異性,並非所有的JVM指令都可以移植到硬體中。

在Sun的Java處理器PicoJava一║中使用的一種常用方法就是硬體執行一部分JVM指令,剩下的一些複雜指令通過陷阱(TraP)調用軟體方法執行。

JP一01對於這個問題採用了不同的解決方案。JP一01擁有自己的指令集。有一些指令和JVM指令是一一對應的,可以在一個時鐘周期內完成。對於較為複雜的JVM指令是通過一序列的JP一01指令進行模擬執行,每一個

Java位元組碼指令都對應著一個一 個微碼序列的起始地址(microcode)。另外一 些具有面向對象特性的指令則提供硬體陷阱機制採用軟體方法進行模擬執行。如果位元組碼有對應的JP一01指令,它將在一個周期內執行完成並進行下一個位元組碼的執行。

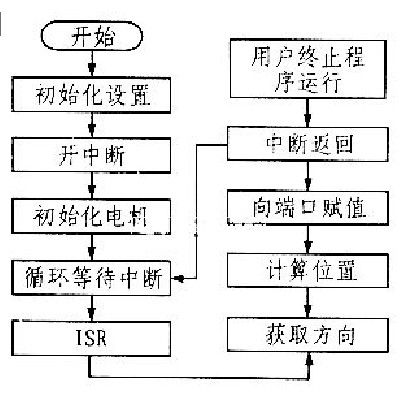

對於較為複雜的位元組碼,JP一01將執行接下來的微碼指令序列。當微碼指令執行結束以後通過一個nextbc。指令返回 ,這個指令翻譯過程需要一段額外的流水線。堆疊結構處理器具有較短的流水線,因此指令分支延遲也較小。

JP一01處理器的流水線是整個流水線設計方案。JP一01核心具有3 段流水線用來執行JP一01指令,另外有一段額外的流水線用來執行

Java位元組碼到微碼序列地址的轉換。每周期可以完成一條JP一01指令。條件轉移指令會引起兩個周期的延遲,為了簡化設計 ,當指令轉移發生或者需要訪問

外部存儲器時採用暫停流水線的處理方式。

該流水線階段從

程式存儲器中取出位元組碼中的JVM指令通過微碼指令查找表獲得對應的微碼序列地址,同時將獲取的可能包含立即數的位元組碼存儲在運算元暫存器中作為運算元使用。流水線第2段獲取JP一01的微碼指令。PJ一01的微碼指令存儲在微碼ROM中。正常執行中微碼指令計數器是遞增的。如果pc指向的下一條指令是nextbc,則表示該微碼指令序列執行結束,需要從第1段獲取新的指令。流水線第3段包括解碼和地址產生兩個功能,對PJ一01微碼指令進行解碼產生控制信號,同時產生讀寫存儲器地址的偏移量,偏移量結合

內部存儲器的堆疊指針或者

外部存儲器中方法的常數池指針、方法區指針從而生成存儲器訪問的物理地址。

流水線第4段是PJ一01微碼指令執行段。由於JVM所有的算術/邏輯操作都是對運算元棧棧頂進行操作,因此將堆疊棧頂(TOS)和次棧頂(TOS一1) 分別作為暫存器A和暫存器B,將A、B作為源操作暫存器,A作為目的暫存器。所有的Laod操作,包括對於局部變數、內部暫存器以及外部存儲器的操作,都將運算元載入A暫存器。因此就不需要租RISC結構處理器中常見的回寫流水線階段。

介紹一種32位微處理機

—MicroVAX 78032晶片

介紹 美國DEC於1985年推出的Micro AX║系統的CPU晶片一Micro VAX78032介紹開發該晶片的背景和設計目標,所採用的壓縮設計的技術途徑,設計過程情況,最終晶片設計,該晶片的功能結構及其物理實現。

壓縮設計的技術途徑

78032設計中的原則問題是怎樣在單個晶片上實現VAX體系結構的複雜性。它具有304條指令的指令系統 ,1 4種數據類型和21種定址方式。指令長度在1位元組到54位元組之間變化。要求請求式頁面

虛擬存儲器支持,以便確保與作業系統軟體的兼容性。為適應這種複雜性 ,在整個一片VLSl VAX實現中要求有1. 25M個電晶體穴位。然而,在設計該晶片時的半導體技術,在單片微處理機中僅能達到其十分之 一。

所有VAX系統中的體系結構功能是按軟體、微碼和作業系統劃分的。所有先前的VAX實現,在這三方面都有相似的邊界。硬體提供暫存器和存儲器,微碼提供指令系統,作業系統提供程式服務。貶要求一個容量很大的

控制存儲器— 最小要有400K位— 以便存放指令微碼。用微碼或 一個支援處理機來處理控制台功能。再者,控制邏輯要支持存儲管理,而可變的指令格式又是相當複雜的。

為減少

微處理機晶片上的電晶體數量,採取了兩種不同的途徑。第一,重新劃分了VAX指令系統,將控制存儲器的容量削減為62K位。第二,通過簡化某些功能,把某些功能併入別的地方,或者省略某個整體部分,來減少片內硬體的數目。

重新劃分指令系統

作為重新劃分的第一步,設計小組假定所有VAX指令都必須實現以執行所有VAX套用軟體為目的。然而,有若干類指令涉及大量微碼但又不經常使用。例如,典型的分時工作負荷是由基本指令、面向科學計算的指令和面向商業的指令處理的。通過對70M次以上的指令執行的分析表明,面向商業的指令僅占總執行數的0.2%。對科學計算和工程設計工作負荷的研究表明,其百分比更低。甚至在商業套用中,面向商用的指令的執行率低於總執行數的4%,多數情況下還是用基本指令。因此,在作業系統中仿真商用指令,而不是採用微碼實現,便有效地縮小了控制存儲器的容量; 但是由於這些指令不經常執行,所以對性能的影響甚微。

另一方面,浮點指令需要大量的微碼,並且經常被執行。在用微碼的情況下,浮點指令的執行速度是相對低的,除非採用單獨的浮點加速器(FPA)。因此,儘管現存的VAX 實現給出微碼執行和硬體浮點二者,設計小組仍然決定不用微碼實現這些指令。取而代之的是用可選的浮點晶片來執行浮點指令,或者用微碼仿真。

總之,用片內微碼實現了304條VAX指令中的175 條,14種數據類型中的6種。其中包括整數和邏輯指令,可變位欄位、控制、佇列、過程調用、字元串傳送、以及作業系統支持。這種微碼指令子集包含了典型程式執行中所用的指令的98%以上。然而,微碼僅占一個完整的VAX實現的

控制存儲器空間1/5的。當使用浮點晶片時,它執行七十條浮點指令和三種數據類型(F、D和G浮點 )。如果不用浮點片,則用微碼仿真這些指令。餘下的59條指令和五種數據類型始終都是用微碼仿真的。其主要是十進制串、字元串和H浮點操作。CPU片為仿真的指令提供某種微碼支持。指令系統歸納了78032晶片的指令系統。

決定用微碼仿真指令,對速度是有影響的,因為仿真指令執行的時間比微碼指令執行時間長三到十倍。但是,這組59條指令是不常用的,它對典型程式的執行速度的降低不超過4%。指令的劃分示出了CPU晶片、FPU晶片和宏代碼之間的指令劃分。最重要的是,由於控制存儲器的容量五倍地縮小,使晶片的工作面積減半。