基本介紹

- 中文名:微處理機晶片

- 外文名:microprocessor chip

- 學科:計算機科學與技術

- 主要類型:8086

- 特點:微型

- 含義:計算機的運算核心和控制核心

基本概念

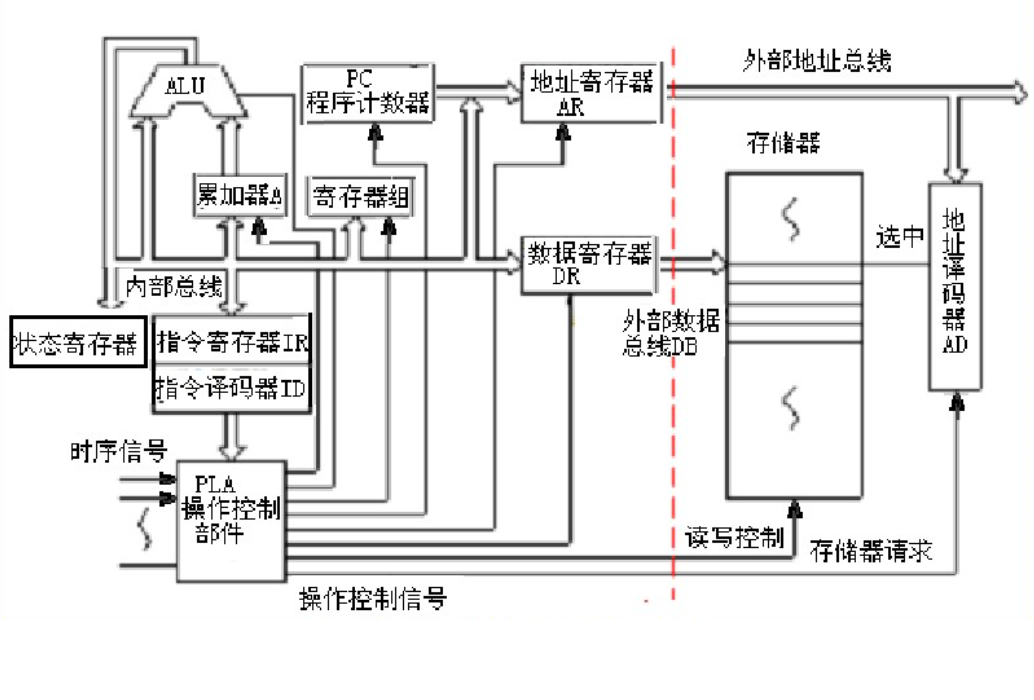

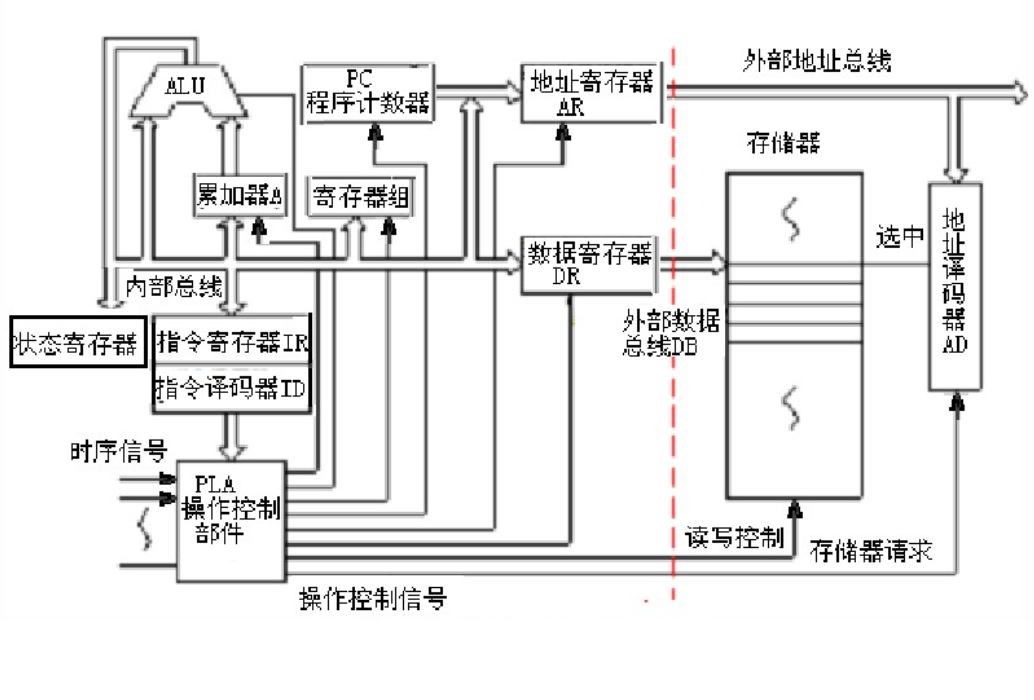

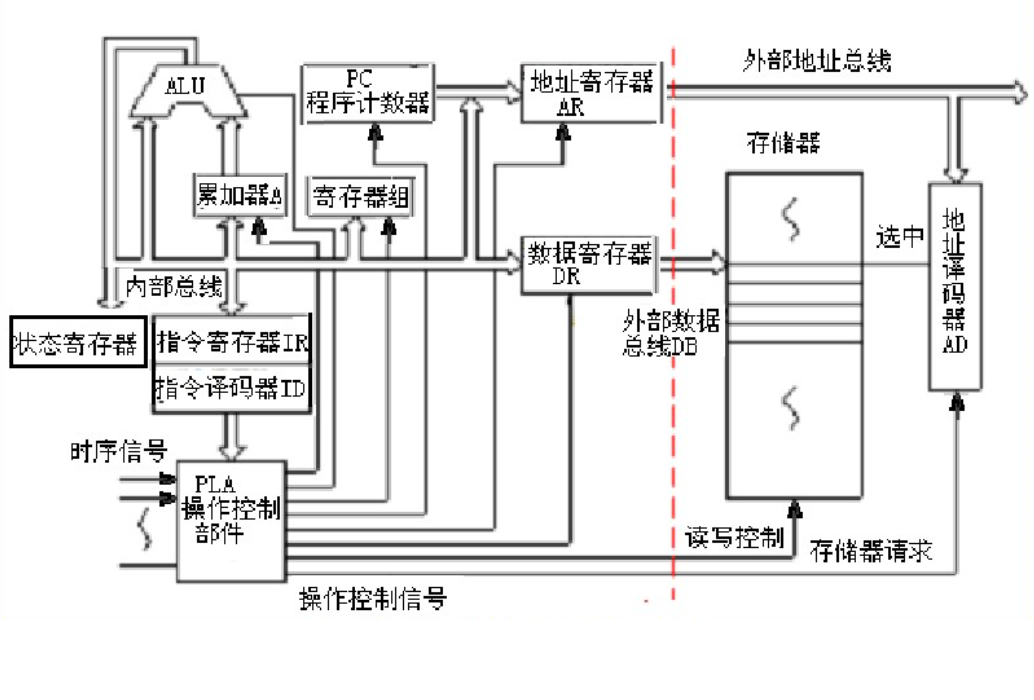

微處理機晶片結構

微處理機(又稱為CPU或中央處理單元)是裝配在單顆晶片上的一個完整的計算引擎。第一顆微處理器是1971年問世的Intel 4004。微處理機能完成取指令、執行指令,以及與外界存儲器和邏輯部件交換信息等操作,是微型計算機的...

ARM處理器是英國Acorn有限公司設計的低功耗成本的第一款RISC微處理器。全稱為Advanced RISC Machine。ARM處理器本身是32位設計,但也配備16位指令集,一般來講比等價32位代碼節省達35%,卻能保留32位系統的所有優勢。定義 ARM的Jazelle...

intel處理器是英特爾公司開發的處理器,即為CPU英特爾公司是全球最大的半導體晶片製造商,它成立於1968年。70年代 微處理器誕生 CPU是Central Processing Unit,就是中央處理器的縮寫,英特爾公司Logo 成立於1968年的英特爾公司,作為全球最...

非x86微處理器 iAPX 432 推出於 1981年1月1日 為 Intel 第一個 32 位 微處理器 Object/capability 架構 Microcoded 作業系統 primitives 1 TB 虛擬可定址空間 硬體支持容錯 兩個晶片的一般數據處理器,包含 43201 和 43202 43203 ...

見於P55C及K6的強大攻勢,Cyrix公司也推出了M2(正式定名為6X86 MX)晶片,按下按鍵你可以看到M2晶片的外觀。Cyrix M2系列CPU是一種高性能的超標量結構微處理器。它專門針對16位和32位的X86軟體進行了最佳化。並配有MMX指令集,兼容Intel...

晶片簡介 簡介 MPU (Microprocessor Unit)微處理器 微機中的中央處理器(CPU)稱為微處理器(MPU),是構成微機的核心部件,也可以說是微機的心臟。它起到控制整個微型計算機工作的作用,產生控制信號對相應的部件進行控制,並執行相應的...

中央處理器是指計算機內部對數據進行處理並對處理過程進行控制的部件,伴隨著大規模積體電路技術的迅速發展,晶片集成密度越來越高,CPU可以集成在一個半導體晶片上,這種具有中央處理器功能的大規模積體電路器件,被統稱為“微處理器”。需要...

鑒於ARM微處理器的眾多優點,隨著國內外嵌入式套用領域的逐步發展,ARM微處理器必然會獲得廣泛的重視和套用。但是,由於ARM微處理器有多達十幾種的核心結構,幾十個晶片生產廠家,以及千變萬化的內部功能配置組合,給開發人員在選擇方案時...

1979年,INTEL公司推出了8088晶片,它仍舊是屬於16位微處理器,內含29000個電晶體,時鐘頻率為4.77MHz,地址匯流排為20位,可使用1MB記憶體。8088內部數據匯流排都是16位,外部數據匯流排是8位,而它的兄弟8086是16位。1981年8088晶片首次用於...

MIPS公司的R系列就是在此基礎上開發的RISC工業產品的微處理器。這些系列產品為很多計算機公司採用構成各種工作站和計算機系統。 MIPS是出現最早的商業RISC架構晶片之一,新的架構集成了所有原來MIPS指令集,並增加了許多更強大的功能。簡介 M...

AMD的AMD-64處理器,在實現與IA-32兼容的同時,支持全64位計算,更展示了強勁的潛力。另外,VIA公司通過購併Cyrix公司,也開始生產與Pentium系列二進制兼容的微處理器晶片。VIA的C3晶片已開始進入桌面系統的低端市場。產品特點 傳統上,...

晶片主機板 AMD和其主機板合作夥伴推出了一系列全新主機板,它們全部採用支持AMD RYZEN的兩款桌面晶片組:X370和X300。PC系統 和全球多家定製化PC製造商攜手推出一系列基於高性能AMD RYZEN處理器的"夢幻電腦"。從獨特外觀的定製化水冷系統到更...

MCS48系列,特別是MCS51系列單片機的出現,確立了單片機作為微控制器(MCU)的地位,引起了微型計算機領域新的變革。在當今世界上,微處理器(MPU)和微控制器(MCU)形成了各具特色的兩個分支。它們互相區別,但又互相融合、互相促進。...

Intel 4004是英特爾製造的一款微處理器,片內集成了2250個電晶體,電晶體之間的距離是10微米,能夠處理4bit的數據,每秒運算6萬次,頻率為108KHZ,前端匯流排為0.74MHz(4bit)。產品簡介 封裝/針腳數量:陶瓷DIP,塑封DIP / 16針 核心...

由於集成了類似於ICE的CPU核心調試技術,所以原型設計和系統晶片的調試得到了極大的簡化。微處理器 ---ARM7:小型、快速、低能耗、集成式RISC核心,用於移動通信。--ARM7TDMI(Thumb):這是公司授權用戶最多的一項產品,將ARM7指令集同...

至強Xeon是英特爾生產的微處理器,它用於"中間範圍"的企業伺服器和工作站。在英特爾的伺服器主機板上,最多達八個Xeon處理器能夠共用100MHz的匯流排而進行多路處理。Xeon設計用於網際網路以及大量的數據處理服務,例如工程、圖像和多媒體等需要...

1978年6月INTEL推出了8086微處理器,主頻4.77MHz,採用16位暫存器、16位數據匯流排和29000個3微米技術的電晶體,標誌著第三代微處理器問世。售價360美元。 不過當時由於360美元過於昂貴,大部分人都沒有足夠的錢購買使用此晶片的電腦,...

奔騰4(Pentium 4,或簡稱奔4或P4)是英特爾公司於2000年11月發布的第7代x86微處理器。並且是繼1995年出品的Pentium Pro之後的第一款重新設計過的處理器,這一新的架構稱做NetBurst。首款產品代碼為:Willamette,擁有1.4GHz左右的...

目前採用RISC體系結構的處理器的晶片廠商有SUN、SGI、IBM的 Power PC系列、DEC公司的Alpha系列、Motorola公司的龍珠和Power PC等等。MIPS體系 MIPS是世界上很流行的一種RISC處理器。MIPS的意思是"無內部互鎖流水級的微處理器"(...

英特爾公司是全球最大的半導體晶片製造商,它成立於1968年,具有41年產品創新和市場領導的歷史。1971年,英特爾推出了全球第一個微處理器。這一舉措不僅改變了公司的未來,而且對整個工業產生了深遠的影響。微處理器所帶來的計算機和網際網路...

2012年2月20日,高通正式將Snapdragon系列處理器的中文名稱定為“驍龍”。驍龍處理器平台是高度集成的移動最佳化系統晶片(SoC),結合了業內領先的3G/4G移動寬頻技術與高通公司自有的基於ARM指令集的微處理器核心,擁有強大的多媒體功能、3D...

1991 年 ARM 公司成立於英國劍橋,主要出售晶片設計技術的授權。採用 ARM技術智慧財產權( IP )核微處理器,即我們通常所說的 ARM 微處理器,已遍及工業控制、消費類電子產品、通信系統、網路系統、無線系統等各類產品市場,基於 ARM ...

微處理器內通過內部匯流排把ALU、計數器、暫存器和控制部分互聯,並通過外部匯流排與外部的存儲器、輸入輸出接口電路聯接。外部匯流排又稱為系統匯流排,分為數據匯流排DB、地址匯流排AB和控制匯流排CB。通過輸入輸出接口電路,實現與各種外圍設備連線。主要...

1971年,Intel 推出了世界上第一款微處理器4004,它是一個包含了2300個電晶體的4位CPU。1978年,Intel公司首次生產出16位的微處理器命名為i8086,同時還生產出與之相配合的數學協處理器i8087,這兩種晶片使用相互兼容的指令集。由於...

無論何時,當微處理器向8259A傳送一條A0=0和D4=1的命令時,這條命令就解碼為ICW1。 A0=0和D4=1是ICW1的標識位! 利用A0=0,D4=1對ICW1定址。(1)ICW1:規定8259的連線方式(單片或級聯)與中斷源請求信號的有效形式(邊沿或...

BOOM: Christopher Celio的RV64亂序處理器實現。Chisel, BSD Licensed。[GitHub][Doc]BottleRocket: RV32IMC微處理器。Chisel, Apache Licensed。 [GitHub]bwitherspoon: RV32微處理器。SystemVerilog, ISC Licensed。[GitHub]Clarvi: ...