專利背景

隨著現代

航空電子的技術發展,航電系統內部設備間要傳輸大量信息,而各設備製造商間接口規範、電氣指標不統一,造成了許多互聯互通的矛盾和衝突。為了解決該問題,由美國各航空電子設備製造商、飛機製造商等機構聯合成立的航空無線電公司,制定了用於航空電子系統通信的工業標準-ARINC429規範。該規範忽略了不同廠家間接口的複雜性,規定了統一的互聯接口技術指標、電器性能和接外掛程式形式,為設備互聯提供了統一的平台。ARICN429匯流排為串列匯流排,採用差分雙絞電纜傳輸信號,傳輸電壓範圍在12±1伏,最高傳輸速率可達到100千比特/秒,工作方式為雙極性歸零模式,傳輸距離較遠,2012年10月之前,中國航空領域多採用ARICN429匯流排實現設備和系統間數據交換。

2012年10月之前的ARICN429匯流排接口模組主要存在以下三個方面的不足之處:

一是通信速率不可變。某些國內大型機載平台,要求航電設備的匯流排傳輸速率根據系統要求可調整。而國內多數ARICN429匯流排接口模組採用單片機和協定晶片方案,若要改變匯流排傳輸速率,需要改變模組的晶振頻率,涉及到模組硬體的改動,兼容性和可維護性不強。

二抗干擾能力較弱。機載設備工作環境複雜,各設備間容易產生電磁干擾。ARINC429匯流排數據傳輸易受到電磁干擾而導致電平出現毛刺、畸變等現象,採樣判決中如果僅ARINC429電平信號進行單次採樣,結果易被干擾而產生錯誤的判決。這要求ARICN429匯流排有足夠的魯棒性,能夠防止突發性電平畸變和毛刺對數據判決的影響,而2012年10月之前ARICN429接口模組由於其硬體結構固定、採樣方法單一,不能有效防止電磁干擾帶來的錯誤判決。

三是通道單一。隨著航電系統的發展設備間交換數據量越來越大,傳統的單一數據通道已無法滿足要求,需研製具有多個收發通道的接口模組,且收發通道間可靈活組合配對。

截至2012年10月,中國採用已有ARICN429匯流排接口都存在進一步的技術升級和功能擴展的需要,均要求通信速率可變,並進一步降低誤碼率,減小模組體積,提高系統的魯棒性和兼容性。

發明內容

專利目的

《多通道ARINC429匯流排接口》的任務是提供一種基於FPGA實現多通道ARINC429匯流排接口,較傳統的429匯流排接口,它具有多通道、參數可配置、多速率選擇、低誤碼、高容錯等特點,特別是能夠滿足航空電子設備間數據通信要求的多通道ARINC429匯流排接口。

技術方案

《多通道ARINC429匯流排接口》包括收發ARINC429匯流排接口模組數據的DSP處理器模組和匯流排驅動模組,其特徵在於,ARINC429匯流排接口模組基於

FPGA實現,DSP處理器模組採用高速數位訊號處理晶片作為主控晶片,完成與ARINC429匯流排接口間數據收發控制和通道參數配置,ARINC429匯流排接口模組具有2個通道控制器,一個提供4路傳送通道數據路徑的傳送通道控制器、一個提供8路接收通道數據路徑的接收通道控制器,DSP處理器模組傳送數據時,首先由傳送通道控制器寫入待傳送的數據和命令信息,選擇傳送通道號和設定傳送速率,在FPGA內部對數據進行處理和組包,在精確時序控制下,將組包後的並行數據轉換成串列數位訊號,送入匯流排驅動模組,經匯流排驅動模組內置的驅動電路匯流排緩衝、電壓比較和波形成形,將數位訊號轉換成符合ARINC429匯流排電平的模擬信號,傳送到預設的傳送通道。DSP處理器模組接收數據過程為以上傳送過程的逆過程。

改善效果

《多通道ARINC429匯流排接口》根據綜合化航空電子設備互聯互通要求,在ARINC429匯流排接口模組中設至少4路數據傳送通道的傳送通道控制器和至少8路數據接收通道的接收通道控制器,實現了多個傳送、接收通道間自由匹配,傳送/接收通道控制器可以任意選擇數據收發通路,大大增加了通信系統的靈活性和可配置性。DSP處理器以中斷方式接收接口模組傳來的數據,保證了接收的實時性和可靠性。

該發明依據ARINC429通信協定規範設定了傳送/接收通道控制暫存器,實現了收發通道的參數化配置。通過命令字可配置數據的奇/偶校驗模式,選擇匯流排傳輸速率(100K/12.5K),通道開關控制等命令,以滿足不同接收端對ARINC429匯流排數據要求,提高了系統的兼容性和可擴展性。

該發明充分利用FPGA的高數據吞吐率、大存儲空間,對基於FPGA實現的ARINC429匯流排接口模組收發數據進行快取,減小了匯流排數據的丟包率。電平採樣引入多次採樣判決機制,匯流排接口模組在晶振輸出的精確時鐘控制下,在FPGA內部採用寬度為5個時鐘周期的滑動判決視窗,對接收到的ARINC429比特電平進行採樣判決,避免了單次採樣的不確定性,經過實驗驗證該方法能夠降低由電磁干擾而引起的傳輸誤碼率。

該發明設計的ARINC429匯流排接口可以推廣套用到使用ARINC429匯流排的航空電子、航天電子、

汽車電子以及工業控制等場合。

附圖說明

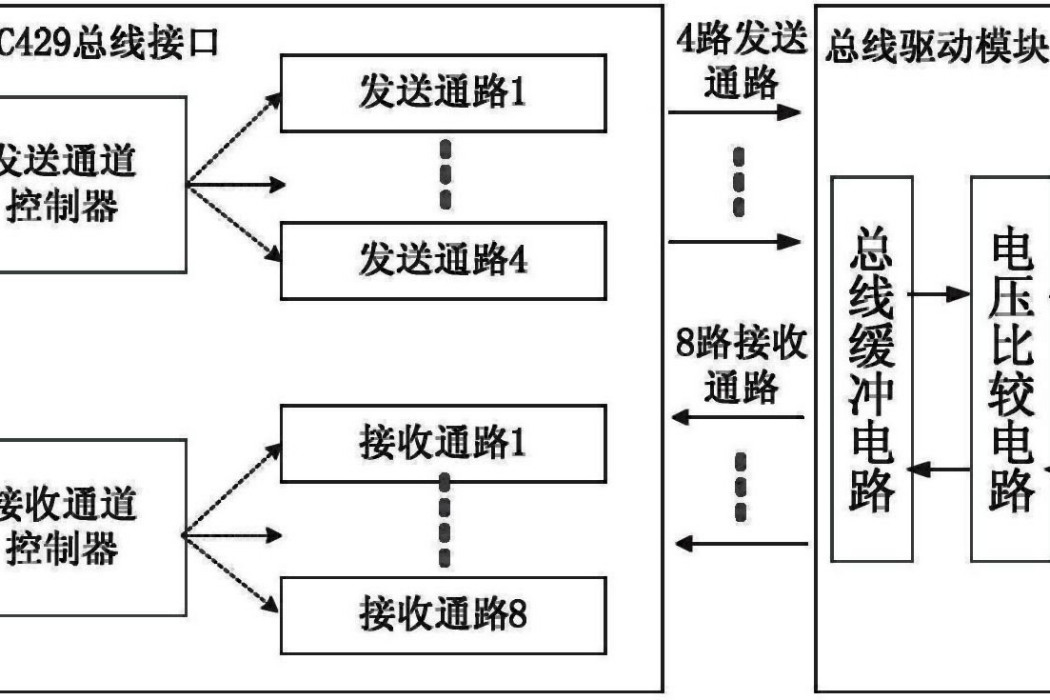

圖1是《多通道ARINC429匯流排接口》的物理組成示意圖。

圖2是該發明ARINC429匯流排電平採樣判決圖。

圖3是該發明多通道ARINC429匯流排接口FPGA數據處理框圖。

圖4是該發明多通道ARINC429匯流排接口數據收發流程圖。

權利要求

1.《多通道ARINC429匯流排接口》包括,ARINC429匯流排接口模組,收發ARINC429匯流排接口模組數據的DSP處理器模組和匯流排驅動模組,其特徵在於,ARINC429匯流排接口模組基於FPGA實現,DSP處理器模組採用高速數位訊號處理晶片作為主控晶片,完成與ARINC429匯流排接口模組間數據收發控制和通道參數配置,ARINC429匯流排接口模組具有2個通道控制器,一個是提供4路傳送通道數據路徑的傳送通道控制器、一個是提供8路接收通道數據路徑的接收通道控制器,DSP處理器模組傳送數據時,首先由傳送通道控制器寫入待傳送的數據和命令信息,選擇傳送通道號和設定傳送速率,在FPGA內部對數據進行處理和組包,在精確時序控制下,將組包後的並行數據轉換成串列數位訊號,送入匯流排驅動模組,經匯流排驅動模組內置的驅動電路匯流排緩衝、電壓比較和波形成形,將數位訊號轉換成符合ARINC429匯流排電平的模擬信號,傳送到預設的傳送通道。

2.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,匯流排驅動模組含有依次串聯的匯流排緩衝電路、電壓比較電路和波形成形電路,由此構成的匯流排驅動模組,完成數位訊號與符合ARINC429匯流排電平的模擬信號間轉換。

3.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,當來自外部ARINC429匯流排模擬信號到來時,先經過匯流排驅動模組電平轉換和匯流排緩衝後,將ARINC429電平特性的模擬信號轉換為FPGA可採樣的兩路ARINC429RX±差分數位訊號,送到FPGA的數據接收端,FPGA接收端檢測到有效數據幀到來後,按預設的匯流排傳輸速率開始接收數據,在FPGA內部完成串並轉換、解碼、接收快取和處理,並在接收完一幀數據後,傳送中斷信號通知DSP處理器模組接收數據。

4.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,DSP處理器模組通過查詢與接收通道相連的中斷處理暫存器判斷接收通道號,調用相應中斷處理函式來接收數據。

5.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,DSP處理器模組按先寫低位再寫高位順序,向傳送通路暫存器寫入寬度為32Bit的待傳送數據,再寫入傳送控制命令。

6.如權利要求5所述的多通道ARINC429匯流排接口,其特徵在於,DSP處理器模組通過寫入數據/命令信息將32Bit的待傳送數據傳送至FPGA,FPGA設定通道參數模組在接收到數據/命令信息後,首先解析命令並按照要求設定通道控制器的傳送通道號、通道開/斷狀態、奇偶校驗模式和數據傳輸速率參數,然後通過內置添加校驗模組對待傳送數據添加校驗信息,將處理後的校驗數據快取至傳送快取模組,再經編碼模組完成數據編碼,通過並串轉換模組將並行數據轉換為串列數據,最後在並串轉換模組嚴格的時鐘控制下,輸出符合ARINC429通信協定的兩路ARINC429TX±差分數位訊號,輸出的差分數位訊號經匯流排驅動模組,將差分數位訊號轉換成符合ARINC429匯流排電平的模擬信號,傳送到預設的傳送通道。

7.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,ARINC429匯流排接口模組在晶振輸出的精確時鐘控制下,在FPGA內部設定了寬度為5個時鐘周期的滑動判決視窗,對接收到的ARINC429比特電平進行採樣判決。

8.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,ARINC429匯流排接口模組接收到數據和命令後,將待傳送數據快取至傳送快取模組中,並解析命令,根據通道控制器要求設定奇偶校驗模式和數據傳送速率,在FPGA內部完成添加校驗、數據編碼和並串轉換。

9.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,FPGA內部採用滑動判決視窗對每個ARINC429比特電平進行採樣,再通過串並轉換模組將串列數據轉換為並行數據,然後經解碼模組對並行數據進行解碼,以32個Bit數據組成一個數據包,將數據包快取至接收快取模組中,通過FPGA內置的數據處理模組完成數據處理後,經中斷信號模組傳送中斷信號,通知DSP處理器模組接收32Bit數據,DSP處理器模組接收中斷信號模組通過查詢而接收到的中斷信號,判斷接收通道號並調用相應的中斷處理程式來接收數據。

10.如權利要求1所述的多通道ARINC429匯流排接口,其特徵在於,通過匯流排驅動模組電平轉換後的ARINC429信號,每個比特流持續時間是100個時鐘周期。

實施方式

參閱圖1。在以下描述的一個最佳實施例中,《多通道ARINC429匯流排接口》包括,DSP處理器模組、ARINC429匯流排接口模組和匯流排驅動模組。DSP處理器模組採用高速數位訊號處理晶片作為主控晶片,完成與ARINC429匯流排接口間數據收發控制、通道參數配置等功能。

ARINC429匯流排接口模組完成匯流排收發通道選擇和配置,設定的傳送通道控制器和接收通道控制器包括4路數據傳送通道、8路數據接收通道,且可通過參數配置收發通路的特性。也就是說ARINC429匯流排接口模組具有2個通道控制器,提供數據路徑的4個傳送通道、8個接收通道,通道控制器來配置各通道參數,如設定通道號、通道開/斷狀態、奇偶校驗模式、數據傳輸速率等。DSP處理器模組傳送數據時,首先由傳送通道控制器寫入待傳送的數據和命令信息,選擇傳送通道號和設定傳送速率,在FPGA內部對數據進行處理和組包,然後在嚴格時序控制下,將組包後的並行數據轉換成串列數位訊號,輸出的串列數位訊號送入匯流排驅動模組,經匯流排驅動模組內置的驅動電路匯流排緩衝、電壓比較和波形成形,將數位訊號轉換成符合ARINC429匯流排電平的模擬信號,傳送到預設的傳送通道。DSP處理器模組數據接收為傳送的逆過程。

匯流排驅動模組含有依次串聯的匯流排緩衝電路、電壓比較電路和波形成形電路,由此構成的匯流排驅動電路,完成數位訊號與符合ARINC429匯流排電平的模擬信號間轉換。 參閱圖2。ARINC429匯流排接口模組在晶振輸出的精確時鐘控制下,在FPGA內部設定了寬度為5個時鐘周期的滑動判決視窗,對接收到的ARINC429比特電平進行採樣判決。圖中,(a)為ARINC429匯流排電平信號(“1010”),為雙極性歸零碼,速率為100千比特/秒;(b)為經電平轉換後的數位訊號;(c)為採樣時鐘信號,頻率為10兆赫,每個ARINC429比特電平持續100個採樣時鐘周期;(d)為FPGA內設定的寬度為5個採樣周期的滑動判決視窗。採用滑動視窗多次採樣機制,對經轉換後的ARINC429匯流排數位訊號進行採樣,降低了判決的誤碼率。具體方法如下:通過匯流排驅動模組電平轉換後的ARINC429信號,每個比特流持續時間是100個採樣時鐘周期。由於採用雙極性歸零碼,只有前50個時鐘周期包含有用信號,FPGA採樣時刻選取有效電平持續時間的中間時刻點,即第25時刻點,作為第一個比特電平最佳採樣點,選作為滑動視窗中心位置,以第25時刻點為中心,前後各取2個採樣點組成視窗元素,在滑動視窗內對第一個比特電平連續進行5次採樣,並記錄下採樣的結果,若結果為’1’的次數大於2次,判定該比特電平為’1’,否則判定為’0’;以此類推,後續三個電平的最佳採樣點位置分別為:第125,225,325時刻點。

如圖2所示,對圖2(a)對電平“1010”採樣,4個滑動視窗的位置分別為:[23..27],[123..127],[223..227],[323..327]。

參閱圖3。FPGA數據處理包括傳送數據處理和接收數據處理兩部分,其中傳送部分實現思路為:DSP處理器模組按先寫低位再寫高位順序,向傳送通路暫存器寫入寬度為32Bit的待傳送數據,再寫入傳送控制命令。DSP處理器模通過寫入數據/命令信息模組將32Bit的數據傳送至FPGA,FPGA設定通道參數模組在接收到數據和指令後,首先解析控制命令並按照要求設定通道控制器的傳送通道號、通道開/斷狀態、奇偶校驗模式、數據傳送速率等參數,然後通過內置添加校驗模組對待傳送數據添加校驗信息,將處理後的校驗數據快取至傳送快取模組中,再經編碼模組完成數據編碼,通過並串轉換模組將並行數據轉換為串列數據,最後在並串轉換模組嚴格的時鐘控制下,輸出符合ARINC429通信協定的兩路ARINC429TX±差分數位訊號,輸出的差分數位訊號經匯流排驅動模組將差分數位訊號轉換成符合ARINC429匯流排電平的模擬信號,傳送到預設的傳送通道。

接收部分實現思路為:當來自外部ARINC429匯流排模擬信號到來時,先經過匯流排驅動模組電平轉換、匯流排緩衝後,將ARINC429電平特性的模擬信號轉換為FPGA可採樣的兩路ARINC429RX±差分數位訊號,送到FPGA的數據接收端,FPGA接收端檢測到有效數據幀到來後,按預設的匯流排傳輸速率開始接收數據,在FPGA內部完成串並轉換、解碼、接收快取和處理,並在接收完一幀數據後,傳送中斷信號通知DSP處理器模組接收數據。具體實現方式如下:

FPGA在檢測到待接收的數據和指令到來後,在晶振輸出的高精度時鐘控制下,採用寬度為5個時鐘周期的滑動判決視窗對每個比特進行採樣,通過串並轉換模組將串列數據轉換為並行數據,然後經解碼模組對並行數據進行解碼,以32個數據組成一個數據包,將數據包快取至接收快取模組中,通過FPGA內置的數據處理模組完成數據處理後,經中斷信號模組傳送中斷信號,通知DSP處理器接收32Bit數據,處理器接收中斷處理模組通過查詢到接收到的中斷信號,判斷接收通道號並調用相應的中斷處理程式來接收數據。

參閱圖4。處理器啟動後,首先運行初始化函式,配置處理器工作方式,包括設定工作頻率、初始化IO口、配置中斷暫存器以接收外部中斷。然後進入主循環,檢測收發通道狀態。當判斷到有待傳送數據時,進入數據傳送流程。首先處理器寫入待傳送數據和控制命令,在FPGA中解析數據,根據控制命令設定數據校驗模式和傳送速率,並按ARINC429協定要求進行數據編碼,最後在嚴格時鐘控制下傳送數據,數據傳送流程結束。

當主循環中檢測到接收數據來時,進入接收流程。首先判斷幀起始信號是否到來,如果未檢測到幀起始信號則繼續等待。當檢測到幀起始信號後開始接收數據,在FPGA中完成串並轉換並對數據進行組包,當一幀數據組包完成後,對該包數據進行處理並傳送中斷信號通知處理器。處理器在收到外部中斷信號後進入中斷處理函式,首先查詢中斷向量暫存器來確定接收通道號,然後往該接收通道寫入讀使能/時鐘信號,再從接收暫存器讀出數據並進行處理,即完成數據接收流程。

榮譽表彰

2021年11月,《多通道ARINC429匯流排接口》獲得2020年度四川專利獎三等獎。