基本介紹

- 中文名:器件隔離

- 外文名:Device Isolation

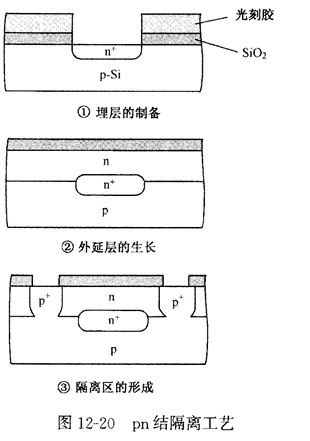

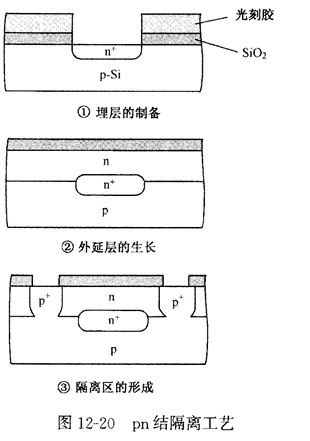

PN結隔離

LOCOS隔離

溝槽隔離

積體電路製造需要某種隔離工藝將單個器件隔離開來。因為半導體積體電路是在同一塊半導體矽片上,通過平面工藝技術製造許多元件和器件(如電阻、電容、二極體、三極體等),...

光電隔離器(optoelectronic isolator,英文縮寫為OC)亦稱光電耦合器、光耦合器,簡稱光耦。光耦合器以光為媒介傳輸電信號。它對輸入、輸出電信號有良好的隔離作用,所以...

介質隔離(Dielectric isolation)技術是積體電路製造中的一種隔離元器件的方法。積體電路是由許多元器件構成的,各個元器件之間往往需要進行電絕緣體—隔離。常用的隔離...

淺槽隔離,即 shallow trench isolation,簡稱STI。通常用於0.25um以下工藝,通過利用氮化矽掩膜經過澱積、圖形化、刻蝕矽後形成槽,並在槽中填充澱積氧化物,用於與矽...

光耦隔離就是採用光耦合器進行隔離。光耦合器的結構相當於把發光二極體和光敏三極體封裝在一起。光耦隔離電路使被隔離的兩部分電路之間沒有電的直接連線,主要是防止...

隔離器是一種採用線性光耦隔離原理,將輸入信號進行轉換輸出。輸入,輸出和工作電源三者相互隔離,特別適合與需要電隔離的設備儀表配用。隔離器又名信號隔離器,是工業...

iCoupler磁耦隔離器是基於晶片尺寸變壓器的磁耦合器,與傳統光耦合器中採用的發光二極體(LED)和光電二極體不同,iCoupler磁隔離技術通過採用晶圓級工藝直接在片上製作...

隔離層,是指為了阻止氣體、液體或固體污染物從其發生地向周圍環境擴散而採取的一系列隔離措施。如使用蓋帽、修建圍堵牆等。蓋帽是指將阻隔性屏障或其他無污染的清潔...

磁耦隔離,是防止電流在兩通訊之間流動的一種方法,保護電路不受危險電壓和電流的損壞。通過隔離電路進行隔離。一般情況下,一個隔離器件的隔離能力的通常描述參數是...

隔離放大器是一種特殊的測量放大電路,其輸入、輸出和電源電路之間沒有直接電路耦合,即信號在傳輸過程中沒有公共的接地端。輸入電路和放大器輸出之間有歐姆隔離的器件...

光隔離器是一種只允許單向光通過的無源光器件,其工作原理是基於法拉第旋轉的非互易性。 通過光纖回波反射的光能夠被光隔離器很好的隔離。光隔離器主要利用磁光晶體...

隔離開關(Isolating switch)是一種主要用於“隔離電源、倒閘操作、用以連通和切斷小電流電路”,無滅弧功能的開關器件。隔離開關在分位置時,觸頭間有符合規定要求的...

信號隔離器是一種信號隔離裝置,將輸入單路或雙路電流或電壓信號,變送輸出隔離的單路或雙路線性的電流或電壓信號,並提高輸入、輸出、電源之間的電氣隔離性能。...

隔離二極體:顧名思義,利用二極體的單嚮導通原理,對某方向電壓的導通起到隔離的作用。隔離二極體一般情況下正嚮導通電壓在0.6~0.8V之間(矽二極體)。...

反向隔離是對加到器件輸出端的信號與其輸入端隔離程度的量度 , 是反射信號對正方向上所要的基本信號流的干擾的衡量。...

電子元器件是電子元件和電小型的機器、儀器的組成部分,其本身常由若干零件構成,可以在同類產品中通用;常指電器、無線電、儀表等工業的某些零件,如電容、電晶體、...

智慧型隔離器又名信號隔離器,是一種採用線性光耦隔離原理將輸入信號進行轉換輸出。一般由輸入信號處理單元、隔離單元、輸出信號處理單元、電源等4部份構成。...

《元器件》是2009年電子工業出版社出版的圖書,作者是姚金生。本書介紹了對某些元器件的修理方法以及常用元器件的參數等,對我們的生活有很大的便利。...

直流大電流隔離器的原理是首先將變送器或儀表的信號,通過半導體器件調製變換,然後通過光感或磁感器件進行隔離轉換,然後再進行解調變換回隔離前原信號,同時對隔離後...

光纖隔離器,通信術語,用來保持光源譜純度的光纖器件。...... 光纖隔離器,通信術語,用來保持光源譜純度的光纖器件。中文名 光纖隔離器 性質 通信術語 ...

隔離式電源是指輸入和輸出通過變壓器等磁性元器件電氣連線的...... 隔離式電源是指輸入和輸出通過變壓器等磁性元器件電氣連線的,即使將輸出短路也不會有太大問題,而...