同步狀態機相對於控制器,它將一項功能完成分成若干步驟,每一步對應於一個二進制的狀態。

基本介紹

- 中文名:同步狀態機

- 領域:計算機

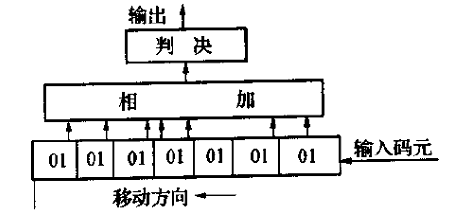

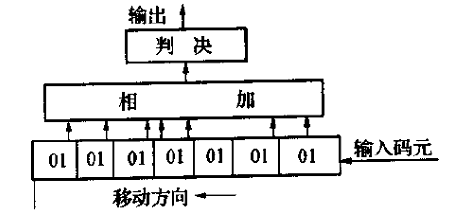

同步狀態的搜尋與接收系統定時

圖1

圖1 圖2

圖2同步狀態轉移分析

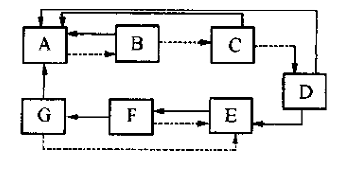

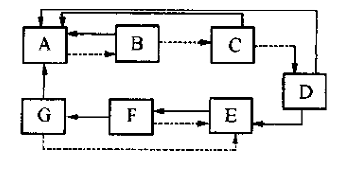

圖3

圖3狀態機的控制與編碼

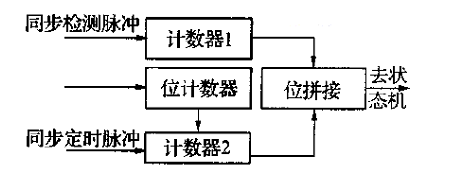

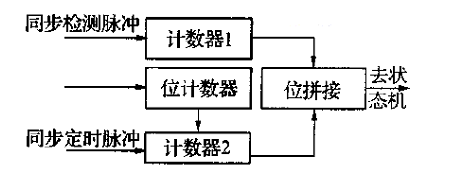

圖4

圖4同步狀態機相對於控制器,它將一項功能完成分成若干步驟,每一步對應於一個二進制的狀態。

圖1

圖1 圖2

圖2 圖3

圖3 圖4

圖4同步狀態機相對於控制器,它將一項功能完成分成若干步驟,每一步對應於一個二進制的狀態。...

狀態機由狀態暫存器和組合邏輯電路構成,能夠根據控制信號按照預先設定的狀態進行狀態轉移,是協調相關信號動作、完成特定操作的控制中心。有限狀態機簡寫為FSM(Finite ...

在計算機科學領域,狀態機複製或狀態機方法是實現容錯服務的一種常規方法,主要通過複製伺服器,並協調客戶端和這些伺服器鏡像間的互動來達到目標。這個方法也同時提供了...

首先,狀態機的輸出往往是由狀態位組合生成的。同時變化的狀態位越多,組合輸出穩定前所需的時間就越長,產生的毛刺就越多。如果該輸出不經同步就直接連線到暫存器的...

《基於狀態機的嵌入式系統開發》是2010年清華大學出版社出版的圖書,作者是楊剛。該書講述了嵌入式系統及狀態機方面的知識。...

引入同步有限狀態機,並進一步探討了同步狀態機的特徵;第6章則詳細介紹了VerilogHDL的仿真技術,並對ModelSim軟體進行了介紹;第7章介紹了幾則實用的可綜合的設計;第8...

5.3 時鐘同步狀態機分析 5.3.1 狀態機結構 5.3.2 輸出邏輯 5.3.3 特徵方程 5.3.4 使用D觸發器的狀態機分析 5.4 時鐘同步狀態機設計 5.4.1 狀態表設...

4. 1 時鐘同步狀態機的設計 84 4. 1. 1 時鐘同步狀態機及其設計流程 84 4. 1. 2 時鐘同步狀態機設計方法構建序列發生器 86 4. 1. 3 狀態圖直接描述法...

11.4 在Verilog HDL設計中啟用同步時序邏輯11.5 數據接口的同步方法小結思考題第12章 同步狀態機的原理、結構和設計概述12.1 狀態機的結構...

4.3 設計同步狀態機4.4 SRAM的設計4.5 複雜數字邏輯設計4.6 設計示例:UART4.7 可綜合的Verilog RTL設計4.8 代碼書寫風格4.9 習題參考文獻...

3.4 同步狀態機的原理與設計3.4.1 什麼是狀態機3.4.2 狀態機的設計原理3.4.3 典型的狀態機實例3.5 Verioog HDL可綜合的代碼風格...

4.4 有限同步狀態機 100 本章小結 110 思考題和習題 110 第5章 仿真驗證與Testbench編寫 113 5.1 Verilog HDL電路仿真和驗證概述 113 5.2 Verilog HDL測試程...