反向設計介紹

反向設計其實就是晶片反向設計,它是通過對晶片內部電路的提取與分析、整理,實現對晶片技術原理、設計思路、工藝製造、結構機制等方面的深入洞悉,可用來驗證設計框架或者分析信息流在技術上的問題,也可以助力新的晶片設計或者產品設計方案。

在晶片反向設計領域,世紀芯長期晶片電路修改、網表/電路圖反向提取、電路層次化整理、邏輯功能分析、版圖提取與設計、設計規則檢查調整、邏輯版圖驗證、單元庫替換以及工藝尺寸的縮放等技術服務。通過這些逆向分析手段,我們可以幫助客戶了解其他產品的設計,用於項目可行性研究、打開思路、尋找問題、成本核算等,比如:在進入新領域之前,評估、驗證自己技術方案和設計思路的可行性;通過對市場上成熟產品的研究,協助解決關鍵性的技術問題;利用已有產品的市場資源,降低進入壁壘,實現更好的產品兼容性等等。

電路修改

我們利用先進的聚焦離子束機(FIB)通過刻蝕和沉積的方法能夠修改多層布線的

積體電路晶片。主要服務項目包括

積體電路晶片引線修改(能夠修改最小工藝為90nm);積體電路晶片材料和成分鑑定;微電路故障分析(最小尺寸為40nm);製作納米級的光電子器件、生物感測器件和超到電子器件等。

網表/電路圖提取

在晶片反向工程中,網表/電路圖提取是非常重要的工作。網表提取的質量和速度直接影響後面整理、仿真和LVS等方方面面的工作。

世紀芯在長期的技術研究中已經成功總結了一套切實可行的規範和方法,可以高質量高速度的提取各種類型電路的網表。如:

| 數字電路

| 模擬電路

|

設計服務範圍

| 標準單元、門陣列、半定製和全定製

| COMS工藝和Bi-poly工藝

|

服務內容

| 提供頂層級和單元級(門級)兩個層次電路圖,如下圖所示。可按版圖布局生成電路圖;提供ERC校驗和支持SVS流程;

| 提供管子級網表/電路圖; 涵帶電晶體寬長比等幾何參數;按版圖布局生成電路圖;提供ERC校驗和支持SVS流程

|

數據交付

| 數據格式:Verilog和EDIF

提供圖像數據、原始網表數據、按版圖位置生成的兩個層次的電路圖

| 數據格式:SPICE和EDIF

提供圖像數據、原始網表數據、按版圖位置生成的兩個層次的電路圖

|

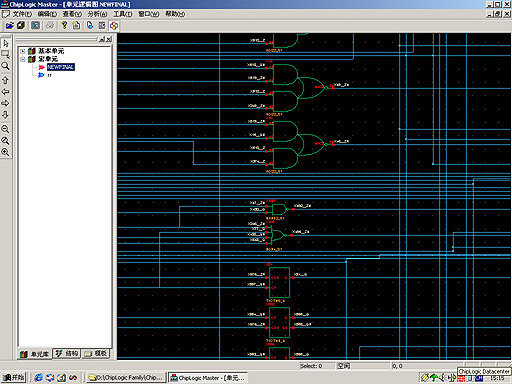

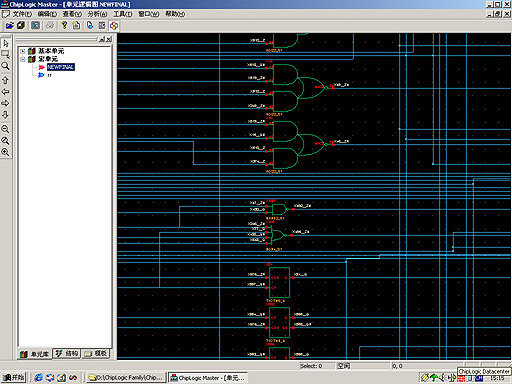

邏輯功能分析

網表提取結束後,往往需要進行電路的整理工作,把一個打平(flatten)的電路進行層次化(hiberarchy)整理,形成一個電路的層次化結構,以便理解設計者的設計思路和技巧,同時還能達到查找網表錯誤的目的。

世紀芯通過對電路的各個層次模組的整理和分析,不僅可以充分理解晶片設計者的設計思想和設計技巧,還可以在分析總結先進設計思路的基礎上實現自身設計能力的提高。

世紀芯擁有先進的邏輯功能分析軟體,可達到高效準確的分析效果。

邏輯功能分析器:

邏輯功能分析

邏輯功能分析其主要優勢表現在:

☆電路圖自動生成和瀏覽。軟體可讀入Verilog等多種格式的網表檔案,根據網表描述的邏輯關係自動生成可視化的電路圖。並且用戶可以快速瀏覽局部電路圖,進行器件選擇和線網擴展。

☆內置完備的單元符號庫。系統提供的單元符號庫包含了常用單元的符號圖,可以省去用戶編輯單元符號圖的工作。

☆強大的線網分析功能。用戶既可以指定任何一個線網以標號方式顯示,來簡化電路圖,又可利用線網統計分析功能找出某些特徵線網,指導電路分析。

☆完善的ERC電學規則檢查。電學規則檢查包括輸入端懸空、輸出端短路、無用器件等檢查等項目,ERC錯誤發現後可直接定位到版圖進行修正。

☆支持各種常用

檔案格式,能夠輸出Verilog、SPICE和EDIF等格式檔案。

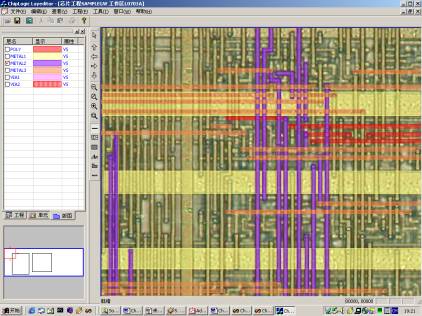

版圖設計

版圖設計是電路邏輯的物理實現,是積體電路產品實現(ChipLogic Layeditor)。世紀芯在反向設計的基礎上提供版圖的提取、工藝庫替換、目標工藝修改、DRC檢查和LVS校驗等各種設計服務。

為最大限度方便版圖設計,世紀芯專門引進了先進的版圖編輯器,該編輯器主要功能優勢表現在:

(1)版圖編輯器除了提供常用的版圖編輯功能外,還能夠直接

顯示晶片圖像,從而保證版圖提取的精確性。同時顯示多層晶片圖像,大大提高引線孔識別的準確度。

(2)提供自動化的單元識別和引線識別功能,大大提高版圖的提取效率。通過提取圖像特徵值,軟體能夠自動識別出重複放置的單元,並支持X方向和Y方向鏡像放置和90度旋轉放置,引線和引線孔的自動識別功能,準確率在90%以上。

(3)支持整體縮放功能,適應工藝參數修改。支持GDSII和CIF等標準格式,能夠直接導入Cadence、Synopsys等廠商的版圖工具。

(4)提供設計規則檢查功能,既可以使用本軟體進行DRC(設計規則檢查),也可以將版圖導入Cadence和Synopsys等廠商的版圖工具進行DRC。

(5)電學規則檢查ERC可發現大部分錯誤,顯著提高準確率。進一步提高準確率可通過分組對比校驗,即分兩組同時進行版圖提取並進行SVS。

(6)支持百萬門級電路的版圖提取。支持標準單元電路和全定製電路。

(7)網路分布支持,多個用戶可以同時提取版圖,軟體保證完全無縫的多用戶協調。

邏輯版圖驗證

網表和版圖設計結束後,往往需要對其正確性進行各種驗證,為了保證設計流程的完整性,需提供晶片網表數據和版圖數據的各種驗證服務:

| 驗證類別

| 內 容

|

1

| FPGA驗證

| 通過燒制晶片來驗證邏輯提取的正確性

|

2

| 邏輯仿真驗證

| 根據客戶提供的晶片相關說明編寫測試向量來驗證邏輯提取的正確性

|

3

| LVS驗證

| 版圖和網表的一致性驗證

|

邏輯功能分析

邏輯功能分析