基本介紹

- 中文名:低電平

- 外文名:Vil

- 主要套用:測量電纜和保護連線

定義

輸入

輸出

套用簡介

對測量電纜的要求

測量常用連線器類型

BNC連線器

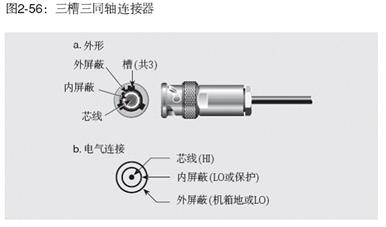

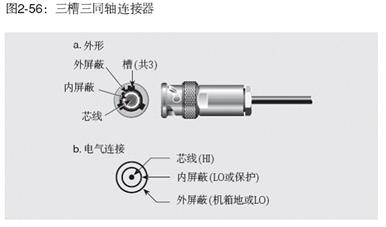

BNC連線器 三槽三同軸連線器

三槽三同軸連線器

BNC連線器

BNC連線器 三槽三同軸連線器

三槽三同軸連線器低電平(Vil)指的是保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低於Vil時,則認為輸入電平為低電平。...

所謂電平,是指兩功率或電壓之比的對數,有時也可用來表示兩電流之比的對數。電平的單位分貝用dB表示。常用的電平有功率電平和電壓電平兩類,它們各自又可分為絕對...

低電平有效的意思就是說,一個廣義的理想開關,其常態為閉合狀態,也就是常保持1信號,當給其0信號時(也就是斷開此開關),這個開關將會觸發下級電路。...

高電平,指的是與低電平相對的高電壓,是電工程上的一種說法。在邏輯電平中,保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高於輸入高電壓(Vih)...

低電平開機,主機板開機鍵觸發主機板開機電路工作,開機電路將觸發信號進行處理,最終向電源第14腳發出低電平信號,將電源的第14腳的高電平拉低,觸發電源工作,使電源各引腳...

邏輯電平是指一種可以產生信號的狀態,通常由信號與地線之間的電位差來體現。邏輯電平的浮動範圍由邏輯家族中不同器件的特性所決定。...

電平信號是指用電平值表示的信號 ,電平值分為高電平“1”和低電平值”0”。...... 電平信號 [1] 是指用電平值表示的信號 ,電平值分為高電平“1”和低電平...

TTL電平信號規定,+5V等價於邏輯“1”,0V等價於邏輯“0”(採用二進制來表示數據時)。這樣的數據通信及電平規定方式,被稱做TTL(電晶體-電晶體邏輯電平)信號系統...

負邏輯(Negative Logic)是相對正邏輯(Positive Logic)而言的,廣義上來講,和規定邏輯相反的邏輯可以稱為負邏輯或反邏輯;更多用於數字電路領域,將高電平對應邏輯為0,...

三態門(Three-state gate)亦稱“三態輸出門”、“三態門輸出電路”。是一種重要的匯流排接口電路。具有高電平、低電平和高阻抗三種輸出狀態的門電路。主要有電晶體-...

A0~A2對應Y0——Y7;A0,A1,A2以二進制形式輸入,然後轉換成十進制,對應相應Y的序號輸出低電平,其他均為高電平。 [1] 74LS138內部邏輯圖 編輯 74LS138的內部...

在GJB1217“電連線器試驗方法”中規定有“低電平接觸電阻” 和“接觸電阻”兩種試驗方法。其中低電平接觸電阻試驗方法基本內容與上述GB5095中的接觸電阻-毫伏法相同...

當任一輸入端(或多端)為高電平(邏輯“1”)時,輸出就是低電平(邏輯“0”);只有當所有輸入端都是低電平(邏輯“0”)時,輸出才是高電平(邏輯“1”)[1] 。...

當選通端(G1)為低電平,可將地址端(A、B)的二進制編碼在一個對應的輸出端以低電平譯出。 實物圖 若將選通端(G1)作為數據輸入端時,139 還可作數據分配...

0-7 編碼輸入端(低電平有效)EI 選通輸入端(低電平有效)A0、A1、A2 三位二進制編碼輸出信號即編碼 輸出端(低電平有效)GS 片優先編碼輸出端即寬展端(低電平...

非門(英文:NOT gate)又稱非電路、反相器、倒相器、邏輯否定電路,簡稱非門,是邏輯電路的基本單元。非門有一個輸入和一個輸出端。當其輸入端為高電平(邏輯1)時...

上拉就是將不確定的信號通過一個電阻嵌位在高電平,電阻同時起限流作用。而下拉電阻的設定的原則和上拉電阻是一樣的。下拉電阻是直接接到地上,接二極體的時候...

普通調幅信號的產生可將調製信號與直流相加,再與載波信號相乘,即可實現普通調幅。可採用低電平調幅方法和高電平調幅方法。調幅解調方法 ...

由允許信號E控制輸出,當E=1為高電平時,電路的功能是一個正常的緩衝驅動器。輸出根據輸入為低電平或高電平則相應為低電平和高電平。當E=0為低電平時,不論輸入...

與非門是與門和非門的結合,先進行與運算,再進行非運算。與非門是當輸入端中有1個或1個以上是低電平時,輸出為高電平;只有所有輸入是高電平時,輸出才是低電平。...

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。上拉是對器件輸入電流,下拉是...

若兩個輸入的電平相異,則輸出為高電平1;若兩個輸入的電平相同,則輸出為低電平0。即如果兩個輸入不同,則異或門輸出高電平1。中文名 異或門 外文名 Exclusive...

與非門(英語:NAND gate)是數字電路的一種基本邏輯電路。若當輸入均為高電平(1),則輸出為低電平(0);若輸入中至少有一個為低電平(0),則輸出為高電平(1)。...

電壓比較器的功能:比較兩個電壓的大小(用輸出電壓的高或低電平,表示兩個輸入電壓的大小關係):當”+”輸入端電壓高於”-”輸入端時,電壓比較器輸出為高電平;當...