計算機體系結構是指根據屬性和功能不同而劃分的計算機理論組成部分及計算機基本工作原理、理論的總稱。並行性是指計算機系統具有可以同時進行多於兩個運算或操作。並行體系結構是指許多指令能同時進行的體系結構,一般從時間和空間兩方面考慮。

基本介紹

- 中文名:並行體系結構

- 外文名:Parallel architecture

- 學科:計算機

- 定義:許多指令能同時進行

- 分類:Flynn分類法、馮式分類法

- 領域:體系結構

計算機體系結構是指根據屬性和功能不同而劃分的計算機理論組成部分及計算機基本工作原理、理論的總稱。並行性是指計算機系統具有可以同時進行多於兩個運算或操作。並行體系結構是指許多指令能同時進行的體系結構,一般從時間和空間兩方面考慮。

計算機體系結構是指根據屬性和功能不同而劃分的計算機理論組成部分及計算機基本工作原理、理論的總稱。並行性是指計算機系統具有可以同時進行多於兩個運算或操作。並行體系結構是指許多指令能同時進行的體系結構,一般從時間和空間兩方面...

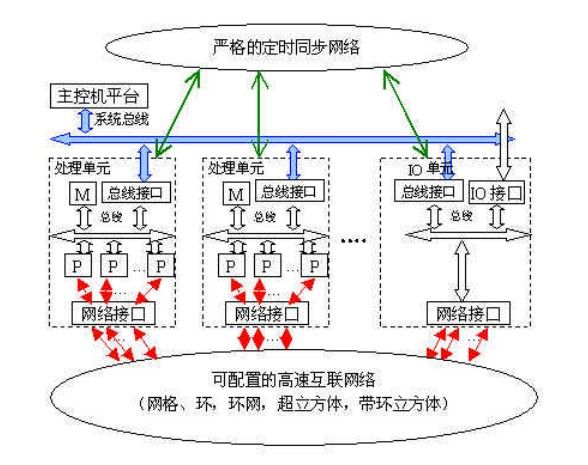

並行計算機的分類及基本結構(採用擴展的Flynn分類):1. SIMD(單指令多數據流)SM--Vector Pipelined 向量流水計算機 DM--Processor Array SIMD陣列機 2. MIMD(多指令多數據流)SM--SMP(UMA) 對稱式多處理機 UMA Uniform-memory-access ...

《並行機體系結構(網路版)》介紹了並行計算機體系結構的基本概念、基本原理、基本分析和設計方法。《並行機體系結構(網路版)》共9章,內容包括:計算機體系結構的相關概念、時間並行技術、指令級並行技術、向量處理機、互連網路、陣列處理機...

《並行計算機體系結構(第2版)》是2021年高等教育出版社出版的圖書。內容簡介 本書以當代可擴放的並行計算機系統結構為主題,從硬體和軟體融合的角度,著重討論了集中式共享存儲系統、分散式共享存儲系統、訊息傳遞並行處理系統、異構並行...

《並行計算機系統結構與可擴展計算》是清華大學出版社2009年2月1日出版的圖書,作者是古志民。作者簡介 古志民,北京理工大學計算機科學技術學院教授、博士生導師、學術委員、北京理工大學一美國伊利諾伊理工學院(BIT-IIT)可擴展計算聯合實驗...

《新的並行算法及面向新的並行算法的新型並行體系結構》是依託北京科技大學,由高慶獅擔任項目負責人的面上項目。項目摘要 要巨型機有效解決國防和國民經濟建設的計算問題,關鍵是把被計算的問題(特別是本來屬於串列計算問題)進行並行化。

《並行多核體系結構基礎》是2018年北京機械工業出版社出版的圖書,作者是湯孟岩。內容簡介 並行編程和性能調優對許多程式設計師而言已經成為不可或缺的能力。本書以問題為引導, 系統地講解了並行多核體系結構中的根本問題。第一部分 (第2-4...

並行系統聯合體(Parallel Sysplex)是系統聯合體的增強版,它用於較新的作業系統OS/390。根據IBM,並行系統聯合體是IBM多年來大型系統開發的最終結果。並行系統聯合體是一個聚合體系結構,它增強了通信能力,支持連線更多的中央處理器聯合...

《高效能並行計算機體系結構研究》是依託中國人民解放軍國防科技大學,由周興銘擔任項目負責人的重點項目。 中文摘要 超高性能計算機面臨重大技術挑戰,其體系結構處在重大變革時期。本項目面向國家重大科學計算需求,研究千萬億次高效能並行...

《並行計算機體系結構技術與分析》是2009年1月1日科學出版社出版的圖書,作者是楊曉東、陸松、牟勝梅。該書可作為高等院校相關領域的教師和研究生的教學參考書,也可供相關科研人員閱讀。內容簡介 本書以研製高性能計算機系統為線索,對...

本書正是以此技術為背景,通過大量的實例,精確的數據和作者對並行結構深邃的理解向人們提示了蘊藏於並行體系結構中的強大力量,並同時首次對設計的平衡性能做了充分的定量評估。本書用硬體、軟體方面的*技術對並行結構設計中的若干重大問題...

在並行計算系統體系結構方面,主要研究面向大數據的高性能加速處理器結構和大數據的可擴展異構並行計算體系結構;在混合主存系統方面,主要研究面向大數據的流式高並發主存結構和混合主存的數據管理最佳化機制;在並行處理的軟體支撐方面,主要研究...

該書共八章,內容包括計算機系統結構的相關概念、時間並行技術、指令級並行技術、向量流水處理機、互連網路、陣列處理機、多處理機、課程設計實驗。圖書目錄 第一章 計算機體系結構的相關概念 第二章 時間並行技術 第三章 指令級並行...

為利用並行計算,通常計算問題表現為以下特徵:(1)將工作分離成離散部分,有助於同時解決;(2)隨時並及時地執行多個程式指令;(3)多計算資源下解決問題的耗時要少於單個計算資源下的耗時。基本體系結構 並行計算科學中主要研究的是...

隨著對並行計算技術研究的深入和SMP、MPP等處理機技術的發展,並行資料庫的研究也進入了一個新的領域,集群已經成為了並行資料庫系統中最受關注的熱點。並行資料庫領域主要還有下列問題需要進一步地研究和解決。(1)並行體系結構及其套用,...

本質上的並發性支持,這種體系結構由於本質上是與各個獨立的過濾器的狀態無關的,與並行的流的通過次序也是無關的,所以並發是一個基本的體系結構自然具有的特性。缺點:由於過濾器之間本質上是獨立的,所以設計者必須獨立考慮每一個過濾...

(1)計算機系統概論;(2)運算方法和運算器;(3)內部存儲器;(4)指令系統;(5)中央處理機;(6)匯流排系統;(7)外圍設備;(8)輸入/輸出系統;(9)作業系統支持;(10)安騰高性能處理機體系結構;(11)並行體系結構...

隨著社交網路的興起,基於大規模圖結構上的計算、分析與挖掘,成為具有重要理論意義和套用價值的研究熱點。本項目面向大規模圖結構數據,研究如何高效處理,檢索、分析與套用。研究主要分為四個方面:(1)基於並行體系結構的大圖劃分與子圖...

遺傳算法使我們有可能開發出駐留在大型並行生物計算機上的軟體。原理 計算機體系結構解決的是計算機系統在總體上、功能上需要解決的問題,它和計算機組成、計算機實現是不同的概念。一種體系結構可能有多種組成,一種組成也可能有多種物理...

體系結構 相對於串列計算,並行計算可以劃分成時間並行和空間並行。時間並行即流水線技術,空間並行使用多個處理器執行並發計算,當前研究的主要是空間的並行問題。以程式和算法設計人員的角度看,並行計算又可分為數據並行和任務並行。數據...

並行計算機以追求高性能為目標,但同時也增大了晶片面積和硬體單元的互連開銷,進而帶來了功耗的增加。在體系結構級研究並行計算機系統的功耗,對設計擁有自主智慧財產權的面向特定套用的高性能低功耗計算機系統有著重要的支撐作用。.本項目面向...

要想適應新的問題推的需要,使計算效率有根木的提高,那就只有呆用一種絕然不同的計算機體系結構,以擺脫指令和數據串列處理的“馮諾依曼瓶預”,當然還要改變現行的程式設計語言。計算機體系結構,如以並行處理原理為基礎,在結構上就具有...

《支持推測並行化的多核事務儲存體系結構研究》是科學出版社出版的圖書,作者是王耀彬。內容簡介 隨著多核平台的普及,如何利用多核加速串列套用的執行已成為國際學術界和工業界共同關注的熱點研究問題。《支持推測並行化的多核事務儲存體系...

《支持推測並行化的多核事務存儲體系結構研究》是2014年科學出版社出版的圖書。內容簡介 隨著多核平台的普及,如何利用多核加速串列套用的執行已成為國際學術界和工業界共同關注的熱點研究問題。《支持推測並行化的多核事務存儲體系結構研究...

《多核體系結構下並行套用的性能評測與最佳化技術研究》是依託北京套用物理與計算數學研究所,由張寶印擔任項目負責人的青年科學基金項目。項目摘要 本項目以三類典型的並行科學計算套用(分子動力學、能量方程和中子輸運方程)為背景,研究多核...

高性能計算(High performance computing, 縮寫HPC) 是利用超級計算機實現並行計算的理論、方法、技術以及套用的一門技術科學,圍繞利用不斷發展的並行處理單元以及並行體系架構實現高性能並行計算這一核心問題,該領域研究範圍包括並行計算模型...

分散式處理(distributed processing)和並行處理(Parallel processing)是為了提高並行處理速度採用的兩種不同的體系架構。並行處理是利用多個功能部件或多個處理機同時工作來提高系統性能或可靠性的計算機系統,這種系統至少包含指令級或指令級...