基本介紹

- 中文名:並行同步計算機

- 外文名:parallel synchronous computer

- 分類:計算機

並行同步計算機,一般指的是在同時實行兩個或多個資料庫、檔案、模組、執行緒之間用來保持數據內容一致性的機制的一種由於高速計算的電子計算機器。用軟體實現並行計算機系統的時鐘同步提出了利用軟體同步實現TANSPUTER系統中各處...

整體同步並行計算模型(Bulk Synchronous Parallel Computing Model),又名大同步模型或BSP模型,由哈佛大學Viliant和牛津大學Bill McColl提出。BSP的創始人是英國著名的計算機科學家Valiant,他希望像馮·諾伊曼體系結構那樣,架起電腦程式語言...

並行處理計算機系統(parallel computer system)是指同時執行多個任務或多條指令或同時對多個數據項進行處理的計算機系統。早期的計算機是串列逐位處理的,稱為串列計算機。隨著計算機技術的發展,現代計算機均具有不同程度的並行性。結構特點 ...

曙光1000是一個基於Message-passing機制的鬆散耦合大規模並行計算機系統。它包括32個基於i860的計算結點,1~2個系統服務結點子系統和2~3個I/O結點組成的外存子系統。這些結點由一個6×6的二維mesh網連線,每一個Mesh網路上有一個...

並行處理(Parallel Processing)是計算機系統中能同時執行兩個或多個處理的一種計算方法。並行處理可同時工作於同一程式的不同方面。並行處理的主要目的是節省大型和複雜問題的解決時間。為使用並行處理,首先需要對程式進行並行化處理,也就...

同步並行算法 同步並行算法(synchronized parallel algorithm)是2018年公布的計算機科學技術名詞。定義 一種即時的、實現進程之間完全同步執行的並行算法。出處 《計算機科學技術名詞 》第三版。

本書介紹MIMD(多指令流多數據流)並行計算機的基本概念及其類型特點、結構實現基礎技術——互連網路與存儲組織、典型結構模型及其相應特有技術,闡述多處理機的組織結構及其類型特點、性能分析及其評測、程式並行性及其度量計算,分析多處理機...

PRAM模型特別適合於並行算法的表達、分析和比較,使用簡單,很多關於並行計算機的底層細節,比如處理器間通信、存儲系統管理和進程同步都被隱含在模型中;易於設計算法和稍加修改便可以運行在不同的並行計算機系統上;根據需要,可以在PRAM模型...

《並行計算技術及其套用》是重慶大學出版社出版的圖書。《並行計算技術及其套用》內容包括並行算法、並行計算機體系結構、編程和套用,重點介紹了並行計算基本理論和實現技術,以及網路環境下的並行分散式計算技術。內容簡介 《並行計算技術及其...

單指令流多數據流計算機主要有向量機和陣列處理機兩種機型。陣列處理機是由一個控制器解釋指令,控制多個功能相同的處理部件對各自數據進行同樣操作的並行處理系統。開發多機並行處理系統的關鍵技術是各處理機之間實現通信和同步。常用匯流排、...

並行技術可分為三類,分別是執行緒庫、訊息傳遞庫和編譯器支持。執行緒庫可實現對執行緒的顯性控制;如果需要對執行緒進行精細管理,可以考慮使用這些顯性執行緒技術。藉助訊息傳遞庫,應用程式可同時利用多台計算機,它們彼此間不必共享同一記憶體空間。MPI...

實現方案和多種技術相結合的混合網路結構,解決了240個處理機互連的難題,從而研製出運算速度達到當時國內領先水平的並行計算機系統,實現了我國巨型計算機向大規模並行處理方向的發展,我國巨型計算機研製進入與國際同步發展的時代。

任務並行(也稱為功能並行和控制並行)是一種形式的並行化的計算機代碼在多個處理器中並行計算環境。任務並行性側重於分配不同處理器上的進程或執行緒同時執行的任務。與涉及在不同數據組件上運行相同任務的數據並行性相反,通過在同一數據上...

也就是說,這類並行計算機採用網際網路將許多聯繫較鬆散的計算機組成一個並行處理系統,其中每個計算機(常稱為結點機)都運行自己的作業系統,以訊息傳遞方式實現結點機之間的同步。這種並行機的各個結點機一般以外掛程式方式插在相對集中的1個或...

並行計算是指,當並發計算的程式,在機器平台上同時被運行的狀況,因此,並行計算是一種機器運算的形式之一。分散式計算(Distributed computing)則是並行計算的一個特例,它採用計算機網路來進行同步。實現並發程式有許多方式,依程式語言與...

大規模並行處理計算機採用的互連網路有:匯流排(Bus)、連結(Fully—Connected)、縱橫交叉(Crossber)、靜態點到點、動態單級網路和動態多級網路。由於大規模並行處理計算機中處理機很多,各處理機間同步與通信是一個難點,採用軟體方法實現同步...

《並行計算機組成與設計》是2017年4月機械工業出版社出版的圖書,作者是(美)米歇爾·杜波依斯(Michel Dubois)、(美)穆拉里·安納瓦拉姆(Murali Annavaram)、佩爾·斯坦斯托姆(Per Stenstr?m)。內容簡介 書中沒有晦澀抽象的技巧以及...

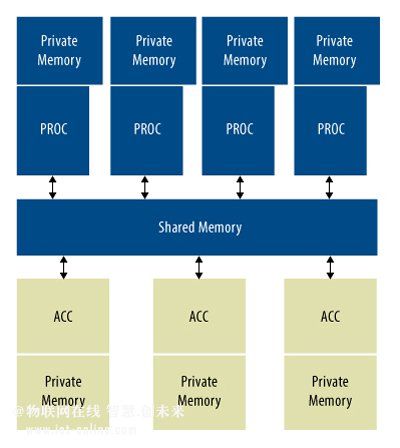

BSP(Bulk Synchronous Parallel,整體同步並行)模型是個分布存儲的MIMD(多指令流多數據流)計算模型,由哈佛大學的Viliant和牛津大學的Bill McColl提出。一台BSP計算機由”個處理器/存儲器(節點)組成,通過通信網路進行互聯。一個BSP程式有...

而功能並行是將一個程式分為若干個段,每一段由一台處理機或計算機執行,而多段程式並行執行需考慮段間同步、通訊等許多問題。基本概念 所謂數據並行是指把數據劃分成若干塊分別映像到不同的處理機上,每一台處理機運行同樣的處理程式...

MPI是一個跨語言的通訊協定,用於編寫並行計算機。支持點對點和廣播。MPI的目標是高性能,大規模性,和可移植性。MPI在今天仍為高性能計算的主要模型。主要的MPI-1模型不包括共享記憶體概念,MPI-2隻有有限的分布共享記憶體概念。 但是MPI程式...

並行計算機系統絕大部分為MIMD系統,包括並行向量處理機(PVP,Parallel Vector Processor),對稱對多處理機(SMP,Symmetrical Multi Processor),規模並行處理機(MPP,Massively Parallel Processor),工作站機群(COW,Cluster Of Work...

⑶進程同步:指令、任務、作業級別的並行處理,不需要同步控制(而並行處理機則要同步)。⑷多處理機工作時,要根據任務的多少來調用資源,因此,所需要的資源變化複雜。代表種類 由於對計算機的速度、性能要求越來越高,出現了超級並行...

共享存儲多處理機系統是包含具有統一地址空間的共享存儲器,各個處理機通過共享變數進行通信與同步,各處理機聯繫密切,實現高度的資源共享,因而又稱為緊密耦合併行處理系統或緊耦合並行計算機。如果所有的處理機都有相同的權力訪問外部設備,...