基本介紹

- 中文名:下拉電阻

- 外文名:pull-down resistor

- 分類:電阻

- 作用:與上接電阻給線路以一個固定電平

- 上下統稱:拉電阻

- 常態值:低電平

基本概念

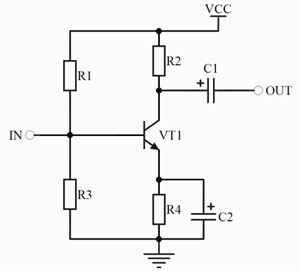

下拉電阻示意圖

下拉電阻示意圖主要作用

負反饋電阻

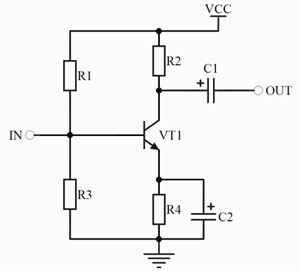

三極體單管放大電路

三極體單管放大電路典型電路

下拉電阻典型電路

下拉電阻典型電路

下拉電阻示意圖

下拉電阻示意圖

三極體單管放大電路

三極體單管放大電路 下拉電阻典型電路

下拉電阻典型電路上拉就是將不確定的信號通過一個電阻嵌位在高電平,電阻同時起限流作用。而下拉電阻的設定的原則和上拉電阻是一樣的。下拉電阻是直接接到地上,接二極體的時候...

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。上拉是對器件輸入電流,下拉是...

主要職能就是阻礙電流流過,套用於限流、分流、降壓、分壓、負載與電容配合作濾波器及阻匹配等.數字電路中功能有上拉電阻和下拉電阻。...

電路設計人員經常使用上拉電阻以及下拉電阻(通常為1至100 kΩ)讓這個處於三態的節點能有確定的默認邏輯狀態,防止狀態不定或感染噪聲。例如,I²C匯流排協定(一種...

電阻式觸控螢幕是一種感測器,它將矩形區域中觸摸點(X,Y)的物理位置轉換為代表X坐標和Y坐標的電壓。很多LCD模組都採用了電阻式觸控螢幕,這種螢幕可以用四線、五線、...

非線繞電阻器簡稱電阻(resistor,通常用“R”表示)是所有電子電路中使用最多的元件。...

排阻(Network Resistor),即網路電阻器(Wire-wound Resistor)。排阻是將若干個參數完全相同的電阻集中封裝在一起,組合製成的。它們的一個引腳都連到一起,作為公共...

電路設計人員經常使用上拉電阻以及下拉電阻(通常為1至100 kΩ)讓這個處於三態的節點能有確定的默認邏輯狀態,防止狀態不定或感染噪聲。例如,I²C匯流排協定(一種...

(On-Chip Debugging) 線上調試(關於嵌入式的名詞) (Off-Chip Driver) 離線驅動調整:OCD 的主要用意在於調整 I/O 接口端的電壓,來補償上拉與下拉電阻值。目的...

當它們用作地址管腳時,可分別置為“0”、“1” 或“f”(懸空);當它們用作數據管腳時,只能置為“0”或“1”(內部有下拉電阻) D1,D0 12,13 輸入 1~...

網路排阻是多個電阻集中封裝在一起組合製成。...... 排阻一般套用在數字電路上,比如:作為某個並行口的上拉或者下拉電阻用。使用排阻比用若干只固定電阻更方便,它...

即在靠近晶片的傳送端串聯電阻,使得該串聯電阻與晶片的內阻之和儘量與傳輸線阻抗...V--電壓源 R1---上拉電阻 R2--下拉電阻當R1=R2時,對高低邏輯的驅動要求均...

Attrib位決定了在口位的輸入狀態下是為懸浮式輸入還是非懸浮式輸入:即‘0’為帶上拉或下拉電阻式輸入,而‘1’則為懸浮式輸入。在口位的輸出狀態下則決定其輸出...