《一種數據時鐘恢復電路及其相位插值器》是龍迅半導體(合肥)股份有限公司於2015年12月29日申請的發明專利,該專利申請號為2015110221842,公布號為CN105634451A,專利公布日為2016年6月1日,發明人是邰連梁、夏洪鋒、徐希、任殿升、陶成、陳峰。

《一種數據時鐘恢復電路及其相位插值器》公開的數據時鐘恢復電路及其相位插值器,通過編碼電路根據並行時鐘和採樣時鐘或多相位時鐘組對數據控制信號進行兩次採樣,確定參考數據值;再根據控制單元輸出的相位控制信號生成第一編碼和第二編碼;由多路復用器根據第二編碼選擇接收的N個相位時鐘中的兩個進行輸出;由時鐘混頻器根據第一編碼接收兩個相位時鐘進行加權模擬運算之後生成並輸出的新相位時鐘;再由差分轉單端放大器將時鐘混頻器輸出的小信號放大成全擺幅信號,供給控制單元去判斷當前位置的時鐘所採樣的數據是否是最佳的採樣數據,如果不是將進一步控制編碼電路來改變相位插值器輸出時鐘的延遲位置,使時鐘超前或者滯後,最終會形成一個時鐘動態跟隨數據的穩定狀態。

2020年7月17日,《一種數據時鐘恢復電路及其相位插值器》獲得安徽省第七屆專利獎銀獎。

(概述圖為《一種數據時鐘恢復電路及其相位插值器》的摘要附圖)

基本介紹

- 中文名:一種數據時鐘恢復電路及其相位插值器

- 公布號:CN105634451A

- 公布日:2016年6月1日

- 申請號:2015110221842

- 申請日:2015年12月29日

- 申請人:龍迅半導體(合肥)股份有限公司

- 地址:安徽省合肥市經濟技術開發區創新創業園A座四層

- Int.Cl.:H03K5/135(2006.01)I

- 類別:發明專利

- 代理機構:北京集佳智慧財產權代理有限公司

- 發明人:邰連梁、夏洪鋒、徐希

專利背景,發明內容,專利目的,技術方案,改善效果,附圖說明,技術領域,權利要求,實施方式,榮譽表彰,

專利背景

在串列通信系統的接收端中,數據時鐘恢復電路(CDR,Clockand Data Recovery)用於從接收的串列數據流中提取時鐘且恢復出數據,CDR的性能直接制約著通信的質量。相位插值器(PI,Phase Interpolator)用於在CDR中對採樣的時鐘相位進行調整,以便實現數據的正確採樣。能夠精確調節時鐘相位的PI對於在接收端能否能夠正確地恢復出傳送端的數據非常重要。

在實際套用中由於工藝和環境溫度的影響,在CDR的工作過程中可能會產生相位階躍,從而導致其抖動性能的下降,直接惡化CDR的動態特性。

發明內容

專利目的

《一種數據時鐘恢復電路及其相位插值器》提供了一種數據時鐘恢復電路及其相位插值器,以解決2015年12月之前的技術中數據時鐘恢復電路動態性能差的問題。

技術方案

《一種數據時鐘恢復電路及其相位插值器》與數據時鐘恢復電路的控制單元相連,所述相位插值器包括:

編碼電路;所述編碼電路的輸入端與所述控制單元相連,用於根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼和第二編碼;兩個多路復用器;每個所述多路復用器的控制端與所述編碼電路輸出端相連,用於接收並根據所述第二編碼,選擇接收的N個相位時鐘中的兩個進行輸出;其中,N為大於等於4的偶數;時鐘混頻器;所述時鐘混頻器的控制端與所述編碼電路輸出端相連,所述時鐘混頻器的輸入端與所述多路復用器的輸出端相連,所述時鐘混頻器用於接收並根據所述第一編碼,接收所述兩個相位時鐘進行加權模擬運算之後生成並輸出的新相位時鐘;兩個差分轉單端放大器;每個所述差分轉單端放大器的輸入端與所述時鐘混頻器的輸出端相連,用於將所述時鐘混頻器輸出的小信號放大成全擺幅信號。

優選的,所述編碼電路包括:第一採樣單元,用於根據接收的所述並行時鐘對所述控制單元輸出的所述數據控制信號進行採樣;第二採樣單元,用於根據接收的所述採樣時鐘或者所述多相位時鐘組對所述採樣信號進行採樣,確定所述參考數據值;第一延遲單元,用於將所述參考數據值的高三位延遲所述並行時鐘的兩個周期,得到高三位延遲值;判斷單元,用於根據所述參考數據值的高三位和所述高三位延遲值進行邏輯處理,並判斷是否跨象限;第一運算單元,用於根據所述判斷單元的判斷結果及所述參考數據值的低四位進行邏輯運算,得到低四位運算;第二運算單元,用於根據所述判斷單元的判斷結果及所述控制單元輸出的所述相位控制信號,得到最低位運算值;獨熱碼邏輯單元,用於根據所述高三位延遲值進行獨熱碼邏輯處理,生成所述第二編碼;溫度計碼邏輯單元,用於根據所述低四位運算值及所述最低位運算值進行溫度計碼邏輯處理,生成所述第一編碼;其中,所述第一編碼的最低位為根據所述最低位運算值單獨編碼生成的。

優選的,當所述判斷單元的判斷結果為跨象限時,所述第一運算單元及所述第二運算單元用於將權重全部移交至交界相位的一邊,改變一次相位;所述獨熱碼邏輯單元用於改變所述第二編碼的相位;所述溫度計碼邏輯單元用於改變所述第一編碼的相位。 優選的,所述控制單元輸出的所述數據控制信號及所述相位控制信號均為二進制編碼。

優選的,所述時鐘混頻器包括:M個電流切換單元、第三電阻、第四電阻、第一NMOS電晶體、第二NMOS電晶體、第三NMOS電晶體和第四NMOS電晶體;其中,M為大於1的自然數; 所述第三電阻的一端和所述第四電阻的一端均與電源相連;所述第三電阻的另一端、所述第一NMOS電晶體的漏極及所述第三NMOS電晶體的漏極相連,連線點作為所述時鐘混頻器的一個輸出端;所述第四電阻的另一端、所述第二NMOS電晶體的漏極及所述第四NMOS電晶體的漏極相連,連線點作為所述時鐘混頻器的另一個輸出端;所述第一NMOS電晶體和所述第二NMOS電晶體的源極相連,連線點分別與所述M個電流切換單元的第一輸出端相連;所述第三NMOS電晶體和所述第四NMOS電晶體的源極相連,連線點分別與所述M個電流切換單元的第二輸出端相連;所述第一NMOS電晶體的柵極、所述第二NMOS電晶體的柵極、所述第三NMOS電晶體的柵極和所述第四NMOS電晶體的柵極分別作為所述時鐘混頻器的輸入端;所述M個電流切換單元的輸入端分別接收所述第一編碼,所述M個電流切換單元的接地端均接地。

優選的,所述時鐘混頻器還包括:M+1個尾電流提供單元、第五電阻、第一開關及第二開關;M個尾電流提供單元的一端分別與所述M個電流切換單元的接地端一一對應相連;所述第一開關的一端與所述M個電流切換單元的第一輸出端相連;所述第二開關的一端與所述M個電流切換單元的第二輸出端相連;所述第一開關的另一端、所述第二開關的另一端、所述第五電阻的一端及另一個尾電流提供單元的一端相連;所述M+1個尾電流提供單元的另一端均接地;所述第五電阻的另一端與所述電源相連。

優選的,所述電流切換單元包括:第五NMOS電晶體、第六NMOS電晶體及第七NMOS電晶體;其中:所述第六NMOS電晶體的漏極為所述電流切換單元的第一輸出端;所述第七NMOS電晶體的漏極為所述電流切換單元的第二輸出端;所述第六NMOS電晶體的源極、所述第七NMOS電晶體的源極及所述第五NMOS電晶體的漏極相連;所述第六NMOS電晶體的柵極及所述第七NMOS電晶體的柵極分別作為所述電流切換單元的兩個輸入端,接收所述第一編碼中兩個反向的信號;所述第五NMOS電晶體的源極接地;所述第五NMOS電晶體的柵極接收偏置電壓。

優選的,所述尾電流提供單元為電流源或者電流漏。優選的,所述多路復用器包括兩個選擇電路,每個選擇電路包括:N個第一NMOS電晶體;其中每兩個第一NMOS電晶體的源極相連,柵極分別接收相差180°相位的兩個相位時鐘,接收相鄰相位時鐘的第一NMOS電晶體的漏極相連,連線點分別作為所述選擇電路的兩個輸出端;N/2個第二NMOS電晶體;每個所述第二NMOS電晶體的漏極分別與兩個第一NMOS電晶體的源極連線點相連,N/2個所述第二NMOS電晶體的源極相連,柵極分別接收所述第二編碼;源極接地的第三NMOS電晶體;所述第三NMOS電晶體的柵極接收偏置電壓,漏極與所述第二NMOS電晶體的源極連線點相連;與所述選擇電路的兩個輸出端相連的負載元件,用於對接收的N個相位時鐘進行擺幅限制。

優選的,所述負載元件包括:第一電阻及第二電阻;其中:所述第一電阻的一端與所述選擇電路的一個輸出端相連;所述第二電阻的一端與所述選擇電路的另一個輸出端相連;所述第一電阻的另一端與所述第二電阻的另一端相連,連線點與電源相連。

一種數據時鐘恢復電路的相位插值器,與數據時鐘恢復電路的控制單元相連,所述相位插值器包括:

編碼電路;所述編碼電路的輸入端與所述控制單元相連,用於根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼;N個時鐘混頻器;每個所述時鐘混頻器的控制端與所述編碼電路輸出端相連,用於接收並根據所述第一編碼,選擇N個相位時鐘中的兩個接收並進行加權模擬運算之後生成並輸出的新相位時鐘;其中,N為大於等於4的偶數;兩個差分轉單端放大器;每個所述差分轉單端放大器的輸入端與所述時鐘混頻器的輸出端相連,用於將所述時鐘混頻器輸出的小信號放大成全擺幅信號。

一種數據時鐘恢復電路,包括:鎖相環,用於輸出N個相位時鐘;其中,N為大於等於4的偶數;控制單元,用於接收並行時鐘及並行數據,生成並輸出數據控制信號及相位控制信號;上述任一所述的數據時鐘恢復電路的相位插值器。

優選的,還包括:接收電路;所述接收電路與所述數據時鐘恢復電路的相位插值器的輸出端相連,用於接收採樣數據及所述數據時鐘恢復電路的相位插值器輸出的全擺幅信號;串並轉換電路;所述串並轉換電路的輸入端與所述接收電路的輸出端及所述數據時鐘恢復電路的相位插值器的輸出端相連,用於接收採樣數據及所述全擺幅信號,並將所述採樣數據進行串並轉換,生成所述並行時鐘、所述並行數據及採樣時鐘或者多相位時鐘組。

改善效果

《一種數據時鐘恢復電路及其相位插值器》公開的數據時鐘恢復電路的相位插值器,通過編碼電路根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼和第二編碼;由多路復用器接收並根據所述第二編碼,選擇接收的N個相位時鐘中的兩個進行輸出;由時鐘混頻器接收並根據所述第一編碼,接收所述兩個相位時鐘進行加權模擬運算之後生成並輸出的新相位時鐘;再由差分轉單端放大器將所述時鐘混頻器輸出的小信號放大成全擺幅信號,供給所述控制單元去判斷當前位置的時鐘所採樣的數據是否是最佳的採樣數據,如果不是將進一步控制所述編碼電路來改變所述相位插值器輸出時鐘的延遲位置,使時鐘超前或者滯後,最終會形成一個時鐘動態跟隨數據的穩定狀態。

附圖說明

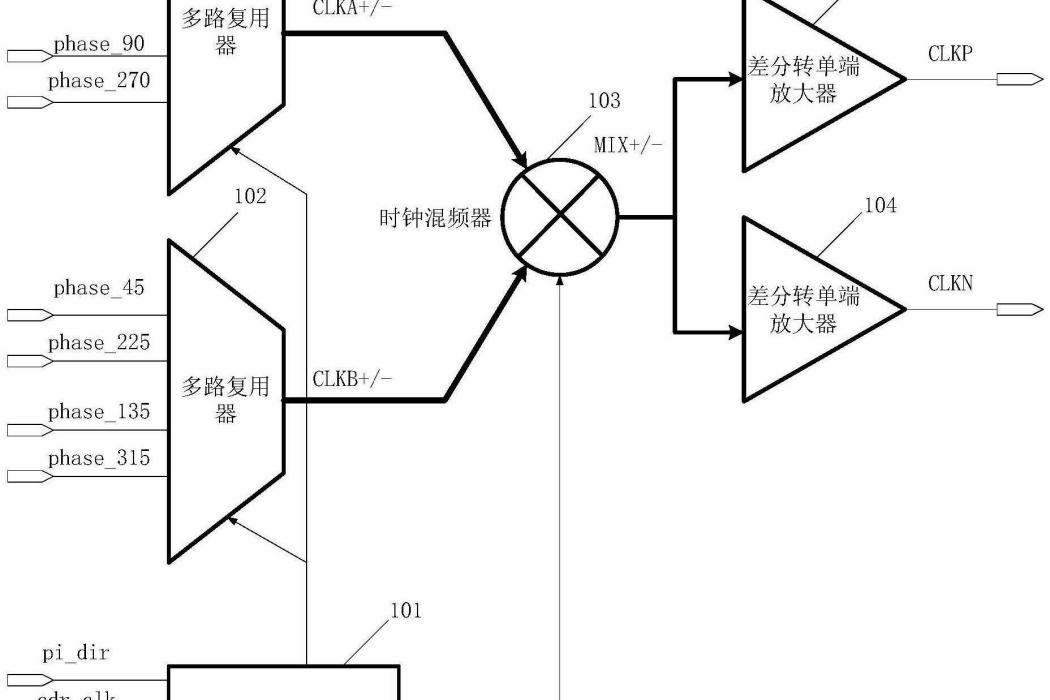

圖1為《一種數據時鐘恢復電路及其相位插值器》實施例公開的數據時鐘恢復電路的相位插值器結構示意圖;

圖2為該發明另一實施例公開的相位時鐘與權重之間的對應關係示意圖;

圖3為該發明另一實施例公開的編碼電路中各個數據的時序圖;

圖4為該發明另一實施例公開的時鐘混頻器的結構示意圖;

圖5為該發明另一實施例公開的另一時鐘混頻器的結構示意圖;

圖6為該發明另一實施例公開的電流切換單元的結構示意圖;

圖7為該發明另一實施例公開的多路復用器的結構示意圖;

圖8為該發明另一實施例公開的數據時鐘恢復電路的結構示意圖。

技術領域

《一種數據時鐘恢復電路及其相位插值器》涉及數據時鐘恢復技術領域,尤其涉及一種數據時鐘恢復電路及其相位插值器。

權利要求

1.《一種數據時鐘恢復電路及其相位插值器》其特徵在於,與數據時鐘恢復電路的控制單元相連,所述相位插值器包括:編碼電路;所述編碼電路的輸入端與所述控制單元相連,用於根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼和第二編碼;兩個多路復用器;每個所述多路復用器的控制端與所述編碼電路輸出端相連,用於接收並根據所述第二編碼,選擇接收的N個相位時鐘中的兩個進行輸出;其中,N為大於等於4的偶數;時鐘混頻器;所述時鐘混頻器的控制端與所述編碼電路輸出端相連,所述時鐘混頻器的輸入端與所述多路復用器的輸出端相連,所述時鐘混頻器用於接收並根據所述第一編碼,接收所述兩個相位時鐘進行加權模擬運算之後生成並輸出的新相位時鐘;兩個差分轉單端放大器;每個所述差分轉單端放大器的輸入端與所述時鐘混頻器的輸出端相連,用於將所述時鐘混頻器輸出的小信號放大成全擺幅信號;所述編碼電路包括:第一採樣單元,用於根據接收的所述並行時鐘對所述控制單元輸出的所述數據控制信號進行採樣,生成採樣信號;第二採樣單元,用於根據接收的所述採樣時鐘或者所述多相位時鐘組對所述採樣信號進行採樣,確定所述參考數據值;第一延遲單元,用於將所述參考數據值的高三位延遲所述並行時鐘的兩個周期,得到高三位延遲值;判斷單元,用於根據所述參考數據值的高三位和所述高三位延遲值進行邏輯處理,並判斷是否跨象限;第一運算單元,用於根據所述判斷單元的判斷結果及所述參考數據值的低四位進行邏輯運算,得到低四位運算值;第二運算單元,用於根據所述判斷單元的判斷結果及所述控制單元輸出的所述相位控制信號,得到最低位運算值;獨熱碼邏輯單元,用於根據所述高三位延遲值進行獨熱碼邏輯處理,生成所述第二編碼;溫度計碼邏輯單元,用於根據所述低四位運算值及所述最低位運算值進行溫度計碼邏輯處理,生成所述第一編碼;其中,所述第一編碼的最低位為根據所述最低位運算值單獨編碼生成的。

2.根據權利要求1所述的數據時鐘恢復電路的相位插值器,其特徵在於,當所述判斷單元的判斷結果為跨象限時,所述第一運算單元及所述第二運算單元用於將權重全部移交至交界相位的一邊,改變一次相位;所述獨熱碼邏輯單元用於改變所述第二編碼的相位;所述溫度計碼邏輯單元用於改變所述第一編碼的相位。

3.根據權利要求1所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述控制單元輸出的所述數據控制信號及所述相位控制信號均為二進制編碼。

4.根據權利要求1所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述時鐘混頻器包括:M個電流切換單元、第三電阻、第四電阻、第一NMOS電晶體、第二NMOS電晶體、第三NMOS電晶體和第四NMOS電晶體;其中,M為大於1的自然數;所述第三電阻的一端和所述第四電阻的一端均與電源相連;所述第三電阻的另一端、所述第一NMOS電晶體的漏極及所述第三NMOS電晶體的漏極相連,連線點作為所述時鐘混頻器的一個輸出端;所述第四電阻的另一端、所述第二NMOS電晶體的漏極及所述第四NMOS電晶體的漏極相連,連線點作為所述時鐘混頻器的另一個輸出端;所述第一NMOS電晶體和所述第二NMOS電晶體的源極相連,連線點分別與所述M個電流切換單元的第一輸出端相連;所述第三NMOS電晶體和所述第四NMOS電晶體的源極相連,連線點分別與所述M個電流切換單元的第二輸出端相連;所述第一NMOS電晶體的柵極、所述第二NMOS電晶體的柵極、所述第三NMOS電晶體的柵極和所述第四NMOS電晶體的柵極分別作為所述時鐘混頻器的輸入端;所述M個電流切換單元的輸入端分別接收所述第一編碼,所述M個電流切換單元的接地端均接地。

5.根據權利要求4所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述時鐘混頻器還包括:M+1個尾電流提供單元、第五電阻、第一開關及第二開關;M個尾電流提供單元的一端分別與所述M個電流切換單元的接地端一一對應相連;所述第一開關的一端與所述M個電流切換單元的第一輸出端相連;所述第二開關的一端與所述M個電流切換單元的第二輸出端相連;所述第一開關的另一端、所述第二開關的另一端、所述第五電阻的一端及另一個尾電流提供單元的一端相連;所述M+1個尾電流提供單元的另一端均接地;所述第五電阻的另一端與所述電源相連。

6.根據權利要求4或5所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述電流切換單元包括:第五NMOS電晶體、第六NMOS電晶體及第七NMOS電晶體;其中:所述第六NMOS電晶體的漏極為所述電流切換單元的第一輸出端;所述第七NMOS電晶體的漏極為所述電流切換單元的第二輸出端;所述第六NMOS電晶體的源極、所述第七NMOS電晶體的源極及所述第五NMOS電晶體的漏極相連;所述第六NMOS電晶體的柵極及所述第七NMOS電晶體的柵極分別作為所述電流切換單元的兩個輸入端,接收所述第一編碼中兩個反向的信號;所述第五NMOS電晶體的源極接地;所述第五NMOS電晶體的柵極接收偏置電壓。

7.根據權利要求4或5所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述尾電流提供單元為電流源或者電流漏。

8.根據權利要求1所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述多路復用器包括兩個選擇電路,每個選擇電路包括:N個第一NMOS電晶體;其中每兩個第一NMOS電晶體的源極相連,柵極分別接收相差180°相位的兩個相位時鐘,接收相鄰相位時鐘的第一NMOS電晶體的漏極相連,連線點分別作為所述選擇電路的兩個輸出端;N/2個第二NMOS電晶體;每個所述第二NMOS電晶體的漏極分別與兩個第一NMOS電晶體的源極連線點相連,N/2個所述第二NMOS電晶體的源極相連,柵極分別接收所述第二編碼;源極接地的第三NMOS電晶體;所述第三NMOS電晶體的柵極接收偏置電壓,漏極與所述第二NMOS電晶體的源極連線點相連;與所述選擇電路的兩個輸出端相連的負載元件,用於對接收的N個相位時鐘進行擺幅限制。

9.根據權利要求8所述的數據時鐘恢復電路的相位插值器,其特徵在於,所述負載元件包括:第一電阻及第二電阻;其中:所述第一電阻的一端與所述選擇電路的一個輸出端相連;所述第二電阻的一端與所述選擇電路的另一個輸出端相連;所述第一電阻的另一端與所述第二電阻的另一端相連,連線點與電源相連。

10.一種數據時鐘恢復電路的相位插值器,其特徵在於,與數據時鐘恢復電路的控制單元相連,所述相位插值器包括:編碼電路;所述編碼電路的輸入端與所述控制單元相連,用於根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼;N個時鐘混頻器;每個所述時鐘混頻器的控制端與所述編碼電路輸出端相連,用於接收並根據所述第一編碼,選擇N個相位時鐘中的兩個接收並進行加權模擬運算之後生成並輸出的新相位時鐘;其中,N為大於等於4的偶數;兩個差分轉單端放大器;每個所述差分轉單端放大器的輸入端與所述時鐘混頻器的輸出端相連,用於將所述時鐘混頻器輸出的小信號放大成全擺幅信號;所述編碼電路包括:第一採樣單元,用於根據接收的所述並行時鐘對所述控制單元輸出的所述數據控制信號進行採樣,生成採樣信號;第二採樣單元,用於根據接收的所述採樣時鐘或者所述多相位時鐘組對所述採樣信號進行採樣,確定所述參考數據值;第一延遲單元,用於將所述參考數據值的高三位延遲所述並行時鐘的兩個周期,得到高三位延遲值;判斷單元,用於根據所述參考數據值的高三位和所述高三位延遲值進行邏輯處理,並判斷是否跨象限;第一運算單元,用於根據所述判斷單元的判斷結果及所述參考數據值的低四位進行邏輯運算,得到低四位運算值;第二運算單元,用於根據所述判斷單元的判斷結果及所述控制單元輸出的所述相位控制信號,得到最低位運算值;溫度計碼邏輯單元,用於根據所述低四位運算值及所述最低位運算值進行溫度計碼邏輯處理,生成所述第一編碼;其中,所述第一編碼的最低位為根據所述最低位運算值單獨編碼生成的。

11.一種數據時鐘恢復電路,其特徵在於,包括:鎖相環,用於輸出N個相位時鐘;其中,N為大於等於4的偶數;控制單元,用於接收並行時鐘及並行數據,生成並輸出數據控制信號及相位控制信號;權利要求1至10任一所述的數據時鐘恢復電路的相位插值器。12.根據權利要求11所述的數據時鐘恢復電路,其特徵在於,還包括:接收電路;所述接收電路與所述數據時鐘恢復電路的相位插值器的輸出端相連,用於接收採樣數據及所述數據時鐘恢復電路的相位插值器輸出的全擺幅信號;串並轉換電路;所述串並轉換電路的輸入端與所述接收電路的輸出端及所述數據時鐘恢復電路的相位插值器的輸出端相連,用於接收採樣數據及所述全擺幅信號,並將所述採樣數據進行串並轉換,生成所述並行時鐘、所述並行數據及採樣時鐘或者多相位時鐘組。

實施方式

如圖1所示,所述《一種數據時鐘恢復電路及其相位插值器》與數據時鐘恢復電路的控制單元相連,所述相位插值器包括:編碼電路101;的輸入端與所述控制單元相連;兩個多路復用器102;每個多路復用器102的控制端與編碼電路101輸出端相連;時鐘混頻器103;時鐘混頻器103的控制端與編碼電路101輸出端相連,時鐘混頻器103的輸入端與多路復用器102的輸出端相連;兩個差分轉單端放大器104;每個差分轉單端放大器104的輸入端與時鐘混頻器103的輸出端相連。

編碼電路101根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼和第二編碼;多路復用器102接收並根據所述第二編碼,選擇接收的N個相位時鐘中的兩個進行輸出;其中,N為大於等於4的偶數;時鐘混頻器103接收並根據所述第一編碼,接收所述兩個相位時鐘進行加權模擬運算之後生成並輸出的新相位時鐘;差分轉單端放大器104將所述時鐘混頻器輸出的小信號放大成全擺幅信號。

具體工作流程為:

以N為8為例進行說明,兩個多路復用器102接收的8個相位時鐘分別為phase_0、phase_180、phase_90、phase_270、phase_45、phase_225、phase_135和phase_315。

編碼電路101根據接收的並行時鐘cdr_clk對所述控制單元輸出的數據控制信號cdr_code進行採樣,根據接收的採樣時鐘cdr_fast_clk或者多相位時鐘組cdr_bus_clk<3:0>對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號pi_dir進行處理,生成第一編碼和第二編碼;首先在系統上電後所述控制單元會復位所述相位插值器的編碼電路101,以使編碼電路101送出一組希望的第二編碼控制多路復用器102去選取兩組時鐘作為多路復用器102的輸出;在具體的實際套用中,編碼電路101送出的第二編碼可以為8位編碼信號,其偶數位和奇數位有均有一位為高電平信號,其他為低電平信號,而且這兩位為高電平信號的編碼位置上是相鄰的。編碼為高電平的控制信號將會閉合開關,兩組時鐘會被選取並放大輸出。復位時為高電平信號的兩位編碼信號為設計時預先設定好的。

然後,被選取的兩組時鐘CLKA+/-和CLKB+/-將會同時送給時鐘混頻器103進行加權插值混頻,復位時的編碼電路101送給時鐘混頻器103的第一編碼(在具體的套用中可以為32位編碼信號)為高電平的信號會作為權重的選取信號;在具體的實際套用中,其中的一組希望將被使用加權插值運算的時鐘的編碼控制信號全為高電平信號,另一組不希望將被使用加權插值運算的時鐘的編碼控制信號全為低電平信號。此時時鐘混頻器103隻會將一個帶全部權重信息的時鐘信號放大送出,然後時鐘混頻器103放大輸出信號MIX+/-再送給差分轉單端放大器104,差分轉單端放大器104主要功能是將時鐘混頻器放大輸出的小信號放大成全擺幅信號CLKP和CLKN,最終送給前端模擬的接收電路使用。復位的目的是保證數據時鐘恢復電路整個環路工作在一個確切的一個狀態,不至於環路斷開。

復位後,當接收電路接收到所述相位插值器送給的時鐘信號後,會對串列數據進行採樣並將串列數據轉變成並行數據,然後再供給所述控制單元去判斷當前位置的時鐘所採樣的數據是否是最佳的採樣數據,如果不是將進一步傳送信號控制所述相位插值器來改變時鐘的延遲位置,使時鐘超前或者滯後,最終會形成一個時鐘動態跟隨數據的穩定狀態。該實施例所述的數據時鐘恢復電路的相位插值器,編碼電路101將所述控制單元輸出的數據控制信號和相位控制信號進行編碼,變成多路復用器102和時鐘混頻器103工作時所需要的特殊數位訊號(所述第一編碼和所述第二編碼),然後控制多路復用器102和時鐘混頻器103先後無縫協同工作,實現了無突變的平滑過渡;並且差分轉單端放大器104輸出的所述全擺幅信號,可以供給所述控制單元去判斷當前位置的時鐘所採樣的數據是否是最佳的採樣數據,如果不是將進一步控制編碼電路101來改變所述相位插值器輸出時鐘的延遲位置,使時鐘超前或者滯後,最終會形成一個時鐘動態跟隨數據的穩定狀態。

優選的,所述編碼電路包括:

第一採樣單元,用於根據接收的所述並行時鐘對所述控制單元輸出的所述數據控制信號進行採樣;

第二採樣單元,用於根據接收的所述採樣時鐘或者所述多相位時鐘組對所述採樣信號進行採樣,確定所述參考數據值;

第一延遲單元,用於將所述參考數據值的高三位延遲所述並行時鐘的兩個周期,得到高三位延遲值;

判斷單元,用於根據所述參考數據值的高三位和所述高三位延遲值進行邏輯處理,並判斷是否跨象限;

第一運算單元,用於根據所述判斷單元的判斷結果及所述參考數據值的低四位進行邏輯運算,得到低四位運算值;

第二運算單元,用於根據所述判斷單元的判斷結果及所述控制單元輸出的所述相位控制信號,得到最低位運算值;

獨熱碼邏輯單元,用於根據所述高三位延遲值進行獨熱碼邏輯處理,生成所述第二編碼;

溫度計碼邏輯單元,用於根據所述低四位運算值及所述最低位運算值進行溫度計碼邏輯處理,生成所述第一編碼;其中,所述第一編碼的最低位為根據所述最低位運算值單獨編碼生成的。

優選的,當所述判斷單元的判斷結果為跨象限時,所述第一運算單元及所述第二運算單元用於將權重全部移交至交界相位的一邊,改變一次相位;所述獨熱碼邏輯單元用於改變所述第二編碼的相位;所述溫度計碼邏輯單元用於改變所述第一編碼的相位。 具體的工作原理為:

從所述控制單元輸出的所述參考數據值cdr_code<6:0>的高三位將會編碼成為所述多路復用器的所述第二編碼mux_sel<7:0>,去選擇將要參與混頻的兩組輸入時鐘信號;所述參考數據值cdr_code<6:0>的低四位將會編碼成為所述時鐘混頻器的所述第一編碼mix_sel<15:0>(mix_sel_b<15:0>是反向信號)去生成所述新相位時鐘。

值得說明的是,所述第一編碼的最低位mix_sel<0>(mix_sel_b<0>是反向信號)的碼值必須單獨進行編碼,因為這個最低位碼值不僅影響了編碼的速度,也影響著時鐘象限的平滑轉移。該碼值在編碼時需要額外的控制信號,即代表相位的超前或滯後的相位控制信號pi_dir。所述第一編碼的最低位mix_sel<0>的碼值根據所述相位控制信號pi_dir和當前的所在象限標誌共同來決定編碼出的。

所述參考數據值cdr_code<6:0>、所述第二編碼mux_sel<7:0>及所述第一編碼mix_sel<15:0>的對應關係可以參見表1:

cdr_code<6:0> | mux_sel<7:0> | mix_sel<15:0> |

|---|---|---|

0000000 | 00000011 | 0000000000000000 |

0000001 | 00000011 | 0000000000000010 |

0000010 | 00000011 | 0000000000000110 |

0000011 | 00000011 | 0000000000001110 |

| | | | | |

0001100 | 00000011 | 0001111111111110 |

0001101 | 00000011 | 0011111111111110 |

0001110 | 00000011 | 0111111111111110 |

0001111 | 00000011 | 1111111111111110 |

0010000 | 00000011 | 1111111111111111 |

0010000 | 00000110 | 1111111111111111 |

0010000 | 00000110 | 1111111111111111 |

0010001 | 00000110 | 0111111111111111 |

0010010 | 00000110 | 0011111111111111 |

0010011 | 00000110 | 0001111111111111 |

| | | | | |

0011100 | 00000110 | 0000000000001111 |

0011101 | 00000110 | 0000000000000111 |

0011110 | 00000110 | 0000000000000011 |

0011111 | 00000110 | 0000000000000001 |

根據時鐘混頻器的權重取值,可以將所述第一編碼mix_sel<15:0>和mix_sel_b<15:0>互換,不必重新考慮編碼,均在本申請的保護範圍內。

圖2所示為N個相位時鐘與權重的對應關係;當所述判斷單元的判斷結果為跨象限時,在相位跨界處需要進行特殊處理,首先需要先將權重全部移至交界相位的一邊,相位改變一次;再改變多路復用器來換相位,此時權重不在此相位上,權重全在上一步的交界相位上,相位基本不變;最後改變時鐘混頻器,完成相位跳變,相位改變一次;從整個過程中不難看出,在相位跨界處,相位變化了兩次,基本沒有損失PI的回響速度。在整個CDR過程中,PI的編碼部分實現了只增加一個周期的延遲,基本沒有損耗CDR的頻寬。

如圖3所示的是上述編碼算法的具體實現時序圖,相位插值器接收到並行時鐘cdr_clk和採樣快時鐘cdr_fast_clk或者多相位時鐘組cdr_bus_clk<3:0>,將會對所述控制單元送達的數據控制信號cdr_code<6:0>及相位控制信號pi_dir進行重新採樣,先使用並行時鐘cdr_clk對數據採樣,保證接口時序的正確,然後使用採樣快時鐘cdr_fast_clk或者多相位時鐘組cdr_bus_clk<3:0>對並行時鐘採樣後的數據再重新採樣,這樣在快時鐘領域得參考點(所述參考數據值)就確定下來,再根據數控制信號據cdr_code<6:0>及相位控制信號pi_dir對數據進行邏輯編碼。首先先將參考數據值的高三位cdr_code_a<6:4>延遲兩個周期後得到高三位延遲值cdr_code_b<6:4>,然後和參考數據值的高三位cdr_code_a<6:4>進行簡單的異或邏輯判斷當前給出的二進制碼所代表的象限是否跨界(跨象限),接著使用這個判定結果信號將參考數據值的低四位cdr_code_a<3:0>邏輯運算得到cdr_code_b<3:0>,進一步邏輯運算得到低四位運算值cdr_code_c<3:0>,同時也使用這個判定結果信號結合相位控制信號pi_dir重新產生數據pre_mixcode_lsb,最後將高三位延遲值cdr_code_b<6:4>、低四位運算值cdr_code_c<3:0>和pre_mixcode_lsb一起送給核心編碼電路(所述獨熱碼邏輯單元和所述溫度計碼邏輯單元)進行編碼分別得到最終的編碼值mux_sel<7:0>,mix_sel<15:0>、mix_sel_b<15:0>。計入所述編碼電路的延時到圖3最右側的虛線所示的時鐘沿之前所有電路邏輯要全部完成,若時間不夠需要加入觸發器,同時時鐘也要隨之改變,視其具體套用環境而定,均在本申請的保護範圍內。

值得說明的是,如果使用的採樣快時鐘cdr_fast_clk是並行時鐘cdr_clk的N倍,則採樣快時鐘cdr_fast_clk可以被和並行時鐘cdr_clk同頻的多相位時鐘組cdr_bus_clk<N:0>所代替,如果考慮使用並行時鐘cdr_clk的話,使用cdr_bus_clk<N-1:0>同樣是可以的,均在本申請的保護範圍內。

如果不跨界,按不跨界的方式處理;如果跨界,按跨界的方式處理。圖3中在跨界的①,②,③三種狀態時,關鍵數據cdr_code_b<3:0>、cdr_code_c<3:0>及pre_mixcode_lsb的具體取值見表2和表3所示:

取值 | ⓪ | ① | ② |

|---|---|---|---|

cdr_code_a<4>=0, cdr_code_b<3:0>= | cdr_code_a<3:0> | cdr_code_a<3:0> | cdr_code_a<3:0> |

cdr_code_a<4>=1, cdr_code_b<3:0>= | cdr_code_a<3:0>的反碼 | cdr_code_a<3:0>的反碼 | cdr_code_a<3:0>的反碼 |

跨界時取值 | ① | ② | ③ |

|---|---|---|---|

cdr_code_c<3:0>= | cdr_code_a<4>同或pi_dir | cdr_code_a<4>同或pi_dir | cdr_code_b<3:0> |

pre_mixcode_lsb= | cdr_code_a<4>同或pi_dir | cdr_code_a<4>同或pi_dir | cdr_code_a<4> |

優選的,所述控制單元輸出的所述數據控制信號及所述相位控制信號均為二進制編碼。

所述數據控制信號及所述相位控制信號均為二進制編碼,不會降低頻寬,再經過PI的編碼電路即可產生可用碼值。

優選的,如圖4所示,所述時鐘混頻器包括:M個電流切換單元、第三電阻R3、第四電阻R4、第一NMOS電晶體N1、第二NMOS電晶體N2、第三NMOS電晶體N3和第四NMOS電晶體N4;其中,M為大於1的自然數;第三電阻R3的一端和第四電阻R4的一端均與電源VDD相連;第三電阻R3的另一端、第一NMOS電晶體N1的漏極及第三NMOS電晶體N3的漏極相連,連線點作為所述時鐘混頻器的一個輸出端;第四電阻R4的另一端、第二NMOS電晶體N2的漏極及第四NMOS電晶體N4的漏極相連,連線點作為所述時鐘混頻器的另一個輸出端;第一NMOS電晶體N1和第二NMOS電晶體N2的源極相連,連線點分別與所述M個電流切換單元的第一輸出端a相連;第三NMOS電晶體N3和第四NMOS電晶體N4的源極相連,連線點分別與所述M個電流切換單元的第二輸出端b相連;第一NMOS電晶體N1的柵極、第二NMOS電晶體N2的柵極、第三NMOS電晶體N3的柵極和第四NMOS電晶體N4的柵極分別作為所述時鐘混頻器的輸入端;所述M個電流切換單元的輸入端分別接收所述第一編碼,所述M個電流切換單元的接地端均接地。

所述多路復用器輸出的兩組時鐘其中的CLKA+和CLKB+分別連線的增益管(第一NMOS電晶體N1和第三NMOS電晶體N3)的漏端連線一起MIX-,而CLKA-和CLKB-分別連線的增益管(第二NMOS電晶體N2和第四NMOS電晶體N4)的漏端連線一起MIX+,分別共用一個負載元件(第三電阻R3或者第四電阻R4),這樣確保加權插值混頻的時鐘的延遲時間是漸近變化的,這個負載元件連線的節點就是時鐘混頻器的輸出節點。

各個增益管連線著代表權重的電流切換單元,這些電流切換單元連線的控制信號(第一編碼)來自編碼電路,每個電流切換單元均有兩個控制信號,而且這兩個控制信號是互斥的(如mix_sel<0>與mix_sel_b<0>,或者mix_sel<15>與mix_sel_b<15>),這樣也就保證了所有的電流切換單元所流經的電流加在一起是一個固定電流,這個固定電流中有多少比例的電流流經對應的增益管,也就代表了增益管對應的時鐘的權重大小。當來自編碼電路輸出的控制信號(第一編碼)發生改變,兩組時鐘的權重比例即發生改變,時鐘混頻器的輸出時鐘的延遲時間也就隨著改變,從而完成加權插值整個過程。

圖4所示的電流切換單元以16個為例進行展示,控制電流切換單元的控制信號為32個。電流切換單元個數也可以為其他數量,可以取大於1的自然數,當然也是有極限的,視其具體的套用環境而定。

或者,如圖5所示,所述時鐘混頻器還包括:M+1個尾電流提供單元、第五電阻R5、第一開關S1及第二開關S2;

M個尾電流提供單元的一端分別與所述M個電流切換單元的接地端一一對應相連;第一開關S1的一端與所述M個電流切換單元的第一輸出端a相連;第二開關S2的一端與所述M個電流切換單元的第二輸出端b相連;第一開關S1的另一端、第二開關S2的另一端、第五電阻R5的一端及另一個尾電流提供單元的一端相連;所述M+1個尾電流提供單元的另一端均接地;第五電阻R5的另一端與電源VDD相連。

優選的,如圖6所示,圖4和圖5中的所述電流切換單元包括:第五NMOS電晶體N5、第六NMOS電晶體N6及第七NMOS電晶體N7;其中:

第六NMOS電晶體N6的漏極為所述電流切換單元的第一輸出端a;

第七NMOS電晶體N7的漏極為所述電流切換單元的第二輸出端b;

第六NMOS電晶體N6的源極、第七NMOS電晶體N7的源極及第五NMOS電晶體N5的漏極相連;

第六NMOS電晶體N6的柵極及第七NMOS電晶體N7的柵極分別作為所述電流切換單元的兩個輸入端,接收所述第一編碼中兩個反向的信號;第五NMOS電晶體N5的源極接地;第五NMOS電晶體N5的柵極接收偏置電壓。

電流切換單元電路如圖6所示,該單元電路主要由3個NMOS管組成(第五NMOS電晶體N5、第六NMOS電晶體N6及第七NMOS電晶體N7),其中第五NMOS電晶體N5為電流管用於提供加權的電流,第六NMOS電晶體N6及第七NMOS電晶體N7為開關切換管用於切換電流管的電流方向。對於一個單元電路來說,當編碼電路送來一對互斥的控制信號時,比如mix_sel為高電平信號,mix_sel_b為低電平信號,則第六NMOS電晶體N6閉合,第七NMOS電晶體N7斷開,第六NMOS電晶體N6所對應的時鐘的權重將會增加一個,第七NMOS電晶體N7所對應的時鐘的權重減少增加一個,導致相位插值器輸出時鐘位置會向第六NMOS電晶體N6所對應的時鐘移動,也意味著輸出時鐘的位置超前,反之滯後。這裡選取的參考時鐘是不變。

圖5所示的所述時鐘混頻器採用圖6的電流切換單元,可以有效提高PI的線性度,並針對傳統的線性電流加權混頻方法進行了修正,採用了非線性電流加權混頻方法可以進一步提高了PI的線性度。達到了降低周期到周期抖動的目的,從而降低了誤碼率,提高了基於PI方式的自適應均衡技術的性能。

對於一個PI,其歸一化的權重用A1、A2表示,混頻的兩個相位時鐘用sin(ωT)和sin(ωT-φd),混頻後的時鐘為: 其中的p=A1+A2cosφd,q=A2sinφd,tanφPI=q/p;此處φd=45°,如果等間隔分成16等分後,則tanφPI取值範圍為,(a∈),結合A1+A2=1求取線性補償後的權重A1、A2的取值,最後根據實際使用總電流將歸一化的權重轉化為每個電流切換單元電路需要的電流,經計算補償後的電流值成對稱(圖5中給出的最終計算值按最大電流1mA為準)。

其中的p=A1+A2cosφd,q=A2sinφd,tanφPI=q/p;此處φd=45°,如果等間隔分成16等分後,則tanφPI取值範圍為,(a∈),結合A1+A2=1求取線性補償後的權重A1、A2的取值,最後根據實際使用總電流將歸一化的權重轉化為每個電流切換單元電路需要的電流,經計算補償後的電流值成對稱(圖5中給出的最終計算值按最大電流1mA為準)。

圖5所示的所述時鐘混頻器還給出了進一步提高線性的電荷充電的補償方法,其原理為:當電流切換單元里的電流全部都流向兩個輸入時鐘信號中的一個時,一組輸入時鐘信號具有全部的權重,另一組輸入時鐘信號沒有權重,這個時候沒有權重的輸入時鐘信號在權重全部變為0的過程會對輸出有擾動,因為圖4中的第一NMOS電晶體N1、第二NMOS電晶體N2(或者第三NMOS電晶體N3、第四NMOS電晶體N4)從飽和工作區突然變為線性區,會使得輸出節點電勢降低,從而影響了最終輸出,在權重全部變為0的過程,閉合第一開關S1(或者第二開關S2),斷開第二開關S2(或者第一開關S1),使得節點Vcomp對節點A(B)進行充電,這個節點Vcomp的設定一般小於輸出節點的最小信號電壓,這樣節點A(B)的電勢將會得到一定的補償,解決了第一NMOS電晶體N1、第二NMOS電晶體N2(或者第三NMOS電晶體N3、第四NMOS電晶體N4)的溝道漏電的難題,從而進一步提高了線性度。

優選的,所述尾電流提供單元為電流源或者電流漏。

在具體的實際套用中,各個所述尾電流提供單元提供的電流不做具體限定,多個所述電流切換單元接收到的電流可以依次為68.1微安、65.7微安、63.8微安、62.3微安、61微安、60.2微安、59.6微安及59.3微安等等,視其具體套用環境而定。

優選的,多路復用器102包括兩個選擇電路,每個選擇電路如圖7所示,包括:

N個第一NMOS電晶體N1;其中每兩個第一NMOS電晶體N1的源極相連,柵極分別接收相差180°相位的兩個相位時鐘,接收相鄰相位時鐘的第一NMOS電晶體的漏極相連,連線點分別作為所述選擇電路的兩個輸出端;

N/2個第二NMOS電晶體N2;每個第二NMOS電晶體N2的漏極分別與兩個第一NMOS電晶體N1的源極連線點相連,N/2個第二NMOS電晶體N2的源極相連,柵極分別接收所述第二編碼;

源極接地的第三NMOS電晶體N3;第三NMOS電晶體N3的柵極接收偏置電壓,漏極與第二NMOS電晶體N3的源極連線點相連;

與所述選擇電路的兩個輸出端相連的負載元件120,用於對接收的N個相位時鐘進行擺幅限制。

優選的,如圖7所示,負載元件120包括:第一電阻R1及第二電阻R2;其中:

第一電阻R1的一端與所述選擇電路的一個輸出端相連;

第二電阻R2的一端與所述選擇電路的另一個輸出端相連;

第一電阻R1的另一端與第二電阻R2的另一端相連,連線點與電源VDD相連。

兩個多路復用器102輸入的多相位時鐘以8個時鐘phase_0、phase_180、phase_45、phase_225、phase_90、phase_270、phase_135和phase_315為例進行說明,圖7僅為其中的一個多路復用器102,接收phase_0、phase_180、phase_90、phase_270、mux_sel<0>、mux_sel<2>、mux_sel<4>和mux_sel<6>,另一個多路復用器102接收的是phase_45、phase_225、phase_135、phase_315、mux_sel<1>、mux_sel<3>、mux_sel<5>和mux_sel<7>,與圖7結構相同。

在復位時編碼電路送給的編碼信號只有mux_sel<1>和mux_sel<0>為高電平,其餘的mux_sel<7:2>全為低電平。當編碼信號到達時,圖7中接收mux_sel<1>或mux_sel<0>的第二NMOS電晶體N2會閉合,phase_0/phase_180,phase_45/phase_225將會被多路復用器放大輸出。圖7中的nbias為偏置電壓。

負載元件120可以將輸入的多相位時鐘經過多路復用器102之後限制在一定的擺幅範圍內,適當的改變多路復用器102和時鐘混頻器103二者的輸出節點的RC時間常數,從而可以送給時鐘混頻器103實現較寬頻率範圍(100兆赫茲—2吉赫茲)內進行相位插值。

第一電阻R1及第二電阻R2構成了負載元件120,其作用是將輸入的多相位時鐘經過所述多路復用器之後限制在一定的擺幅範圍內,同時可以套用在較高的速度上。其中第二NMOS電晶體N2均為開關管,第一NMOS電晶體N1均為增益管。圖7所示,以開關管是設定在增益管下面為例進行展示,在具體的套用中也可以將開關管置於增益管得上面,優點是減少增益管的米勒效應,即減少輸出信號對輸入信號的回饋影響,均在本申請的保護範圍內。該實施例中給出的多相位時鐘輸入為8個時鐘,控制信號也為8個。多相位時鐘輸入的個數也可以為其他數量,可以取4、6、8…N大於4的偶數,N/2為奇數時,多相位時鐘輸入的使用接法有些特別之處,同樣在該發明的保護範圍內。

該發明另一實施例還提供了另外一種數據時鐘恢復電路的相位插值器,與數據時鐘恢復電路的控制單元相連,所述相位插值器包括:

編碼電路;所述編碼電路的輸入端與所述控制單元相連,用於根據接收的並行時鐘對所述控制單元輸出的數據控制信號進行採樣,生成採樣信號,根據接收的採樣時鐘或者多相位時鐘組對所述採樣信號進行採樣,確定參考數據值;根據所述參考數據值和所述控制單元輸出的相位控制信號進行處理,生成第一編碼;N個時鐘混頻器;每個所述時鐘混頻器的控制端與所述編碼電路輸出端相連,用於接收並根據所述第一編碼,選擇N個相位時鐘中的兩個接收並進行加權模擬運算之後生成並輸出的新相位時鐘;其中,N為大於等於4的偶數;兩個差分轉單端放大器;每個所述差分轉單端放大器的輸入端與所述時鐘混頻器的輸出端相連,用於將所述時鐘混頻器輸出的小信號放大成全擺幅信號。

該實施例與上述實施例的區別在於:省去了上述實施例中的多路復用器,可以將時鐘混頻器多使用幾路來替代多路復用器,N個所述時鐘混頻器則具備所述多路復用器的功能,適用於較低的工作頻率,但是帶來的代價是面積會增大。上述實施例中使用了多路復用器,適用於較高的工作頻率,節省了所述相位插值器的面積,提高線性度,使得套用的頻率範圍變寬。兩者均在本申請的保護範圍內,此處不做具體限定。

該發明另一實施例還提供了一種數據時鐘恢復電路,如圖8所示,包括:鎖相環201、控制單元202及上述實施例任一所述的數據時鐘恢復電路的相位插值器203。

其中,鎖相環201用於輸出N個相位時鐘;其中,N為大於等於4的偶數;控制單元202用於接收並行時鐘及並行數據,生成並輸出數據控制信號及相位控制信號;數據時鐘恢復電路的相位插值器203與上述實施例所述的數據時鐘恢復電路的相位插值器的結構及原理均相同。

優選的,如圖8所示,所述數據時鐘恢復電路還包括:

接收電路204;接收電路204與數據時鐘恢復電路的相位插值器203的輸出端相連;串並轉換電路205;串並轉換電路205的輸入端與接收電路204的輸出端及數據時鐘恢復電路的相位插值器203的輸出端相連。

其中,接收電路204用於接收採樣數據及所述數據時鐘恢復電路的相位插值器輸出的全擺幅信號;串並轉換電路205用於接收採樣數據及所述全擺幅信號,並將所述採樣數據進行串並轉換,生成所述並行時鐘、所述並行數據及採樣時鐘或者多相位時鐘組。

對於同源的多通道傳輸系統,其傳輸過程中會伴隨著和數據速率有一定比例關係的同源時鐘,這樣在接收端的數據時鐘恢復過程中只需考慮時鐘和數據之間的瞬時位置偏移,採用時鐘混相的PI可以時時來改變時鐘的相位位置,從而修正時鐘與數據之間的偏移距離,即可達到最佳位置採樣數據的目的。

對於不同源的多通道傳輸系統,其傳輸過程中不會伴隨著和數據速率有一定比例關係的同源時鐘,這樣在接收端的數據時鐘恢復過程中不僅需考慮時鐘和數據之間的瞬時位置偏移,而且要考慮長時間頻偏的影響,採用高速PI可以時時來改變時鐘的相位位置,從而修正時鐘與數據之間的偏移距離,達到最佳位置採樣數據的目的。在CDR的環路中,CDR的控制單元作為整個環路的判斷控制中心,用來控制PI調整相位的控制信號一般都交給CDR的控制單元來完成,隨著數據通道數量和混頻相位數量的增加,這些控制信號將會變得繁複,給後期的版圖設計帶來難度,且時序將不易控制,需要耗費更多的走線面積。

該申請中所述的數據時鐘恢復電路,能夠適用於不同源的多通道傳輸系統,針對繁複的控制信號而發明的所述編碼電路,可以降低後期的版圖設計難度,使得時序易於控制,從而降低成本;同樣無需複雜的象限邊界控制單元去檢測邊界跨越難題,避免了相位階躍的缺陷,實現了象限的平滑轉移。所述編碼電路採用了高速時鐘或者多相位時鐘來實現快速編碼功能,很大提高了的PI的跳變速度,使得PI在整個CDR環路中體現了一個運算邏輯時鐘的延遲,但最終使得整個CDR環路的頻寬有個較大提高,使得頻率跟蹤的能力也隨之提高。該發明可以滿足正負約6000ppm頻偏的跟蹤指標,理論最大可滿足正負約12000ppm頻偏的跟蹤指標,實現了任意最大跨度40°左右的跳變且在一個並行時鐘周期內。

另外,針對PI的典型的非線性而提出的所述電流切換單元,可以有效提高PI的線性度以及電流的切換速度,並針對傳統的線性電流加權混頻方法進行了修正,採用了非線性電流加權混頻方法可以進一步提高了PI的線性度。達到了降低周期到周期抖動的目的,從而降低了誤碼率,提高了基於PI方式的自適應均衡技術的性能。

該說明書中各個實施例採用遞進的方式描述,每個實施例重點說明的都是與其他實施例的不同之處,各個實施例之間相同相似部分互相參見即可。

榮譽表彰

2020年7月17日,《一種數據時鐘恢復電路及其相位插值器》獲得安徽省第七屆專利獎銀獎。