《一種基於FPGA的多通道高速輸入信號自動de-skew方法》是合肥埃科光電科技有限公司於2016年8月9日申請的發明專利,該專利申請號為2016106473597,公布號為CN106254287A,專利公布日為2016年12月21日,發明人是曹桂平、董寧、唐世悅、吳暢、葉加聖。

《一種基於FPGA的多通道高速輸入信號自動de-skew方法》涉及高速數據採集領域,具體包括以下步驟:步驟(1)檢測並計算各數據通道間相對skew值;步驟(2)補償各數據通道的skew使得各數據通道對齊;步驟(3)將數據鎖存觸發信號對齊到鎖存視窗的中心。該發明基於FPGA中動態相位調整技術以及動態延遲技術,針對每個通道進行de‑skew,從而使得各通道數據在接收端進行鎖存時達到完全的同步性,增大了數據有效鎖存視窗,提高了數據鎖存的正確性,為高速/超高速數據採集系統提供了一種可靠且行之有效的數據鎖存方法。

2021年8月16日,《一種基於FPGA的多通道高速輸入信號自動de-skew方法》獲得安徽省第八屆專利獎優秀獎。

概述圖為《一種基於FPGA的多通道高速輸入信號自動de-skew方法》的摘要附圖)

基本介紹

- 中文名:一種基於FPGA的多通道高速輸入信號自動de-skew方法

- 公布號:CN106254287A

- 公布日:2016年12月21日

- 申請號: 2016106473597

- 申請日:2016年8月9日

- 申請人:合肥埃科光電科技有限公司

- 地址:安徽省合肥市高新區黃山路602號大學科技園A208

- 發明人:曹桂平、董寧、唐世悅、吳暢、葉加聖

- Int.Cl.:H04L25/14(2006.01)I

- 類別:發明專利

- 專利代理機構:合肥天明專利事務所

- 代理人:金凱

專利背景,發明內容,專利目的,技術方案,改善效果,附圖說明,技術領域,權利要求,實施方式,榮譽表彰,

專利背景

截至2016年8月,隨著對精度和速率要求越來越高,數據採集系統向著多通道和超高速兩個方向發展。多通道高速輸入信號通常存在一個關鍵性的問題,即各路高速信號之間同步性差,通常會存在較大的偏差(skew)。在低速套用場景中,由於每個數據位持續時間長,這種skew不會造成數據鎖存問題,但在高速/超高速套用場景下,每個數據位持續時間非常短,如果通道之間skew較大,則有效鎖存視窗將大大縮小,基本無法進行正確的數據鎖存,而且隨著通道數量增大,由於不確定性大大增加,各通道之間的差異將會擴大,即有效數據鎖存視窗會繼續惡化,則可以想見,要達到對多通道的同時正確的鎖存是非常困難的。

針對高速數據採集系統中多通道高速輸入信號存在的skew問題,2016年8月以前較為常見的解決方法是採用源同步方式,即傳送端同時傳送數據和鎖存數據用的觸發(時鐘)信號,但即便如此,多路數據通道之間以及數據通道和觸發信號通道之間依然會存在或大或小的skew。另一種常見的方法是在PCB走線上保持嚴格的等長關係並通過增加各通道之間走線間距儘量減小串擾,然而在一些條件下,特別在PCB尺寸受限套用場合,嚴格的等長走線或者較大的走線間隔很難執行。即使在保持PCB走線嚴格等長的情況下,由於接收端各通道之間負載(寄生)電容的差異,各通道之間依然會存在skew,在速率較高的場合,即便可以在某個工作條件下進行鎖存,但是鎖存視窗非常小,在長時間工作情況下或者大批量複製時,溫度變化或者個體差異也會造成數據鎖存可能出現誤碼,造成數據中有亮點或者暗點產生,這在某些套用場合如工業檢測領域將是無法容忍的。綜合而言,無論採用以上所述的何種外界手段,都很難完全消除多通道輸入信號之間的skew。

發明內容

專利目的

《一種基於FPGA的多通道高速輸入信號自動de-skew方法》所要解決的技術問題在於提供一種基於FPGA的多通道高速輸入信號自動de-skew算法,該算法解決了多通道高速輸入信號中各通道之間skew較大,有效鎖存視窗大大縮小,基本無法進行正確的數據鎖存的問題,擬為高速/超高速數據採集系統提供一種可靠的、有效的數據鎖存方法。

技術方案

《一種基於FPGA的多通道高速輸入信號自動de-skew方法》具體包括以下步驟:

步驟(1)檢測並計算各數據通道間相對skew值;

步驟(2)補償各數據通道的skew使得各數據通道對齊;

步驟(3)將數據鎖存觸發信號對齊到鎖存視窗的中心。

進一步地,所述步驟(1)中各數據通道間相對skew值的計算方法具體為:配置前端AD系統傳送訓練序列,使用FPGA內部鎖相環(PLL)產生鎖存時鐘,在鎖存時鐘的初始相位採集各數據通道數據,並將數據保存,然後動態調整鎖存時鐘的相位,每次移動一個步長,每移動一次採集一次各數據通道的數據並進行保存,鎖存時鐘的相位移動360度內可獲得各數據通道邊沿位置信息。在獲取到各通道掃描結果後,以邊沿最靠後通道作為參考通道,計算其他通道邊沿相對於該通道邊沿的差異,即可獲得各通道相對skew值。進一步地,所述步驟(2)中對各通道進行延遲補償(de-skew)的過程具體為:將步驟(1)中計算得到的skew值換算為延遲步長,即可得到延遲單元數N(delay),對N(delay)取整,採用動態延遲技術,在工作過程中動態的設定各數據通道在鎖存之前的延遲,使得各通道邊沿完全對齊。進一步地,所述各數據通道所採用的延遲補償是PVT修正的,所述PVT修正是根據工藝,電壓和溫度進行修正的。進一步地,所述步驟(3)中將數據鎖存觸發信號對齊到鎖存視窗中心的方法為:以鎖存時鐘當前位置作為起點,每次移動一個步長進行掃描,選擇任意一個通道作為採集通道,採集該通道在當前相位下的值,直到採集到的值發生跳變停止掃描過程。根據數據率計算將鎖存觸發時鐘對齊到視窗中心所需移動的步長,將鎖存觸發時鐘對齊到視窗中心。在完成de-skew之後,重新配置前端AD系統,退出訓練模式,進入到正常工作狀態,完成數據的正常採集工作。

改善效果

《一種基於FPGA的多通道高速輸入信號自動de-skew方法》基於FPGA中動態相位調整技術以及動態延遲技術,針對每個通道進行de-skew,從而使得各通道數據在接收端進行鎖存時達到完全的同步性,增大了數據有效鎖存視窗,提高了數據鎖存的正確性,為高速/超高速數據採集系統提供了一種可靠且行之有效的數據鎖存方法;該發明採用動態延遲技術,每次上電時根據實際運行環境計算出的各通道skew值並進行動態延遲,而不是每次採用相同的延遲補償值,這使得算法有效性和靈活性大大增加;該發明中所採用的延遲補償技術是PVT修正的,具有高穩定性,不會因為工藝,電壓,溫度差異造成較大誤差,從而使得本算法具有極大的可操作性和實用性。

附圖說明

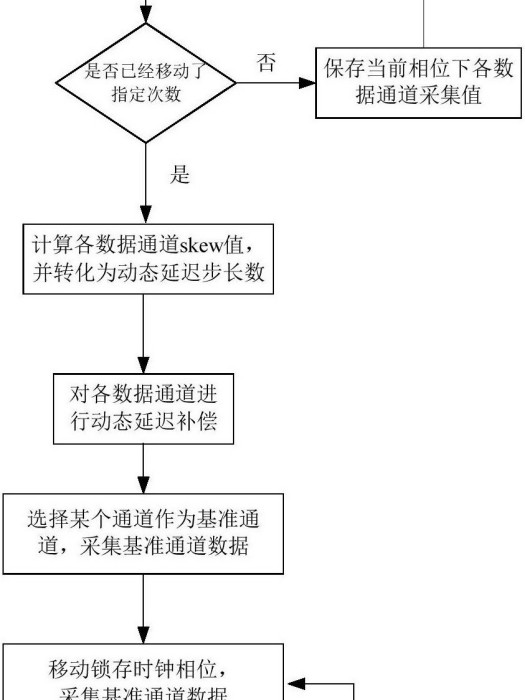

圖1為FPGA內de-skew算法實施流程圖;

圖2為《一種基於FPGA的多通道高速輸入信號自動de-skew方法》基本思路;

圖3檢測邊沿位置信息原理示意圖;

圖4動態延遲技術實現原理示意圖;

圖5設定數據鎖存觸發時刻為視窗中心點原理示意圖。

技術領域

《一種基於FPGA的多通道高速輸入信號自動de-skew方法》涉及高速數據採集技術,更具體的涉及一種基於FPGA的多通道高速輸入信號自動de-skew方法。

權利要求

1.《一種基於FPGA的多通道高速輸入信號自動de-skew方法》特徵在於,包括以下步驟:步驟(1)檢測並計算各數據通道間相對skew值;步驟(2)補償各數據通道的skew使得各數據通道對齊;步驟(3)將數據鎖存觸發信號對齊到鎖存視窗的中心;其中,所述步驟(1)中各數據通道間相對skew值的計算方法具體為:配置前端AD系統傳送訓練序列,使用FPGA內部鎖相環(PLL)產生鎖存時鐘,在鎖存時鐘的初始相位採集各數據通道數據,並將數據保存,然後動態調整鎖存時鐘的相位,每次移動一個步長,每移動一次採集一次各數據通道的數據並進行保存,鎖存時鐘的相位移動360度內可獲得各數據通道邊沿位置信息,在獲取到各通道掃描結果後,以邊沿最靠後通道作為參考通道,計算其他通道邊沿相對於該通道邊沿的差異,即可獲得各通道相對skew值。

2.根據權利要求1所述的一種基於FPGA的多通道高速輸入信號自動de-skew方法,其特徵在於,所述步驟(2)中對各通道進行延遲補償(de-skew)的過程具體為:將步驟(1)中計算得到的skew值換算為延遲步長,即可得到延遲單元數N(delay),對N(delay)取整,採用動態延遲技術,在工作過程中動態的設定各數據通道在鎖存之前的延遲,使得各通道邊沿完全對齊。

3.根據權利要求2所述的一種基於FPGA的多通道高速輸入信號自動de-skew方法,其特徵在於:所述各數據通道所採用的延遲補償是PVT修正的,所述PVT修正是根據工藝,電壓和溫度進行修正的。

4.根據權利要求3所述的一種基於FPGA的多通道高速輸入信號自動de-skew方法,其特徵在於,所述步驟(3)中將數據鎖存觸發信號對齊到鎖存視窗中心的方法為:以鎖存時鐘當前位置作為起點,每次移動一個步長進行掃描,選擇任意一個通道作為採集通道,採集該通道在當前相位下的值,直到採集到的值發生跳變停止掃描過程,根據採集的數據率計算將鎖存觸發時鐘對齊到視窗中心所需移動的步長,將鎖存觸發時鐘對齊到視窗中心。

實施方式

圖1、圖2所示,FPGA上電初始化後,使用其內部PLL產生數據鎖存時鐘,使能動態相位調整,並將步長設定為78.125ps。為使步長精度達到78.125ps,需要手工設定PLL的乘法和除法係數,使得PLL輸出VCO頻率達到最大值。完成鎖存時鐘準備後,下一步配置前端AD系統使產生0x55訓練序列,也即產生一個時鐘數據,便於邊沿檢測。在完成訓練序列產生後,配置PLL參數使得鎖存時鐘相位移動一個步長,即78.125ps,移動完成後,採集各數據通道值並保存;繼續移動鎖存時鐘相位,採集各通道數據並保存,直到完成指定次數的移動,(如圖3所示)。指定次數根據實際數據率計算得到,保證在指定次數內一定能檢測到數據跳變。在完成數據通道掃描後,根據保存的掃描序列計算各通道的skew值差異,通常以邊沿最靠後的通道作為參考通道計算其他通道相對於該通道的skew值,在得到各通道相對skew值後,根據延遲步長值,轉化為各通道需要延遲的單元數。這些單元數將被動態延遲補償模組(如圖4所示)使用對各個通道做相應的延遲,使得各通道邊沿完全對齊,以增大數據鎖存視窗。在完成各數據通道對齊之後,需要重新調整鎖存時鐘相位使得鎖存時刻位於視窗中心,這通過繼續移動鎖存時鐘相位檢測邊沿來完成,在檢測到邊沿後,繼續移動半個數據位寬即可將鎖存時刻固定在視窗中心位置,(如圖5所示),從而使得鎖存時刻達到最大冗餘度,充分保證數據鎖存的正確性。在完成de-skew之後,重新配置前端AD系統使退出訓練模式,進入到正常工作狀態,完成數據的正常採集工作。

榮譽表彰

2021年8月16日,《一種基於FPGA的多通道高速輸入信號自動de-skew方法》獲得安徽省第八屆專利獎優秀獎。