滑碼問題,準同步和主從同步,對時鐘的要求,同步網設備,幀同步和彈性存儲器,

滑碼問題

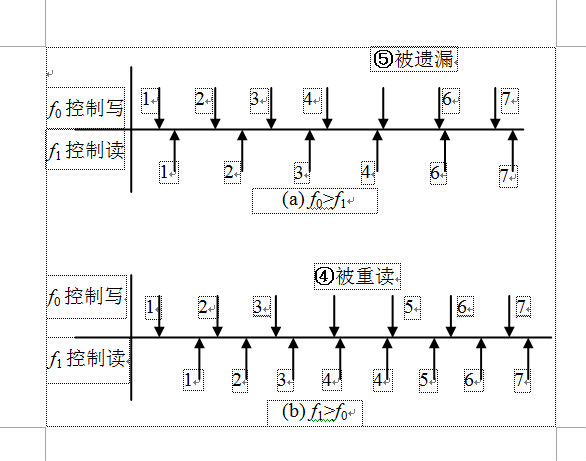

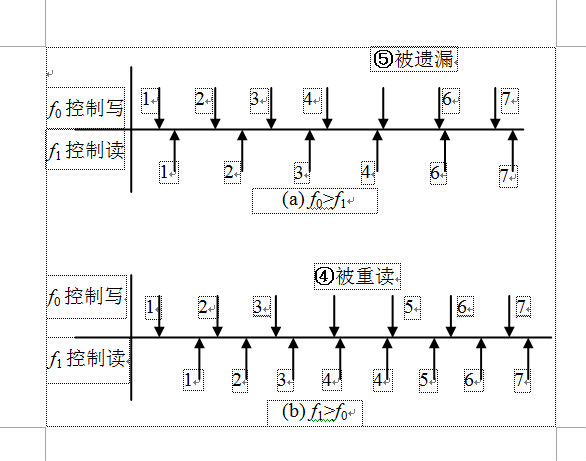

滑碼是數字交換的一個特殊問題,其起因是兩個數字交換局的頻率不相等。圖1是產生滑碼的原理圖。由圖可見,當本局時鐘頻率f1低於入局時鐘頻率f0時,會不斷產生遺漏一幀的情況(如第5次被遺漏)。如f1高於f0,會不斷產生重讀一幀的情況(如第4次被重讀)。頻率相差愈多,遺漏和重讀發生得愈頻繁。每發生一次遺漏或重讀,就稱為發生滑碼一次。不同頻率精度發生滑碼的頻繁程度見表1。滑碼和失步是兩個概念,不要混淆。在下面所述達到主從同步時,從理論上講,是不會發生滑碼的,但實際情況要複雜些,還會發生滑碼。隨著溫度變化,線路延遲也會變化,數碼會提前到來或推遲到來,這等效於頻率變化,當積累至一定值時,就會發生滑碼。

圖1 滑碼發生原理示意圖

表1 振頻精度和滑碼發生對照表

碼率(bit/s) | 頻率精度 | 每天發生的滑碼次數 | 每小時發生的滑碼次數 | 發生一次滑碼的間隔時間 | |

2×10 | 10 | 6.7×10次 | 2.8×10次 | 3.97年 | |

2×10 | 10 | 6.7×10次 | 2.8×10次 | 145天 | |

2×10 | 10 | 0.067次 | 2.8×10次 | 14.5天 | |

2×10 | 10 | 0.67次 | 0.028次 | 35小時 | |

2×10 | 10 | 6.72次 | 0.28次 | 12 800s | |

2×10 | 10 | 67.2次 | 2.8次 | 1 280s | |

2×10 | 10 | 672次 | 28次 | 128s | |

2×10 | 10 | 6 720次 | 280次 | 12.8s | |

一般程控交換機都具有滑碼超過規定值時即告警的性能,如告警時能顯示滑碼的方向(重讀或遺漏)則更佳。這個規定值應可通過人機通信加以改變。

滑碼對通信的影響,是隨著通信種類不同而各異的。在進行數據或圖像傳輸時,滑碼發生的後果很嚴重,但在通話時,滑碼就不那么嚴重了。有關資料表明,當頻率差為10時,也就是大致上每小時出300次滑碼時,才會在通話中聽到“喀嚦”聲,使通話受到嚴重影響。

ITU-T已對滑碼率的發生制定了詳細的要求,將滑碼率的發生分成四級,第一級是基本上無滑碼,或滑碼率少於70天一次;第二級是滑碼率多於70天一次,少於5小時一次;第三級是滑碼率多於5小時一次,少於2分鐘一次;第四級是滑碼率多於2分鐘一次。上述第一級是質量非常高的通信;第二級是滿意的;第三級質量低劣,通話尚可勉強進行,數傳就不行了;第四級是完全不能接受的。在一年內,屬於第四級的時間要少於0.1%,第三級要少於1%,第一和第二級要大於99%。應該注意,上面是端到端的指標。因一個通信要涉及許多交換局,因而每個交換局分配到的指標要比上面講的還嚴格。

準同步和主從同步

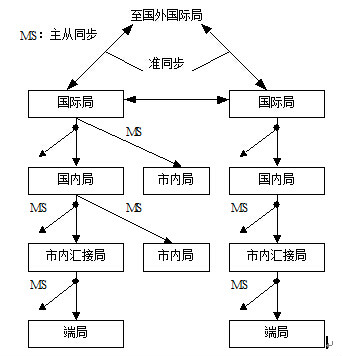

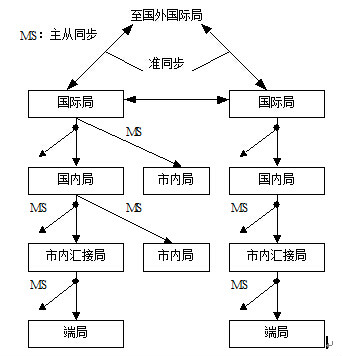

準同步和主從同步是解決網同步的兩種方法。所謂準同步是各數字交換局在時鐘上相互獨立,毫無關聯,但都具有極高的精度和穩定度,一般均採用原子鐘。由於精度高,網內各局的時鐘雖然並不完全相同,但誤差很小,接近同步。這就是準同步的意思。所謂主從同步,是指網內設一主局,配有較高精度的時鐘,網內其他各局均受控於該主局,並且逐級下控,直至終端局或遠端集線器。圖2是準同步和主從同步相結合的示意圖,圖中示出兩個國際局,這兩個國際局之間,以及其和國外的國際局之間,採用準同步。這兩個國際局各控制一批國內、市內局。

圖2 準同步和主從同步原理圖

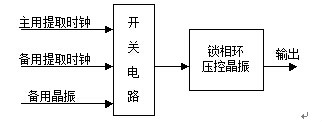

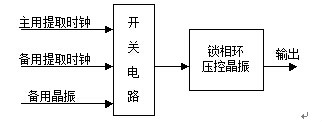

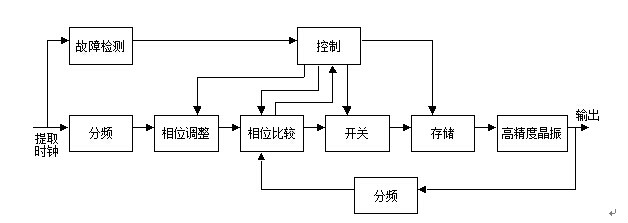

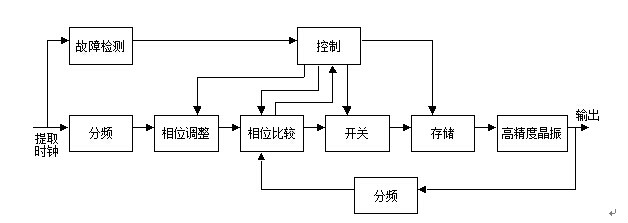

必須注意,在主局控制從局時,是控制整個從局的時鐘。一般的做法是,在主局和從局之間選擇主用路由和備用路由各一條,正常時由主用路由提取的定時去控制從局的鎖相振盪器,當主用路由失效時,就由備用路由提取的定時來控制。當主、備路由都失效時,就由備用晶振來工作。這方面的安排見圖3,為緊耦合主從同步。圖4是另一種松耦合主從同步方框圖。由圖4可見,這種方式只要一個提取時鐘進行控制,不需要備用的提取時鐘,更不需要備用晶振。當輸入的提取時鐘正常時,控制器使相位調整、

圖3 緊耦合主從同步示意圖

圖4 松耦合主從同步示意圖

相位比較和開關等電路起作用,輸入的提取時鐘經分頻後的信號,和高精度晶振輸出經分頻後的信號進行相位比較。比較後的誤差輸出通過開關,變換成數位訊號存入存儲器,存儲器的讀出再變換成電壓信號去控制高精度晶振,使高精度晶振的輸出頻率鎖定於輸入的提取時鐘,以達到主從控制的目的。由上面的敘述可知,松耦合的控制原理和通常的鎖相環相似,只不過中間增加了電壓—數字變換以及數字—電壓逆變換罷了。由於數位訊號(代表頻率漂移)控制十分精細,所以松耦合主從控制的精度非常高。當輸入的提取時鐘失效時,通過故障檢測電路,使控制器將開關電路等封閉,從而使存儲器能保持失控時的值,也就是說有了“記憶”功能,因而也使高精度晶振輸出維持原來的頻率和相位。據稱,松耦合主從控制可以達到幾天內保持頻率漂移小於10/天的水平,而在這期間輸入的提取時鐘總能修復的。由此可見,松耦合主從控制比緊耦合主從控制要優越得多。

對時鐘的要求

時鐘是數字程控交換機等設備的一個重要部件,它的好壞直接對網同步的各項技術指標發生影響,必須給予足夠重視。

對時鐘一般提出3個要求:第1個要求是精度,是指時鐘頻率相對於其標稱頻率的頻率偏移絕對值的衡量,有一個最低準確度的要求,即最多允許的偏移。第2個要求是穩定度,是指在失去同步的情況下,時鐘頻率的變化,有一個最低穩定度的要求,即在一定時間內最多允許頻率變化多少。第3個要求是牽引範圍,即在有同步控制的情況下,能在多大的頻率變化範圍內仍能達到同步。

實際套用的時鐘一般分為3個等級,即銫原子鐘時鐘,高穩定度晶振以及低穩定度晶振,它們的精度、穩定度和牽引範圍分別如下所述。

銫原子鐘時鐘:在精度方面其最低準確度優於1×10,長期穩定性可達1×10/年,無牽引範圍可言,因為這種鐘是作為基準時鐘,用於控制其他時鐘的,不存在再受其他時鐘控制的情況。

高穩定度晶振時鐘:在精度方面其最低準確度一般在10~10之間,長期穩定性一般優於10/天,牽引範圍一般在10~10範圍。

低穩定度晶振時鐘:在精度方面其最低準確度一般在10~10之間,長期穩定性優於10/天,牽引範圍可在10~10之間。

一般銫原子鐘只作為基準時鐘用,因為它的價格非常高昂。省中心以上的長途局,特大城市和大城市的市話匯接局等可考慮採用高穩定晶振時鐘;縣中心局、小城市的長途局,一般市話端局以及再以下的局可考慮採用低穩定度晶振時鐘;至於地區中心局,中等城市等局,可在高穩定性晶振和低穩定性晶振之間選用。隨著技術的進步,電子設備和器件的不斷降低價格,採用高穩定性晶振的場合越來越多。

同步網設備

上面所述的主從同步,原來都是採用提取定時的方法實現的,即在上級局至下級局的數字中繼中,在到達下級局後進行定時提取,作為同步控制用。實踐證明這種實現方法有些缺陷,主要是數字碼流在傳輸過程中會發生一些漂移和抖動,這種漂移和抖動將對同步產生影響。隨著傳輸距離延長,漂移和抖動將加劇,對同步產生的影響也加重。

為了解決這個問題,世界各國都發展了一些同步網設備,如美國的大樓綜合定時系統(BITS),歐洲的同步供給單元(SSU)等,用了這些同步網設備後,就可取代定時提取而達到同步控制目的。實現的機理很簡單,即在最高級設定穩定性非常高的時鐘,用專用的傳輸鏈路逐級往下級的區域性基準鐘或大樓綜合定時系統送,在其中對收到的定時進行處理,除去漂移和抖動,獲得良好的時鐘,再輸出到各種程控交換機等設備,進行同步控制,由於已經除去了漂移和抖動,使同步獲得滿意的效果。

我國已在全國建立同步網,全國最高級基準時鐘PRC設在北京和武漢,各設一個銫原子鐘和GPS(全球定位系統)接收機,其輸出往下輸送至區域基準時鐘LPR。全國省中心以上城市各設一個LPR,在LPR中除接收PRC的時鐘外,也設GPS接收機和一個銣原子鐘(精度比銫原子鐘稍差)。LPR的時鐘再輸出至下級的BITS,BITS的輸出就可供給各種程控交換機等設備作為同步控制用了。用了BITS的控制後,原來的定時提取控制就可不用,同步效果得到很大的改善。在某些場合,BITS輸出一時不能到達,或在距離較近的市(縣)內某些局之間,仍可使用定時提取的同步控制方法。

幀同步和彈性存儲器

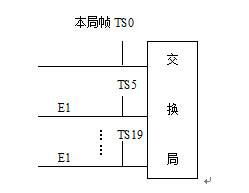

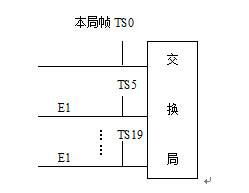

一個交換局往往用很多個E1連線至不同的交換局,這些E1的2Mbit碼流在到達此交換局後,在時間上往往是對不齊的,如圖5所示,在本局幀結構的TS0時間,第一個E1的時間是在TS5,另一個E1的時間是在TS19,等等,因為這個交換局和各局的距離不同,時延也不相同,各局的幀結構本來也是各自獨立產生的,因此造成如圖5所示的情況是十分正常的。幀同步的目的就是要解決各個E1的碼流到達後和本局的幀結構對齊。

圖5 各局碼流和本局幀不同步示意圖

早期的數字程控交換機採用可控延線來解決幀同步問題。每個E1終端需裝可控延遲線一個。可控延遲線提供的最大延遲是125µs,在提取的外界TS0和本局TS0比較下,可控延遲線由伺服馬達控制提供適當的延遲,使外界碼流抵達數字交換網時,恰巧和本局定時對齊而達到幀同步。當外界TS0和本局TS0相差有變動時,隨時調整延遲以保持同步。

後來出現了由可控移位暫存器或隨機存儲器實現的彈性存儲器。採用移位暫存器實現彈性存儲器時,每移1bit,延遲0.488µs (2Mbit碼流時),則移位256bit就等於提供約125µs延遲了。如果彈性存儲器由256bit可控移位暫存器組成,並可在外界TS0和本局TS0的相差控制下,自動提供0~255bit間任何比特的移位,則其作用原理和可控延遲線完全相同。

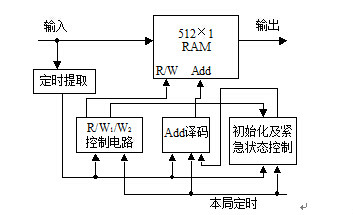

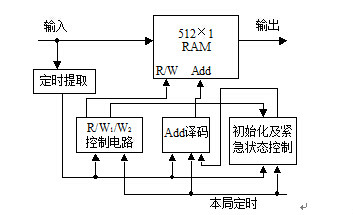

圖6示出一個由雙幀RAM實現的彈性存儲器,RAM的容量是512×1。輸入信息在提取的定時控制下存入RAM;然後在本局的定時控制下,從RAM讀出。

彈性存儲器統一由本局定時讀出,不論外界提取的定時發生在什麼時間,顯然均能達到幀同步。彈性存儲器的關鍵是儘可能使本局定時和提取定時相差更多的時間,圖6中的初始化及緊急狀態控制電路能在彈性存儲器剛開始工作時使本局定時和提取定時相差一幀時間。但是由於提取時鐘和本局時鐘的頻率不可能完全相同,隨著時間的推移,本局定時和提取定時將趨於接近,而產生滑碼。圖6中的初始化及緊急狀態控制電路可在發生滑碼時,立即將本局定時和提取定時拉開一幀的距離,這就減少或避免了滑碼的發生及其對通信質量的影響。

圖6 雙幀RAM實現的彈性存儲器原理圖