HSTL(High Speed Transceiver Logic)是由JEDEC(Joint Electron Device Engineering Council,屬於電子工業協會EIA)在1995年正式制定的一種電路邏輯標準。

基本介紹

- 中文名:HSTL

- 外文名:High Speed Transceiver Logic

- 制定時間:1995年

- 制定機構:JEDEC(Joint Electron

定義,介紹,

定義

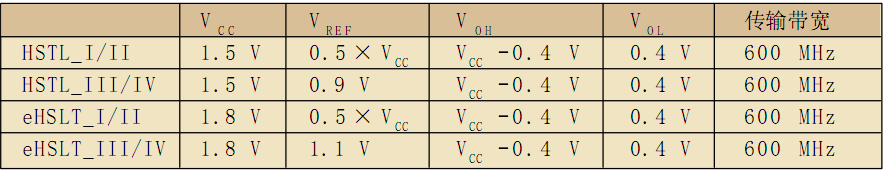

HSTL和eHSTL邏輯電平標準

HSTL和eHSTL邏輯電平標準HSTL是一種技術獨立的數字積體電路接口標準,為了實現電壓擴展和技術獨立I/O結構而開發的。

介紹

此標準所要求的I/O結構是差分放大輸入(一個輸入內部關聯成一個用戶提供的輸入參考電壓,此電壓用於單端輸入)和使用Vcco的輸出。所謂技術獨立,實際上指用來做輸入參考和輸出Vcco的電壓,與器件本身的供電電壓不同。

HSTL最主要的套用是可以用於高速存儲器讀寫。傳統的慢速存儲器訪問時間阻礙了高速處理器的運算操作。在中頻區域(100MHz和180MHz之間),可供選擇基於單端信號的I/O結構有:HSTL、GTL/GTL+、SSTL和低壓TTL(LVTTL)。在180MHz以上的範圍,HSTL標準是唯一可用的單端I/O接口。利用HSTL的速度,快速I/O接口明顯地提高了整個系統的性能。HSTL是高速存儲器套用的I/O接口選擇,同時也很完美地提供了驅動多個記憶體模組地址匯流排的能力。