實現H.324可視電話終端的方法很多,大致可以分成三種方案,一是以超大規模集成專用晶片為核心的方案;二是以PC為主機用軟硬體混合實現的方案;三是以PC機為主機使用軟體的實現方案。隨著PC速度及功能的不斷提高,尤其是多媒體計算機的出現,以PC為主機基本使用軟體來實現H.324可視電話的方案將成為主流。

基本介紹

- 中文名:H.324型終端組成的可視電話系統的實現

- 1:超大規模集成專用晶片為核心

- 1.1:LVP低碼率可視電話處理器

- 1.2:NP501可視電話加速器

1.超大規模集成專用晶片為核心的系統,1.1 LVP低碼率可視電話處理器,1.2 NP501可視電話加速器,2.以PC為主機軟硬體混合實現的方案,3.以PC為主機來實現的方案,

1.超大規模集成專用晶片為核心的系統

H.324終端中的各部分功能均用超大規模集成專用晶片完成,加上小型CCD攝像機及小型液晶監視器構成了一個完整的可視電話終端。該方案的優點是體積小,便於攜帶,使用方便,由於採用硬體設備,故信息處理速度快,圖像與語音質量好。現舉例說明之。

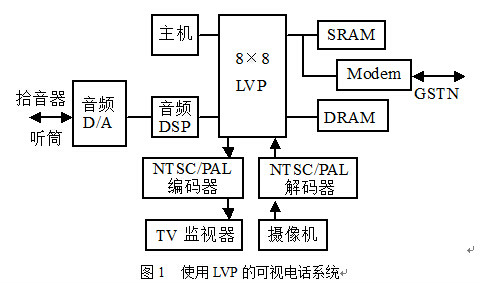

1.1 LVP低碼率可視電話處理器

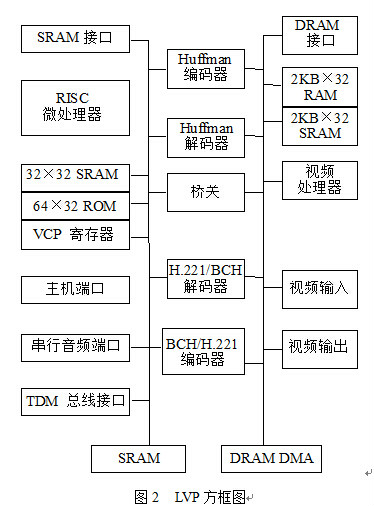

圖1為使用8×8 LVP單片可程式可視電話處理器為核心組成的可視電話系統方框圖。它具有分離的數字視頻匯流排,即輸入及輸出數字視頻匯流排。在單片LVP內部其結構如圖2所示。這是一塊240隻腳的LSI晶片。LVP晶片的內部匯流排及外部接口均分成兩組,一組對未壓縮的數據及中間的數據進行管理,另一組則管理壓縮的數據。視頻輸入及輸出匯流排供未壓縮的數據進出晶片。在匯流排中有兩個主要的數據通路,其中DRAM匯流排傳遞未壓縮的數據或中間數據,而SRAM匯流排則傳遞壓縮的數據和RISC指令及數據。和內部匯流排相聯繫的兩個DMA控制器(SRAM及DRAM)控制通過系統的數據通道。這些功能均是在RISC處理器的管理下進行的。

LVP的結構提供了靈活的視頻處理能力、在DRAM及SRAM間的數據轉移及數個壓縮數據的接口。下面介紹各功能塊的功能。① RISC微控制器

LVP的RISC是32位指令、32位數據的流水線形式精簡指令集的(RISC)微處理器,其指令和數據存儲在外接SRAM中,它沒有指令高速快取器,但通過32位接口可對外接SRAM進行高速訪問。當軟體初始化時,指令碼字可通過兩種方法下載到SRAM中,一是將碼字存儲在和LVP SRAM連線的EPROM中進行下載;二是通過外接主機將碼字下載到LVP中。當採用外接LVP EPROM時,設定LVP的插腳ROMDIS使LVP從外接ROM啟動。LVP RISC 有著少量的片內SRAM用來保存數據。LVP RISC有著流水線的結構,它使用增強的最佳化“C”語言編譯器,對其進行編程。

② SRAM接口及控制器

SRAM接口控制所有對LVP SRAM的訪問,SRAM的主要套用是對LVP RISC程式、堆疊及數據的存儲。它用來對視頻碼流的緩衝存儲及視頻碼速的緩衝。

SRAM DMA控制器是一個8通道的DMA控制器,它用來在SRAM及TDM、音頻、橋關及主機間進行快速的數據傳遞。

通過DMA連線SRAM的通信方法有三種,每一種均可在軟體的控制下實現系統中LVP與其他器件的通信。在大多數套用中,TDM連線埠是不用的,而音頻串列口則連線到DSP實現G.723的處理,亦可將G.723放在晶片中,這樣音頻串列口將通過A/D及D/A傳送未壓縮的數據。在PC套用時主機其內部包括一隻RISC微處理器及微碼視頻信號處理器。連線埠連線到PC的外圍匯流排中,在單獨套用時連線到一個微控制器中。

③ DRAM控制器及接口

DRAM DMA控制器通過多個通道實現DRAM及視頻接口、橋關、視頻處理器(VPe)、DRAM刷新之間的32位的數據傳遞。

DRAM接口提供了與DRAM存儲器晶片的連線,它使用1片、4片或16片DRAM支持512KB至8MB的存儲。

在典型的GSTN可視電話套用中,LVP只需使用單片256×16DRAM。

④ 視頻處理器及視頻的輸入與輸出

視頻處理器的核心功能是實現可程式的視頻信號處理功能,它執行MPEG、JPEG、H.261及H.263建議及其他優選算法的壓縮編解碼運算。使用微碼軟體實現視頻的預處理及後處理,以使LVP提供高質量的編碼與解碼圖像。

視頻處理器的微碼程式存放在2KB的片內ROM中。視頻輸入部分將捕獲的視頻幀數據存放在DRAM中,它提供了硬體預處理,對進入的視頻進行緩衝。抽選濾波器實現CCIR601圖像與SIF、CIF、QCIF及Sub-QCIF圖像之間的轉換。時域濾波器用來提升圖像質量,在低碼率套用時特別有用。視頻輸入還包含一個可程式的CRT控制器,使之鎖定在外接的視頻源上。

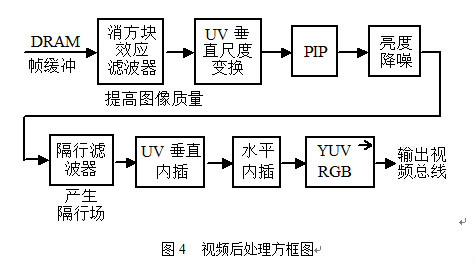

視頻輸出部分顯示存儲在DRAM中的視頻幀。它亦提供了硬體的後處理功能,它能對輸出的視頻信號進行緩衝,還能進行彩色變換、多抽頭的抽選濾波及內插濾波。

抽選和內插濾波實現在SIF、CIF、QCIF及Sub-QCIF與顯示格式之間的格式變換,實現CCIR601或VGA640×480的顯示。視頻輸出還包含一個可程式的CRT控制器實現隔行掃描或逐行掃描。為了實現電視顯示的隔行掃描,一個時域的隔行濾波器可提高圖像質量。CRT控制器亦可程式產生視頻同步及消隱信號,給外接視頻源用。

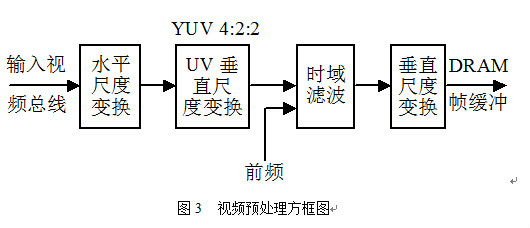

圖3為視頻預處理的方框圖,而圖4為視頻後處理方框圖。

1.2 NP501可視電話加速器

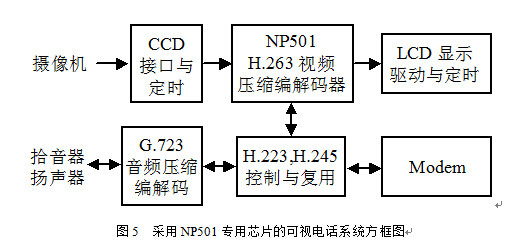

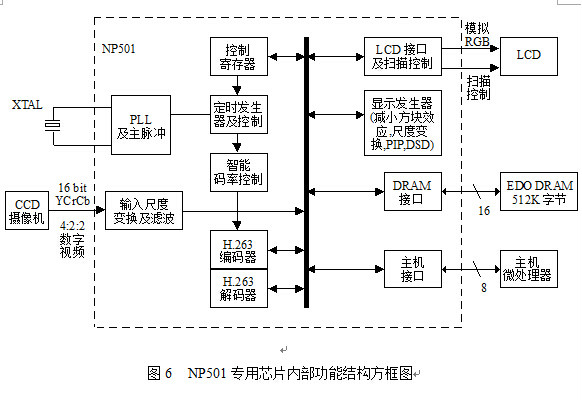

圖5為採用NP501可視電話加速器專用晶片構成的可視電話系統方框圖,而圖6則為NP501專用晶片內部功能結構方框圖。

NP501的主要特點有:

· 是符合ITU-T H.263及H.261視頻編碼標準的多標準的視頻編解碼器。

· 具有TFT LCD直接驅動的液晶顯示接口,包括掃描控制及模擬RGB視頻輸出。

· 具有工業標準的16bit YCbCr 4∶2∶2的數字視頻輸入。

· 同時進行編碼與解碼。

· 刷新速率:對SQCIF及QCIF(176×144)圖像為30幀/秒,對CIF(352×288)圖像為15幀/秒。

· 輸入尺度變換使圖像從攝像機清晰度變換為QCIF或CIF的清晰度。

· 支持H.263附錄F中的高級預測模式及附錄D.1中的無約束運動矢量模式,提高編碼效率。

採用一片微處理器作為主計算機通過8bit接口進行通信。通過可程式的控制暫存器的設定建立器件的運作。在電源接上後工作頻率、攝像機接口及顯示定時設定等由系統設定進行初始化。

一外接的DRAM提供了工作時的緩衝存儲及系統顯示幀緩衝器。對於QCIF格式的視頻編解碼512KB的DRAM是恰當的。而對於CIF格式圖像,應選擇較大的存儲器結構。一隻1MB的存儲器接口支持QCIF/CIF組合清晰度的編解碼。一隻2MB的存儲器接口支持CIF格式的編解碼。

NP501中包含片內PLL及定時產生電路以產生內部時鐘及視頻輸出定時。一個標準的14.318MHz晶體作為時基。該器件使用可程式處理器使之工作在40MHz至60MHz的工作頻率上。

NP501總共有208隻腳,運行在f=54MHz,電源電壓為5V時,功耗為1.5W。

2.以PC為主機軟硬體混合實現的方案

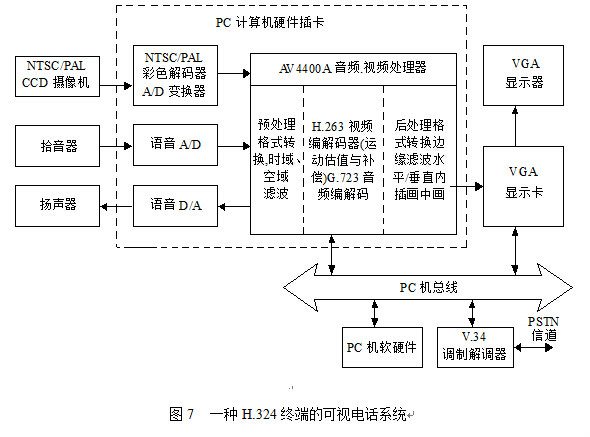

此種方案以PC為主機,如採用330MHz具有MMX多媒體匯流排的奔騰ⅡPC,外加一塊硬體插卡,此插卡上硬體除了完成彩色電視信號(NTSC或PAL)的解碼(包括A/D變換)及語音信號的A/D和D/A變換外,還使用硬體完成H.324終端中視頻、音頻信源編解碼等運算量大的功能,而控制(H.245)、復用(H.223)及與Modem接口等功能則由PC軟體完成。圖7畫出了一種實現此方案的可視電話系統框圖。圖中H.263視頻編解碼,G.723音頻編解碼器等主要功能使用AT&T公司的AV4400A超大規模積體電路完成。該積體電路還完成視音頻信號的預處理及後處理功能。H.324的控制及復用功能及與數據機的接口等均使用軟體完成。

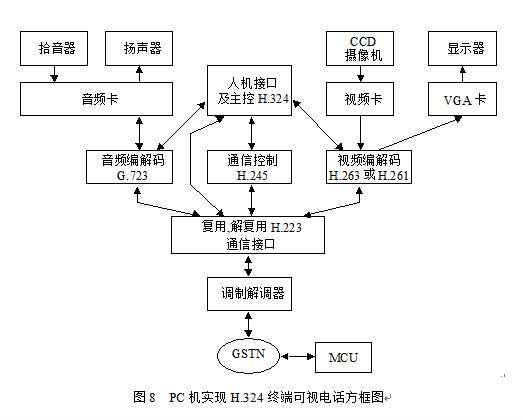

3.以PC為主機來實現的方案

這一方案除了NTSC/PAL彩色解碼器、視頻A/D變換器(視頻卡)及音頻A/D、D/A變換器(音頻卡)外,其他功能均可用軟體實現。在多媒體計算機上採用Win95開發平台,使用VC++5.0及Windows SDK進行編程,採用多執行緒編程技術,在Win95平台上實現並行的模組化處理。整個軟體可分為人機接口及主控、通信控制、音頻編解碼、視頻編解碼、復用、解復及通信接口等部分組成。如圖8所示。它是一個以軟體為主的H.324可視電話終端,由於是軟體為主,故便於性能的改進與升級。其中主控H.324是系統的核心,是控制信息處理中心,它對系統進行初始化,啟動、監控、終止其他模組,主機實現H.324的功能,對整個系統實現控制。通信控制模組主要實現H.245的功能,實現在終端之間協商通信方式、設定通信參數,並對通信過程進行監控。音頻編解碼模組對音頻卡來的數字語音信號進行G.723信源編碼,並對其他終端傳來的數字語音信號進行G.723信源解碼。視頻編解碼模組則實現H.263或H.261的視頻信源編解碼。復用、解復及通信接口模組用軟體實現H.223建議的功能,與數據機接口,完成數據流的適配與復用、解復等功能,在傳輸碼流及各種數據流之間進行轉換。