EDK介紹 嵌入式系統 經歷了從

單片計算機 、

工業控制計算機 、集中

分散式控制系統 ,發展到嵌入式的平台的幾個階段:從獨立單機使用發展到聯網設備;從以模擬電路為主發展到以數字電路為主、數/模混合型,進而進入全數字時代。總的來說,嵌入式系統向著更高性能、更小體積、更低功耗、更廉價、無處不在的方向發展。嵌入式系統的設計和實現朝著基於晶片,特別是片上可程式系統(SOPC)的方向發展。

嵌入式開發 套件(EDK)是用於設計嵌入式可程式系統的全面解決方案。該套件包括嵌入式軟體工具(Platform Studio)以及嵌入式IBM PowerPC硬體處理器核和/或Xilinx MicroBlaze軟處理器核進行Xilinx平台FPGA設計時所需的技術文檔和IP。注意,這裡的嵌入式軟體工具指用來產生、編輯、編譯、連結、載入和調試高級程式語言(通常是C或C++)代碼的工具,以便在處理器引擎上執行。

由於

嵌入式系統 涉及了軟體和硬體的開發以及兩者的綜合設計,因此其開發是較為複雜的。Xilinx為了簡化基於FPGA的

嵌入式開發 流程,提供了功能強大、操作簡單的工具集:集成

軟體環境 ——ISE;嵌入式開發套件——EDK。(注釋:ISE 是Xilinx 公司FPGA

邏輯設計 的基礎。在這個環境中,設計者可以進行約束檔案的編寫,時序分析,邏輯布局布線以及器件編程等。)

EDK自帶了許多工具和IP,可以用來設計完整的

嵌入式處理器 系統,主要包括Xilinx 平台工作室XPS和軟體開發套件SDK。需要注意的是:只有安裝了ISE軟體,才能正常運行EDK,且二者的版本要一致。

EDK的組成模組有:

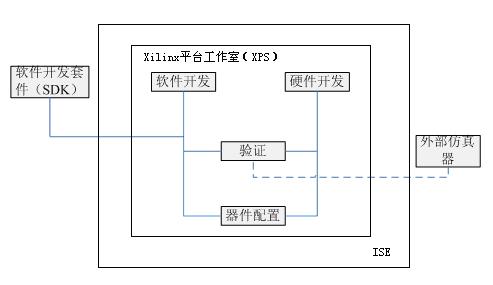

1.Xilinx 平台工作室(Xilinx Platform Studio,XPS)

XPS 是用來設計嵌入式處理器系統硬體部分的開發環境或GUI,是系統設計者構建 Xilinx

嵌入式系統 時必用的工具套件。在XPS中,可以完成嵌入式系統架構的創建、

軟體代碼 的編寫、設計的編譯以及FPGA晶片的

硬體配置 。

2.軟體開發套件(Software Development Kit,SDK)

SDK是集成的

開發環境 ,基於Eclipse。它支持C/C++,用於嵌入式軟體套用的開發和驗證。

3.其它EDK部分

EDK還包括其它的一些部分,如:用於Xilinx

嵌入式處理器 的硬IP;用於嵌入式軟體開發的驅動和庫;在MicroBlaze和PowerPC處理器上用於C/C++軟體開發的GNU編譯器和調試器;有關文檔以及一些工程樣例等。

Xilinx的

嵌入式開發 套件EDK帶有許多的工具和IP,可以用來設計完整的嵌入式處理器系統,並在Xilinx FPGA晶片上運行。EDK中包含了開發硬體和軟體所必須的全部工具,可以很方便的添加系統自帶的IP核和用戶自定義的IP核,可以通過調用ISE等其他工具實現布局布線,時序最佳化等等。可以調用GDB對應用程式進行板上調試及虛擬平台調試。

實現流程 2.1、基於EDK的開發流程

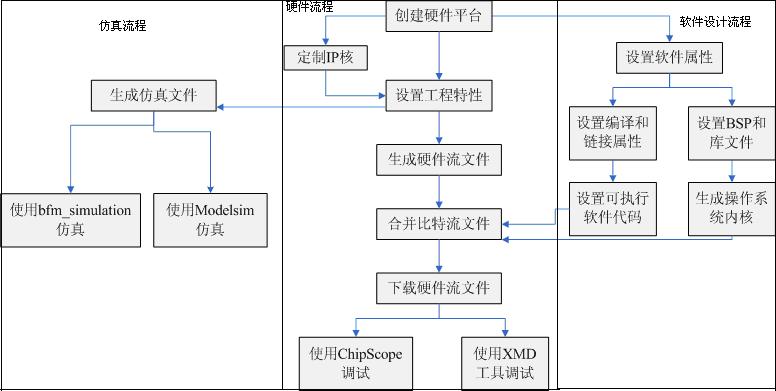

一個完整的嵌入式設計流程包括硬體設計和調試、

軟體設計 與調試,各個步驟相對獨立但又相輔相成。由於嵌入式套用場合多樣,且軟、硬體都可裁剪,因此並不是每個設計都要完成所有的步驟。圖中為基於EDK 的嵌入式設計的簡化流程圖。

簡化的嵌入式設計流程圖 通常,ISE FPGA 開發軟體在後台運行,XPS 工具調用ISE 軟體提供的功能。XPS 主要用來

嵌入式處理器 硬體系統 的開發。

微處理器 、外圍設備以及這些組件之間的連線問題,另外還有它們各自的屬性設定都在XPS 里進行。簡單的軟體開發可以在XPS 里完成,而對於更複雜的套用開發和調試,Xilinx 則推薦使用SDK 工具。硬體平台的功能驗證可以通過硬體描述語言HDL

仿真器 完成。XPS 提供了行為級、結構級以及定時精確級等三種類型的仿真。驗證過程結構由XPS 自動產生,其中包括了仿真的HDL 檔案。設計者只需要輸入時鐘時序、重配置信息以及一些套用代碼即可。仿真細節將在下面的內容中進行相關講述。完成設計後,在XPS 中將FPGA 比特流和可執行可連結格式檔案下載,就可以進行目標器件的配置。

完整的EDK 開發流程如右圖 所示,其主要步驟有:1. 創建硬體平台:利用XPS 的板級開發包嚮導(BSB Wizard)快速構建設計的硬體平台,是EDK 設計的第一步。

完整的嵌入式設計流程圖 2. 添加IP Core 以及用戶定製外設:在XPS 中添加所需的IP Core,對於XPS 庫中缺少的模組,需要用戶自行設計。同樣,XPS 提供了建立用戶自定義外設的嚮導,可簡化該過程。

3. 生成仿真檔案並測試

硬體系統 :生成硬體系統的仿真檔案,可選擇行為級、結構級以及時序級仿真,利用ModelSim等工具測試系統,特別是用戶自定義的外設;如果測試失敗,需要返回上一步修改。

4. 生成硬體比特流:生成硬體網表和比特流檔案,這個步驟類似於傳統FPGA 設計的綜合、布局布線、生成編程檔案這3 個操作。

5. 開發軟體系統:針對

軟體需求 編寫硬體代碼,確定軟體的作業系統、庫、外設驅動等屬性,針對每個套用軟體工程,設定編譯器、最佳化級別、使用的連線檔案等信息。等設定完成後,編譯生成.elf 格式的

可執行代碼 。

6. 合併軟、硬體比特流:編譯軟體後,需要將軟、硬體

執行檔 合併在一起,生成最終的二進制比特檔案。

7. 下載:使用JTAG編程電纜或

編程器 將更新後的最終比特流燒寫到 FPGA、PROM、FLASH以及CF 卡。

8. 線上調試:可利用XMD工具或ChipScope 工具調試,通過JTAG編程電纜線上調試,下載可執行

軟體代碼 、控制執行,並監控相關信息。

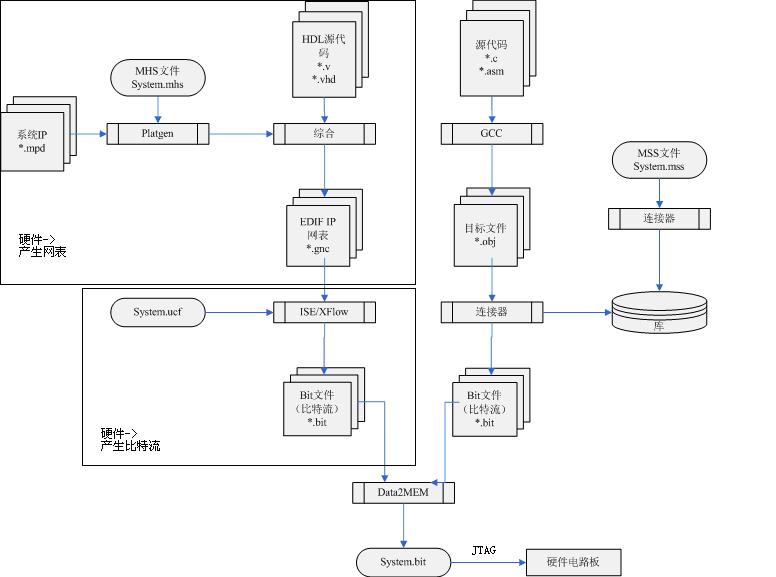

2.2、EDK設計比特檔案的組成

如前所述,最終下載到FPGA 的嵌入式比特流檔案是軟、硬體比特流合併在一起的,詳細的組成部分如右圖所示。硬體部分比特流包括MHS 檔案、用戶自定義HDL 代碼,二者經過綜合實現後,產生.ngc 網表,生成

硬體系統 的比特流檔案;軟體系統包括 MSS 檔案、用戶.c/cpp/asm檔案,通過GCC 編譯器,生成目標檔案.obj,再經過連線合成軟體系統的比特流檔案;最後通過Data2MEM過程,將軟、硬體比特流合成完整系統比特流檔案,通過JTAG鏈路下載到FPGA 晶片中。

EDK 配置比特檔案的組成結構 添加IP 安裝時候需要版本搭配,如ISE8.1搭配EDK8.1。首先,說說使用EDK加入用戶設計的IP。

1、啟動XPS(xilinx platform studio),生成一個processor system,其中可以選擇處理器,硬IP(powerpc)或軟IP(

microblaze ),以及可選的IP(BRAM、UART)等。如果這個階段拿不定不要什麼IP,以後添加刪除都可以。

2、啟動Create and Import Peripheral Wizard,創建IPIF,選擇需要的屬性,如是否包括FIFO、DMA等,系統會自動創建HDL文檔模板,用戶只需要添加

用戶程式 部分。同coreconnect匯流排連線部分不用用戶操心。

3、使用ISE的Project Navigator,打開第二步生成的.npl檔案,添加入自己的代碼,在ISE里進行編譯。

5、若在第三步里,用戶對接口有修改,需要重新啟用Create and Import Peripheral Wizard,來生成EDK接口(.pao/.mpd檔案)

6、使用XPS - Add/Edit Core Dialog,添加用戶IP到第一步的工程中

7、使用XPS生成IP driver。

簡化的嵌入式設計流程圖

簡化的嵌入式設計流程圖 完整的嵌入式設計流程圖

完整的嵌入式設計流程圖 EDK 配置比特檔案的組成結構

EDK 配置比特檔案的組成結構