74ls164、74lsT164是高速矽門CMOS器件,與低功耗肖特基型TTL(LSTTL)器件的引腳兼容。

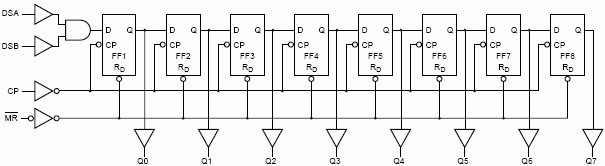

74HC164、74HCT164是8位邊沿觸髮式移位暫存器,串列輸入數據,然後並行輸出。數據通過兩個輸入端(DSA或DSB)之一串列輸入;任一輸入端可以用作高電平使能端,控制另一輸入端的數據輸入。兩個輸入端或者連線在一起,或者把不用的輸入端接高電平,一定不要懸空。

基本介紹

- 中文名:74ls164

- 作用:8 位串入,並出移位暫存器

- 解釋:高速矽門 CMOS 器件

- 強制:所有的輸出為低電平

功能作用

概述

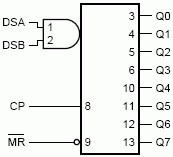

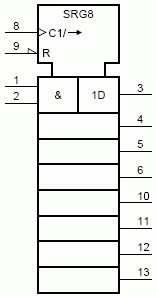

功能圖

特性

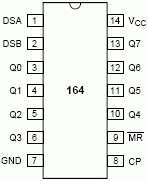

引腳信息

符號 | 引腳 | 說明 |

DSA | 1 | 數據輸入 |

DSB | 2 | 數據輸入 |

Q0~Q3 | 3~6 | 輸出 |

GND | 7 | 地 (0 V) |

CP | 8 | 時鐘輸入(低電平到高電平邊沿觸發) |

/M/R | 9 | 中央復位輸入(低電平有效) |

Q4~Q7 | 10~13 | 輸出 |

VCC | 14 | 正電源 |

電氣特性

符號 | 參數 | 測試條件 | 最小值 | 典型值 | 最大值 | 單位 |

VI | 輸入鉗位電壓 | VCC = Min, II = -18 mA | - | - | -1.5 | V |

VOH | 輸出高電平電壓 | VCC = Min, IOH = Max VIL = Max, VIH = Min | 2.7 | 3.4 | - | V |

VOL | 輸出低電平電壓 | VCC = Min, IOL = Max VIL = Max, VIH = Min | - | 0.35 | 0.5 | V |

IOL = 4 mA, VCC = Min | - | 0.25 | 0.4 | |||

II | 最大輸入電壓時輸入電流 | VCC = Max, VI = 7V | - | - | 0.1 | mA |

IIH | 輸入高電平電流 | VCC = Max, VI = 2.7V | - | - | 20 | μA |

IIL | 輸入低電平電流 | VCC = Max, VI = 0.4V | - | - | -0.4 | mA |

IOS | 輸出短路電流 | VCC = Max (Note 4) | -20 | - | -100 | mA |

ICC | 電源電流 | VCC = Max (Note 5) | - | 16 | 27 | mA |

符號 | 參數 | To (Output) | RL = 2kΩ | 單位 | |||

CL = 15 pF | CL = 50 pF | ||||||

最小值 | 最大值 | 最小值 | 最大值 | ||||

fMAX | 最大時鐘頻率 | - | 25 | - | - | - | MHz |

tPLH | 低到高電平輸出傳遞延遲時間 | 時鐘輸出 | - | 27 | - | 30 | ns |

tPHL | 高到低電平輸出傳遞延遲時間 | 時鐘輸出 | - | 32 | - | 40 | ns |

tPHL | 傳遞延遲時間 | 時鐘輸出 | - | 36 | - | 45 | ns |

功能表

工作模式 | 輸入 | 輸出 | 備註 | |||

/M/R | CP | DSA | DSB | Q0 | Q1 至Q7 | |

L | L | X | X | L | L 至 L | 復位(清除) |

H | ↑ | l | l | L | q1至q7 | 移位 |

H | ↑ | l | h | L | q1至q7 | |

H | ↑ | h | l | L | q1至q7 | |

H | ↑ | h | H | H | q1至q7 | |

工作條件

符號 | 參數 | 最小值 | 典型值 | 最大值 | 單位 |

VCC | 電源電壓 | 4.75 | 5 | 5.25 | V |

VIH | 輸入高電平電壓ViH | 2 | - | - | V |

VIL | 輸入低電平電壓ViL | - | - | 0.8 | V |

IOH | 輸出高電平電流IOH | - | - | -0.4 | mA |

IOL | 輸出低電平電流IOL | - | - | 8 | mA |

fCLK | 時鐘頻率fCP | 0 | - | 25 | MHz |

tW | 脈衝寬度 | 時鐘 | 20 | - | ns |

清除 | 20 | - | - | ||

tSU | 數據設定時間 | 17 | - | - | ns |

tH | 數據保持時間 | 5 | - | - | ns |

tREL | 建立時間 | 30 | - | - | ns |

TA | 工作溫度 | 0 | - | 70 | ℃ |

時序圖