為了開拓64位處理器的高端套用市場,1994年6月Intel和HP公司簽署合作協定,共同開發以伺服器和T作站為主要套用目標的全新64位架構高性能微處理器。1997年11月,Intel和HP公司發布基於EPIC(Explicitly Parallel Instruction Computing,顯式並行指令計算)的Itanium系統結構。

基本介紹

- 中文名:顯式並行指令計算

- 外文名:Explicitly Parallel Instruction Computing

- 簡稱:EPIC

- 處理器:64位

- 定義:簡化處理器,使高度變化成為可能

- 套用學科:計算機原理

概述,結構,特點,

概述

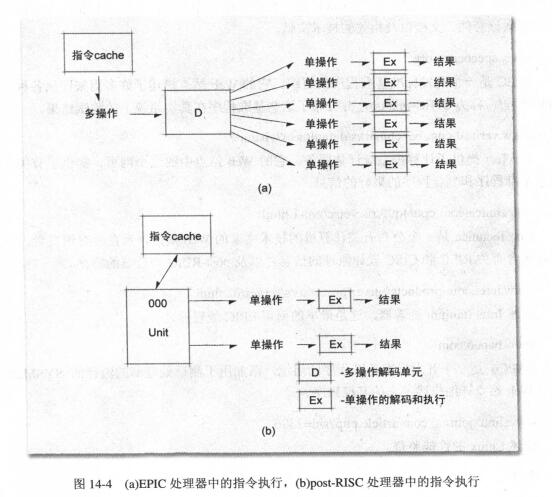

超標量和VLIW是開發指令級並行的兩種極端結構,前者完全依賴流水線硬體動態識別出可並行的指令,並將它們分發給相應的功能單元執行,後者則將指令級並行的開發工作全部交給編譯器完成,在編譯時靜態確定每條指令的流出時刻和執行延遲,僅依賴簡單的流水線硬體確保在指令實際執行延遲與編譯器假定的延遲不一致時(如訪問Cache不命中就會增加訪存操作的延遲),程式的執行結果依然正確。在這兩種結構中,單一的指令級並行開發機制使得它們都存在著嚴重的固有缺陷:超標量結構硬體複雜度太高,學術界和工業界一致認為,同時流出並執行8條指令將達到這種結構的極限;VLIW則面臨著嚴重的代碼兼容問題,而且VLIW編譯器的智慧型程度遠遠無法滿足人們的要求。顯式並行指令計算(Explicitly Parallel Instruction Computing,EPIC)技術正是為了解決這兩種結構的本質缺陷而提出的,它是在VLIW的基礎上融合了超標量結構的一些優點而設計得到的,以期用有限的硬體開銷為代價開發出更多的指令級並行。

結構

EPIC結構既不是RISC也不是CISC,它實質上是一種吸取了兩者長處的系統結構。基於EPIC技術的Itanium處理器的基本設計思想是:

(1)提供一種新的機制,利用編譯程式和處理器協同能力來提高指令並行度。傳統的RISC系統結構沒有能夠充分利用編譯程式所產生的許多有用信息(如關於程式運行路徑的猜測信息),也沒有充分利用現代編澤程式強大的對程式執行過程的調度能力。EPIC採用創新的技術充分利用編譯程式提供的信息和調度能力來提高指令並行度。

(2)簡化晶片邏輯結構,為提高主頻和性能開闢道路。EPIC信守工程設計上的一條基本原則.即“不是越複雜越好,而是越簡捷越好”。事實上,簡捷的構思比複雜的構思更困難。

(3)提供足夠的資源來實現EPIC,包括存儲編譯程式提供的信息以及提高並行計算效率所需的處理單元、高速快取和其他資源。包括4個整數單元,2個浮點單元,3個分支單元.3級高速快取(L1 Cache、L2 Cache、L3 Cache);5組供指令引用的暫存器:128個64位整數暫存器,128個82位浮點暫存器,64個預測暫存器,8個程式暫存器,1 28個專門的套用暫存器。

(4)充分利用豐富的暫存器資源,採用暫存器輪轉技術,讓指令按順序循環使用暫存器,使得處理器在非常繁忙的情況下也不會m現暫存器不足的情況;暫存器直接參與運算,指令的執行效率大大提高;暫存器組能為多個不同的進程保存暫存器狀態,使得進程間的切換十分迅速,非常適合於伺服器套用環境中的多進程並行運行。

特點

一般來說,EPIC結構必須符合以下兩個基本特點:

1、指令級並行主要由編譯器負責開發,處理器應為保證代碼正確執行提供必要的硬體支持,只有在這些硬體機制的輔助下,這些最佳化技術才能高效完成。

2、系統結構必須提供某種通信機制,使得流水線硬體能夠了解編譯器“安排”好的指令執行順序。但需要注意的是,EPIC並不僅僅是採用了多種高級編譯最佳化技術的VLIW結構,這只不過是它的一個特徵。EPIC的第二個特徵,有效的軟硬體通信機制,才是它與VLIW之間的本質區別。