在Verilog HDL的概念中阻塞賦值操作符用等號(即=)表示。在賦值時先計算等號右手部分的值,這時賦值語句不允許任何別的Verilog語句的干擾,直到現行的賦值完成時刻,才允許別的賦值語句的執行。

基本介紹

- 中文名:阻塞賦值

- 外文名:blocking assignment

- 操作符:等號(即=)

- 缺點:順序安排不好時會出現競爭

- 使用情況:描述組合邏輯的always塊

- 套用學科:機械工程、儀器科學、計算機科學

在Verilog HDL的概念中阻塞賦值操作符用等號(即=)表示。在賦值時先計算等號右手部分的值,這時賦值語句不允許任何別的Verilog語句的干擾,直到現行的賦值完成時刻,才允許別的賦值語句的執行。

在Verilog HDL的概念中阻塞賦值操作符用等號(即=)表示。在賦值時先計算等號右手部分的值,這時賦值語句不允許任何別的Verilog語句的干擾,直到現行的賦值完成時刻,才...

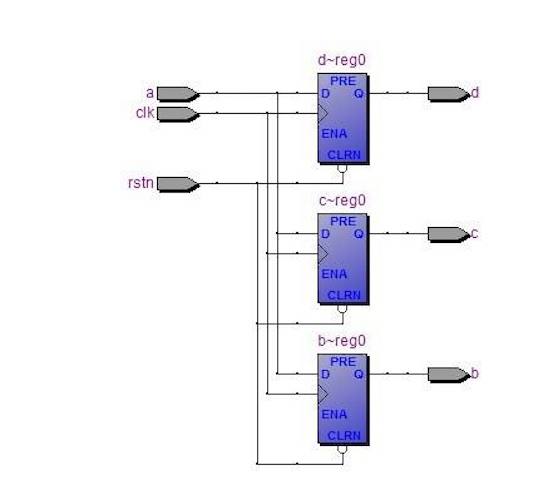

非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非...

Verilog HDL 中提供兩種過程賦值語句initial 和always 語句,用這兩種語句來實現行為的建模。這兩種語句之間的執行是並行的,若與語句塊(begin ...end)相結合,則...

連續賦值語句用於組合邏輯的建模。等式左邊是wire類型的變數。等式右邊可以是常量、由運算符如邏輯運算符、算術運算符參與的表達。在initial或always外的assign賦值語句...

大多數Verilog事件是由動態事件佇列調度的,這些事件包括阻塞賦值、連續賦值、$dis—play命令、實例和原語的輸入變化以及它們的輸出更新、非阻塞賦值語句RHS的計算等。...

在Verilog中,有兩種賦值運算,一種叫做阻塞賦值(blocking assignment),其運算符為=;另一種叫做非阻塞賦值(non-blocking assignment),其運算符為<=。在順序代碼塊中...

14.12 常見的對於非阻塞賦值的誤解小結思考題第15章 較複雜時序邏輯電路設計實踐概述小結思考題第16章 複雜時序邏輯電路設計實踐概述...

10.6.1 進程的設計10.6.2 阻塞賦值與非阻塞賦值10.6.3 套用要點10.7 片記憶體儲器的使用10.7.1 片記憶體儲器10.7.2 設計舉例10.8 如何消除毛刺...