在電路設計中,網表(netlist)是用於描述電路元件相互之間連線關係的,一般來說是一個遵循某種比較簡單的標記語法的文本檔案。門級(gate-level)指的是網表描述的電路綜合級別。顧名思義,門級網表中,描述的電路元件基本是門(gate)或與此同級別的元件。

基本介紹

- 中文名:門級網表

- 外文名:Gate-Level netlist

- 關係:同級別元件

- 用途:用於描述電路元件相互連線關係

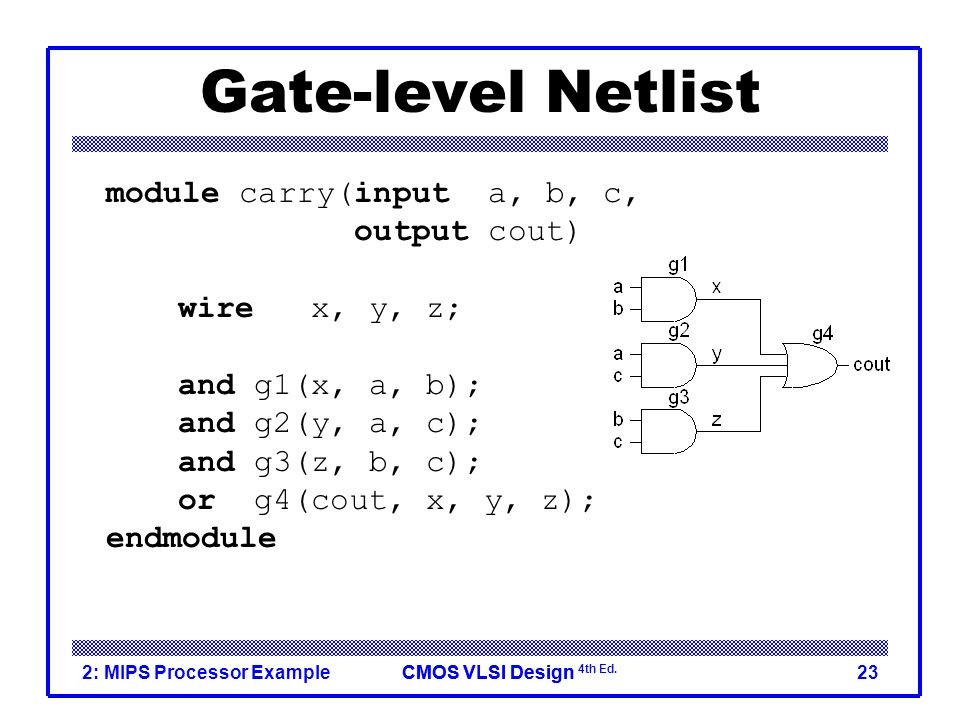

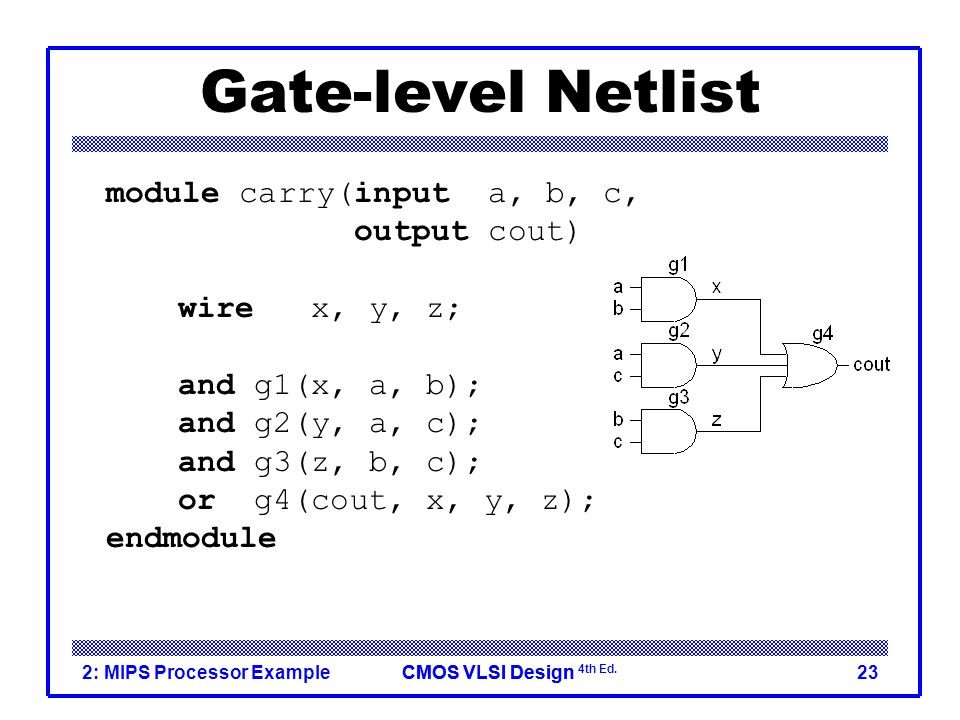

解析,門級網表示意圖,

解析

現代數字積體電路設計方法來自對傳統設計方法的總結和對計算機軟體技術的引入。在對電路性能的要求沒有達到工藝極限時,不需要對每個單元電路都進行特殊設計,可先設計出各種基本單元電路(cell),包括原理圖和版圖,形成一個標準單元庫,再利用庫中的cell實現複雜的邏輯關係。這種方法使得自動化設計成為可能。即使在全定製設計中,對電路功能的描述也是層次化的,而不是直接描述為電晶體網路。有了標準單元庫,一個電路就可以理解為由標準單元構成的網表,也就是說“描述級別”由電晶體級提升到了“門級”。

複雜的電路在“門級”仍然難以看出邏輯功能,需要更高級別的描述。一個複雜的數字電路系統可以理解為由若干個具有典型邏輯功能的模組和一個控制電路組成的,常見的模組包括暫存器、計數器、算術和邏輯運算單元和存儲器等。控制電路是一個有限狀態機,在時鐘的作用下,狀態機根據當前的狀態和輸入信號不斷地進行狀態轉換,同時產生輸出信號,控制各個邏輯模組工作。這種級別的描述稱為“架構級”,是最重要的設計級別。最高級別的描述是系統級,在這個級別,一般只定義系統的功能、外部接口和其中主要功能模組。最低級別的描述是版圖,版圖實際上就是一組幾何圖形,根據版圖可以生成光刻版。一個設計實際上總是要從系統級開始考慮,然後是架構級、門級、電晶體級,最後是版圖級。在傳統的設計流程中,可驗證的設計描述是從電晶體級開始的,用電晶體構成邏輯門,再由邏輯門構成功能模組,最後連線成系統。

門級網表示意圖

對於複雜的積體電路設計,電路功能需要通過多個級別的描述來完成。

數字電路設計分類:系統級、架構級、暫存器傳輸級(RTL)、門級和電晶體級等,所謂級別包括兩方面含義,一是設計者對電路的認識,二是允許使用的描述方法。

相關解析:

系統級設計的任務主要是定義電路的功能和外部特性,設計者只需要將電路為若干個抽象的功能模組,並將各個功能模組的邏輯功能定義清楚即可。

架構級設計要具體一些,在這個級別,電路要描述成相互連線的若干個典型邏輯部件和控制其數據傳輸的狀態機。典型邏輯部件包括計數器、暫存器、算術運算單元等,又稱為數據通道(Data path),狀態機則是一個設計中具有特殊性的部分,它控制數據通道的工作。以上兩種描述,描述方法沒有什麼限制,將問題說清楚即可。

暫存器傳輸級的描述是ASIC設計中最重要的描述,必須使用硬體描述語言完成。所謂暫存器傳輸級描述是基於這樣一種認識,即任何數字電路,無論功能如何,都是由暫存器和暫存器之間的組合邏輯電路實現的,暫存器用來保存數據,組合電路用於傳輸數據。RTL代碼必須保證可綜合性,只能使用硬體描述語言中的部分描述語句。從RTL代碼中應可隱約看出電路結構,又不要寫得過於具體。細化到邏輯門和觸發器的代碼並不好,因為從RTL描述到cell的轉換是邏輯綜合工具的任務,人為寫到cell一級不僅降低了代碼的可讀性,也不利於最佳化。

在ASIC設計中,門級和電晶體級電路是由EDA工具生成的,設計者的任務是給出功能正確的RTL級代碼。