鎖相頻率合成器(phase locked frequency synthe-sizer)是用鎖相環實現的頻率合成器。頻率合成器是將一個高穩定度和高精度的標準頻率,經過對頻率的加、減、乘、除四則運算,產生同樣穩定度和精確度的大量離散、按一定頻率間隔輸出頻率的信號源。

基本介紹

- 中文名:鎖相頻率合成器

- 外文名:phase locked frequency synthe-sizer

單環頻率合成器

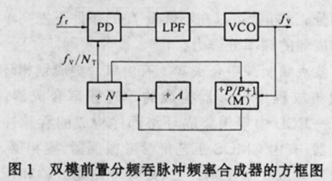

採用變模分頻器

圖1

圖1多環頻率合成器

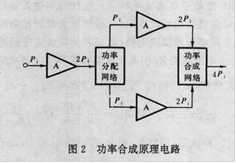

圖2

圖2鎖相頻率合成器(phase locked frequency synthe-sizer)是用鎖相環實現的頻率合成器。頻率合成器是將一個高穩定度和高精度的標準頻率,經過對頻率的加、減、乘、除四則運算,產生同樣穩定度和精確度的大量離散、按一定頻率間隔輸出頻率的信號源。

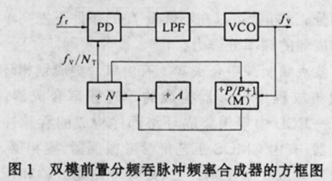

圖1

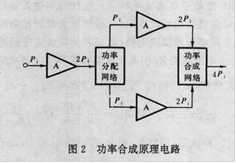

圖1 圖2

圖2鎖相頻率合成器(phase locked frequency synthe-sizer)是用鎖相環實現的頻率合成器。頻率合成器是將一個高穩定度和高精度的標準頻率,經過對頻率的加、減、乘、除...

頻率合成的方法主要有三種:直接頻率合成(DFS),鎖相環頻率合成(PLL)以及直接數字頻率合成(DDS)。這三種頻率合成方法各有特點,傳統的PLL在低相位噪聲和低雜散方面有...

《鎖相環與頻率合成器電路設計》是2008年10月西安電子科技大學出版社出版的圖書,作者是黃智偉。本書主要對鎖相環與頻率合成器電路的相關知識做了介紹。...

頻率合成技術起源於20世紀30年代,至今已有70多年的歷史。頻率合成器的實現方法有3種:直接模擬頻率合成、間接頻率合成和直接數字頻率合成。根據出現的時間順序,可將其...

頻率合成技術的發展時間不長。早期是用多晶體直接合成。20世紀50年代出現了間接頻率合成技術,但頻段只局限於短波範圍。60年代中期,出現了數字鎖相式頻率合成器; 60...

《鎖相與頻率合成》是2011年出版的圖書,作者是張建斌。...... 鎖相與頻率合成》為高等學校“鎖相與頻率合成”課程的教材,講述鎖相環與頻率合成器的理論、組成、...

《鎖相與頻率合成器電路設計》是由西安電子科技大學出版社出版的圖書。...... 《鎖相與頻率合成器電路設計》是由西安電子科技大學出版社出版的圖書。...

本書介紹了鎖相環與頻率合成器電路的分析方法、工作原理等相關知識,以及採用鎖相環與頻率合成器積體電路構成的鎖相環(PLL)、直接數字頻率合成器(DDS)和時鐘發生器...

頻率合成技術起源於20世紀30年代,至今已有70多年的歷史。頻率合成器的實現方法有3種:直接模擬頻率合成、間接頻率合成和直接數字頻率合成。根據出現的時間順序,可將其...

PLL(Phase Locked Loop): 為鎖相迴路或鎖相環,用來統一整合時鐘信號,使高頻器件正常工作,如記憶體的存取資料等。PLL用於振盪器中的反饋技術。 許多電子設備要正常...

鎖相環 (phase locked loop)是一種利用相位同步產生的電壓,去調諧壓控振盪器以產生目標頻率的負反饋控制系統。學過自動控制原理的人都知道,這是一種典型的反饋...

第四節 通用單片集成鎖相環一、高頻單片集成鎖相環二、超高頻單片集成鎖相環三、低頻單片集成鎖相環第五節 集成頻率合成器一、中規模集成頻率合成器...

小數分頻鎖相環(Fractional-N Phase Locked Loop)頻率合成作為一種新技術,通過使分頻比變為小數,可獲得任意小的頻率間隔,實現高頻率分辨力的頻率合成。它相對於...

鎖相環與頻率合成器設計是2008西安電子科技大學出版社出版的圖書,作者是黃智偉...... 本書介紹了鎖相環與頻率合成器電路的分析方法、工作原理等相關知識,以及採用鎖...

頻率合成器是現代電子系統的心臟,本書從頻率合成的基本概念人手,對頻率穩定度概念和以鎖相為主的頻率合成方式等相關知識進行了深入講解。主要內容包括頻率合成的基本...

4.1 單環分頻鎖相頻率合成器4.1.1 單環分頻鎖相頻率合成器工作原理4.1.2 單環分頻鎖相頻率合成器的性能4.1.3 單環分頻鎖相頻率合成器的相位噪聲...

頻率合成器是現代電子系統的心臟,本書從頻率合成基本概念入手,對頻率穩定相關概念和以鎖相為主的頻率合成方式等相關知識進行了深入講解。主要內容包括頻率合成的基本...

頻率合成技術就是把一個或者多個高穩定度、高準確度的參考頻率,經過各種信號處理技術,生成具有同等穩定度和準確度的各種離散頻率。參考頻率可由晶體振盪器產生,合成...

第9章 振盪器第10章 檢相器第11章 環路濾波器第12章 電荷泵鎖相環第13章 數字(採樣)鎖相環第14章 異常鎖定第15章 PLL頻率合成器...

從選材來看,從鎖相環負反饋原理出發,先介紹鎖相環及頻率合成器在通信電路中的套用和性能,然後由鎖相環基本結構、主要模組電路設計細節逐漸深入到基於差分積分調製器...

間接頻率合成又稱之為鎖相頻率合成。採用了鎖相環技術,對頻率進行加、減、乘、除,產生所需的頻率。由於鎖相環相當於一個窄帶跟蹤濾波器,所以鎖相頻率合成的方法...