基本介紹

- 中文名:超長指令字

- 外文名:Very Long Instruction Word

- 簡稱:VLIW

- 提出時間:1983年

超長指令字是微處理器設計領域中的一種越來越流行的技術。超長指令字處理器採用多個獨立的功能部件,但它並不是將多條指令流出到各個功能單元,而是將多條指令的...

組合在一起,構成一條具有多個操作段的超長指令,由這條超長指令控制VLlW機器中多個互相獨立工作的功能部件,每個操作段控制一個功能部件,相當於同時執行多條指令。...

VLIW:(Very Long Instruction Word,超長指令字)一種非常長的指令組合,它把許多條指令連在一起,增加了運算的速度。 超長指令字(VLIW)是指令級並行,超執行緒(Hyper-...

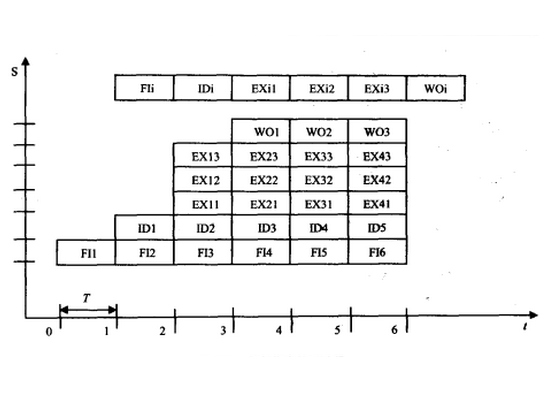

超長指令字處理機: 是指在一個基本時鐘周期內能夠分時發射多條指令的處理機,一般流水線的級數多達8條及以上。 超流水線處理機採用多相的高頻時鐘。一台度為m的...

EPIC允許處理器根據編譯器的調度並行執行指令而不用增加硬體複雜性,該架構由超長指令字架構發展而來,並做了大量改進。中文名 顯式並行指令運算 外文名 Explicitly ...

Computing,CISC);精簡指令集運算(Reduced Instruction Set Computing,RISC) ;顯式並行指令集運算(Explicitly Parallel Instruction Computing,EPIC);超長指令字指令集運算...

超長指令字(VLIW:VeryLongInstructionWord)是由美國Yale大學教授Fisher提出的。它有點類似於超級標量,是一條指令來實現多個操作的並行執行,之所以放到一條指令是為了...

全美達(Transmeta)NASDAQ:TMTA是一家設計超長指令字(VLIW)程式碼轉譯微處理器的美國有限公司,集中於開發減低電子設備功秏的運算技術,於1995年由Bob Cmelik、Dave ...

典型的超長指令字VL1W 機器指令字長度有數百位。在VLlW 處理機中,多個功能部件是並發工作的,所有的功能部件共享使用公用大型暫存器堆,由功能部件同時執行的各種操作...

綜合來說,這兩個限制驅使研究轉向其他的效能增進架構,例如超長指令字(VLIW)、顯式並行指令計算(EPIC)、同步多執行緒(SMT)和多核心處理器。...

3.7.2 超長指令字(VLIW)處理器3.7.3 超標量與超長指令字(VLIW)的區別3.8 DSP的傳輸速度3.8.1 DMA控制技術3.8.2 DMA控制器與傳輸控制塊...

而惠普的研究員在研究一個稱之為顯式並發指令運算(EPIC)的新架構,該架構允許處理器在一個周期內運行多條指令。EPIC是一種超長指令字(VLIW)架構,每個這種指令即...

採用多個功能單元並行實現一條指令中的不同操作屬於指令內部並行,超長指令字( VLIW) 計算機是實現指令內部並行的典型例子。同一時間執行兩條以上指令稱為指令間並行...

單一指令周期容納多部並行操作。在RISC微處理器發展過程中。曾產生了超長指令字(VLIW)微處理器,它使用非常長的指令組合,把許多條指令連在一起,以能並行執行。...

與超長指令字( VLIW , Very Long Instruction Word) 結構的數位訊號處理器相似 ,超標量結構的處理器每個時鐘周期也並行發射和執行多條指令 . 區別在於 ,VLIW的...

一些新的DSP採用超長指令字(VLIW)架構,在這種架構中,單個周期時間內可以實現多條指令,而每個指令所實現的任務比傳統DSP少,因此相對VLIW和通用DSP器件而言,比較MIPS...

TMS320DM642採用第二代高性能、先進的超長指令字veloci T1.2結構的DSP核及增強的並行機制,當工作在720M赫茲的時鐘頻率下,其處理性能最高可達5760MI/s,使得該款...

2.4.1 超長指令字處理器2.4.2 超標量處理器2.4.3 SIMD與向量處理器2.4.4 執行緒級並行2.4.5 處理器資源利用率2.5 性能可變處理器體系結構...

第1章介紹計算機系統結構的基本概念、指令設計與定址、I/O系統設計和存儲體系設計等基礎內容;第2章討論流水處理技術以及超標量、超流水和超長指令字處理機;第3章...

超標量(Superscalar)結構和超長指令字(VLIW)結構在高性能微處理器中被廣泛採用。但是它們的發展都遇到了難以逾越的障礙。Superscalar結構使用多個功能部件同時執行多條...

採用指令級並行技術標量處理機三種指令級並行處理機 流水線(pipelining )處理機超標量(Superscalar)處理機超長指令字(VLIW:Very Long Instruction Word)處理機...

全美達(Transmeta)NASDAQ:TMTA是一家設計超長指令字(VLIW)程式碼轉譯微處理器的美國有限公司,集中於開發減低電子設備功秏的運算技術,於1995年由Bob Cmelik、Dave ...

另外一種衍生類型是超長指令字,處理器接受許多經過編碼的指令並通過檢索提取出一個指令字並執行。微碼機器語言 機器語言是由聲明和指令所組成的。在處理結構上,一個...

5.3 指令級高度並行的超級處理機 1895.3.1 超標量處理機 1905.3.2 超長指令字處理機 1915.3.3 超流水線處理機 1925.3.4 超標量超流水線處理機 193...