專利背景

隨著套用技術的發展,人們對

處理器的處理速度和功耗的要求越來越高,因此,對其內置

存儲器的功耗和速率的要求也越來越高。尤其是在移動通信領域,隨著人們對傳輸數據頻寬的要求的提高,對於核心晶片中所採用的處理器的實時處理各種通信協定的能力要求也是提高,其所處理的中間數據量也大幅的提升,而同時系統對晶片功耗的要求卻卡得更嚴。這對晶片中所用的數據存儲器的要求不僅是提供高速大容量數據交換,同時對低功耗也更迫切。在一個典型的處理器設計中,內置數據存儲器已經是晶片中消耗最大的功能塊。

2010年4月前隨著但導體工藝的發展,一個處理器的運算單元的速度提高的很快,而存儲器的速度往往落後運算單元的速度的提高,因此存儲器的速度就成為提高整個處理器運算速度的瓶頸。為了提高存儲器的速度就必須增大存儲單元器件的尺寸,而這又會增加功耗。因此,如何能提高存儲器的讀寫速度而又能降低功耗已經成了設計高速低耗處理器的重要課題。

發明內容

專利目的

《處理器及其內置存儲器》提供一種處理器及其內置存儲器,以合理利用讀寫速率比較低的低功耗存儲塊,進而降低處理器的功耗並同時能提高處理器的整體運算速度。

技術方案

《處理器及其內置存儲器》提供的處理器,設有內置存儲器,該存儲器包括:至少一個由該處理器奇時鐘驅動的奇時鐘存儲塊;以及至少一個由該處理器偶時鐘驅動的偶時鐘存儲塊;其中該奇時鐘與該偶時鐘的相位差為180度,且該奇時鐘與該偶時鐘的頻率是處理器時鐘頻率的1/2,n為大於或等於1的整數。通常,該處理器與該存儲器之間還連線有邏輯單元。

為達上述目的,該發明還提供一種存儲器,該存儲器內置於處理器,包括:至少一個由該處理器奇時鐘驅動的奇時鐘存儲塊;以及至少一個由該處理器偶時鐘驅動的偶時鐘存儲塊;其中該奇時鐘與該偶時鐘的相位差為180度,且該奇時鐘與該偶時鐘的頻率是處理器時鐘頻率的1/2,n為大於或等於1的整數。

該發明采奇偶時鐘的內置數據存儲器結構,該結構能使內置存儲器運行在通處理器運算單元一半的時鐘頻率下而又基本不影響處理單元對存儲器進行讀寫操作的速率。由於每個存儲塊的運行速率是處理時鐘頻率的一半,因此對每個存儲塊的速度要求就降低了一半,因而可以選用讀寫速率比較低的低功耗存儲塊。

其中,為滿足存儲器具有超長位元組的存儲能力,該奇時鐘存儲塊的數量為兩個或兩個以上;且各個奇時鐘存儲塊之間並行連線。同理,為滿足存儲器具有超長位元組的存儲能力,該偶時鐘存儲塊的數量為兩個或兩個以上;且各個偶時鐘存儲塊之間並行連線。由此,該存儲器能按處理器的指令要求進行多種不同位元組的數據讀寫。

改善效果

基於上述存儲塊的並行結構,處理器能根據位元組地址來選擇存儲塊的讀寫並對沒有被選中的存儲塊的時鐘進行停止操作。《處理器及其內置存儲器》中,該處理器可以對當前讀寫的奇時鐘存儲塊輸送奇時鐘,並對當前未選中的奇時鐘存儲塊進行時鐘停止操作控制;也可以對當前讀寫的偶時鐘存儲塊輸送偶時鐘,並對當前未選中的偶時鐘存儲塊進行時鐘停止操作控制。從而有效降低了整個內置存儲器的功耗。

附圖說明

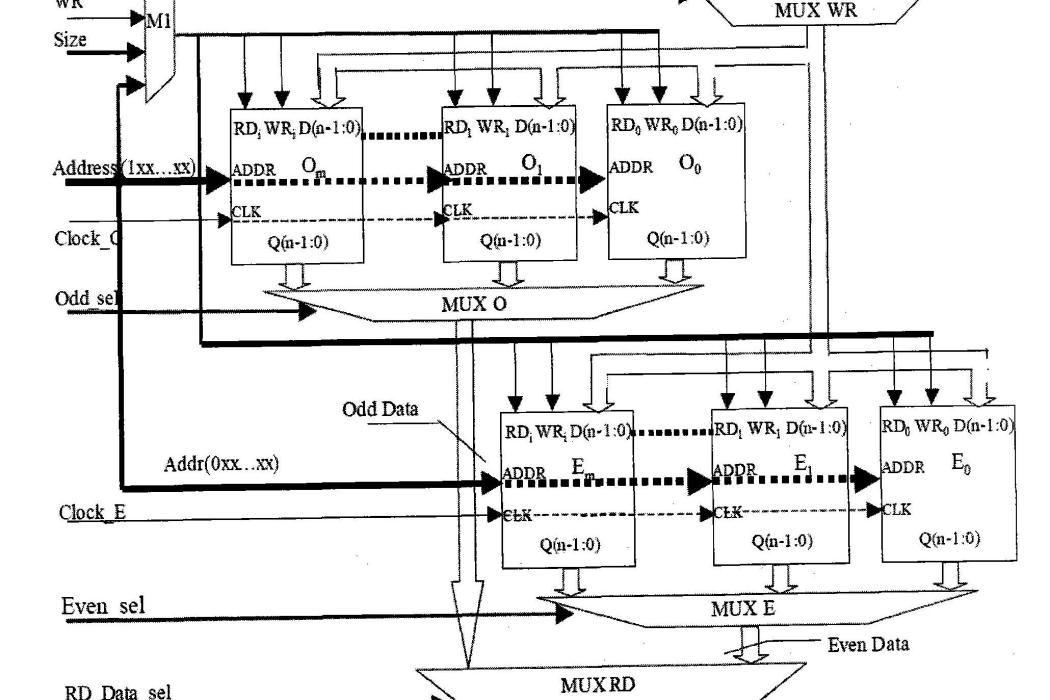

圖1為《處理器及其內置存儲器》提供存儲器電路的邏框圖。

圖2為該發明提供時鐘產生電路和波形。

圖3為該發明提供的奇數/偶數存儲塊的地址分配示意圖。

權利要求

1.一種處理器,設有內置存儲器,其特徵在於,該存儲器包括:一個及一個以上由該處理器奇時鐘驅動的奇時鐘存儲塊,且各個奇時鐘存儲塊之間並行連線;以及一個及一個以上由該處理器偶時鐘驅動的偶時鐘存儲塊,且各個偶時鐘存儲塊之間並行連線;其中所述奇時鐘與所述偶時鐘的相位差為180度,且該奇時鐘與該偶時鐘的頻率是處理器時鐘頻率的l/2,n為大於或等於1的整數;所述處理器對當前讀寫的奇時鐘存儲塊輸送奇時鐘,並對當前未選中的奇時鐘存儲塊進行時鐘停止操作控制;所述處理器對當前讀寫的偶時鐘存儲塊輸送偶時鐘,並對當前未選中的偶時鐘存儲塊進行時鐘停止操作控制。

2.根據權利要求1所述的處理器,其特徵在於,所述處理器與所述存儲器之間還連線有邏輯單元。

3.一種存儲器,該存儲器內置於處理器,其特徵在於,包括:一個及一個以上由該處理器奇時鐘驅動的奇時鐘存儲塊,且各個奇時鐘存儲塊之間並行連線;以及一個及一個以上由該處理器偶時鐘驅動的偶時鐘存儲塊,且各個偶時鐘存儲塊之間並行連線;其中所述奇時鐘與所述偶時鐘的相位差為180度,且該奇時鐘與該偶時鐘的頻率是處理器時鐘頻率的l/2,n為大於或等於1的整數;所述處理器對當前讀寫的奇時鐘存儲塊輸送奇時鐘,並對當前未選中的奇時鐘存儲塊進行時鐘停止操作控制;所述處理器對當前讀寫的偶時鐘存儲塊輸送偶時鐘,並對當前未選中的偶時鐘存儲塊進行時鐘停止操作控制。

實施方式

《處理器及其內置存儲器》提供一種處理器及其內置存儲器,其中,該存儲器包括:至少一個由該處理器奇時鐘驅動的奇時鐘存儲塊;以及至少一個由該處理器偶時鐘驅動的偶時鐘存儲塊;其中該奇時鐘與該偶時鐘的相位差為180度。

圖1給出了採用奇偶時鐘驅動的數據存儲器電路的邏輯框圖。如圖所示,該電路共有2xm個存儲器塊(m=2,4,8,......)。每個存儲器塊的數據字長Q/D是n位(n=16,32,64,......)。存儲塊E0,E1,......,Em由時鐘ClockE驅動。存儲塊O0,O1,......,Om由時鐘ClockO驅動。如圖2所示,時鐘ClockE和時鐘ClockO的頻率是處理器時鐘Clock的一半,兩者的相位差為180度。

該實施例中,該內置存儲器單元可進行多個不同字長的數據的讀寫操作。字長位數可從最小8位到最大m*n位。字長的選擇由處理器的存儲指令來控制。其中,邏輯單元MUX,MUXE和MUXRD是分別用於選擇讀出的數據並把它們送往相應的運算單元。它們分別有控制信號Odd_sel,Even_sel和RD_Data_sel來控制的。這些控制信號是有處理器的讀數據指令中的位元組長度,地址和哪個運算單元等信息產生的。

如圖1所示,WR_Data_sel是用於選擇數據來源和控制寫數據的位元組長度,它是根據處理器寫數據指令中的位元組長度,地址和哪個運算單元發出的等信息產生的。邏輯門M1是用於產生每一個存儲塊的讀寫控制信號WRi/RDi(i=1,2,3......)。這些讀寫控制信號的產生由處理器發出的讀寫信號加上數據的大小及存儲塊的地址值來決定。該實施例中,各個奇時鐘存儲塊並行連線組成的群組和各個偶時鐘存儲塊並行連線組成的群組的地址則由該存儲器的地址線最高位來決定;如圖1所示,Amax=0,則選中的是偶時鐘存儲塊群組,Amax=1,則選中的是奇時鐘存儲塊群組;其中,各群組中單個存儲塊地址線的位數則是由每個存儲塊的位元組長度(n/8)和奇/偶時鐘存儲塊的數量m來決定的,例如,n=64=8x8=2位元組,m=8=2,若以最小地址線A0代表一個位元組地址,則存儲塊地址線的位數就是A5,A4,A3,如圖3所示的111、110、......000。該實施例中,由於各個奇時鐘存儲塊並行連線組成的群組和各個偶時鐘存儲塊並行連線組成的群組的地址則由地址線最高位來決定,如此則一條讀寫指令可以一次最大讀寫字數達到m*n位數的字。

當圖1中的存儲器的存儲量是512K位元組時,如圖3所示,其中偶時鐘存儲塊群組(Amax=0)的尺寸是256K位元組,其地址範圍是從0,0000到3,FFFF;而奇時鐘存儲塊群組(Amax=1)的地址是從4,0000到7,FFFF。如此,每次偶或奇存儲器群組的最大讀寫位元組是64,位數則是512位。這樣就極大的增加存儲器字數長度的讀寫的可程式性。

該實施例所提供的存儲器及其存儲電路可以套用於處理器中的L1存儲器,也可用於L2存儲器,且特別適合於多執行緒結構的處理器和多個並行處理結構的處理器。

基於上述各群組中存儲塊的並行構造,處理器能根據位元組地址來選擇存儲塊的讀寫並對沒有被選中的存儲塊的時鐘進行停止操作。《處理器及其內置存儲器》中,所述處理器可以對當前讀寫的奇時鐘存儲塊輸送奇時鐘,並對當前未選中的奇時鐘存儲塊進行時鐘停止操作控制;也可以對當前讀寫的偶時鐘存儲塊輸送偶時鐘,並對當前未選中的偶時鐘存儲塊進行時鐘停止操作控制。從而有效降低了整個內置存儲器的功耗。

榮譽表彰

2013年,《處理器及其內置存儲器》獲得第八屆江蘇省專利項目獎優秀獎。