簡介 精簡指令集,是計算機中央處理器的一種設計模式,也被稱為RISC(Reduced Instruction Set Computing的縮寫)。這種設計思路對指令數目和

定址方式 都做了精簡,使其實現更容易,指令

並行執行 程度更好,編譯器的效率更高。常用的精簡指令集微處理器包括DECAlpha、ARC、ARM、AVR、MIPS、PA-RISC、PowerArchitecture(包括PowerPC)和SPARC等。這種設計思路最早的產生緣於有人發現,儘管傳統處理器設計了許多特性讓代碼編寫更加便捷,但這些複雜特性需要幾個

指令周期 才能實現,並且常常不被運行程式所採用。此外,處理器和主記憶體之間運行速度的差別也變得越來越大。在這些因素促使下,出現了一系列新技術,使處理器的指令得以流水執行,同時降低處理器訪問記憶體的次數。早期,這種指令集的特點是指令數目少,每條指令都採用標準

字長 、執行時間短、

中央處理器 的實現細節對於機器級程式是可見的。

發展背景 在早期的計算機業中,

編譯器 技術尚未出現。程式是以

機器語言 或彙編語言完成的。為了便於編寫程式,計算機架構師造出越來越複雜的指令,可以高階程式語言直接陳述高階功能。當時的看法是硬體比編譯器更易設計,所以複雜的東西就加進硬體了。

加速複雜化的其它因素是缺乏大記憶體。記憶體小的環境中,具有極高訊息密度的程式較有利。當記憶體中的每一位元組如此珍貴,例如儲存某個完整系統只需幾千位元組,它使產業移向高度編碼的指令、長度不等的指令、執行多個操作的指令,和執行數據傳輸與計算的指令。當時指令

封包 問題遠比易解的指令重要。

那時使用磁性技術,記憶體不僅小,而且很慢。這是維持極高訊息密度的其它原因。借著具有極高訊息密度封包,當必須存取慢速資源時可以降低頻率。

CPU只有少數快取器的兩個原因︰

CPU內部

快取 器遠貴於外部記憶體。以當時的積體電路技術水準,大快取器集對晶片或電路板區域只是多餘的浪費。

具有大數量的快取器將需要大數量的指令位(使用珍貴的

RAM )以做為快取器指定器。

基於上述原因,CPU設計師試著令指令儘可能做更多的工作。這導致一個指令將做全部的工作︰讀入兩個數字,相加,並且直接在記憶體儲存計算結果。其它版本將從記憶體讀取兩個數字,但計算結果儲存在快取器。另一個版本將從記憶體和快取器各讀一個數字,並再次存入記憶體。以此類推。這種處理器設計原理最終成為

複雜指令集 (CISC)。

當時的目標是給所有的指令提供所有的定址模式,此稱為「正交性」。這在 CPU 上導致了一些複雜性,但就理論上每個可能的命令都可以單獨的調試(調用,be tuned),這樣使得程式設計師能夠比用簡單的命令來得更快速。

這類的設計最終可以由光譜的兩端來表達, 6502 在光譜的一端,而 VAX 在光譜的另一端。單價25美元的 1MHz 6502 晶片只有單一的通用

快取 器, 但它的極精簡的單周期記憶體界面(single-cycle memory interface)讓一個位的操作效能和更高頻率設計幾乎相同,例如 4MHz Zilog Z80 在使用相同慢速的記憶晶片下(大約近似 300ns)。

發展分歧 在

計算機指令系統 的最佳化發展過程中,出現過兩個截然不同的最佳化方向:CISC技術和RISC技術。CISC是指

複雜指令系統計算機 (Complex Instruction Set Computer);RISC是指精簡指令系統計算機(Reduced Instruction Set Computer)。這裡的計算機指令系統指的是計算機的最低層的

機器指令 ,也就是CPU能夠直接識別的指令。隨著計算機系統的複雜,要求計算機指令系統的構造能使計算機的整體性能更快更穩定。最初,人們採用的最佳化方法是通過設定一些功能複雜的指令,把一些原來由軟體實現的、常用的功能改用硬體的

指令系統 實現,以此來提高計算機的執行速度,這種計算機系統就被稱為

複雜指令系統計算機 ,即Complex Instruction Set Computer,簡稱CISC。另一種最佳化方法是在20世紀80年代才發展起來的,其基本思想是儘量簡化

計算機指令 功能,只保留那些功能簡單、能在一個節拍內執行完成的指令,而把較複雜的功能用一段子程式來實現,這種計算機系統就被稱為精簡

指令系統 計算機.即Reduced Instruction Set Computer,簡稱RISC。RISC技術的精華就是通過簡化計算機指令功能,使指令的平均執行周期減少,從而提高計算機的工作主頻,同時大量使用

通用暫存器 來提高子程式執行的速度

精簡指令集 提出原由 IBM公司設在紐約Yorktown的JhomasI.Wason研究中心於1975年組織力量研究

指令系統 的合理性問題.因為當時已感到,日趨龐雜的指令系統不但不易實現.而且還可能降低系統性能.1979年以帕特遜教授為首的一批科學家也開始在美國加州大學伯克萊分校開展這一研究.結果表明,CISC存在許多缺點.首先.在這種計算機中.各種指令的使用率相差懸殊:一個典型程式的運算過程所使用的80%指令.只占一個處理器指令系統的20%.事實上最頻繁使用的指令是取、存和加這些最簡單的指令.這樣-來,長期致力於複雜指令系統的設計,實際上是在設計一種難得在實踐中用得上的指令系統的處理器.同時.複雜的指令系統必然帶來結構的複雜性.這不但增加了設計的時間與成本還容易造成設計失誤.此外.儘管VLSI技術現在已達到很高的水平,但也很難把CISC的全部硬體做在一個晶片上,這也妨礙

單片計算機 的發展.在CISC中,許多複雜指令需要極複雜的操作,這類指令多數是某種高級語言的直接翻版,因而通用性差.由於採用二級的微碼執行方式,它也降低那些被頻繁調用的簡單指令系統的運行速度.因而.針對CISC的這些弊病.帕特遜等人提出了精簡指令的構想即指令系統應當只包含那些使用頻率很高的少量指令.並提供一些必要的指令以支持作業系統和高級語言.按照這個原則發展而成的計算機被稱為

精簡指令集計算機 (ReducedInstructionSetComputer-RISC)結構.簡稱RISC.

優勢 RISC和CISC是設計製造

微處理器 的兩種典型技術,雖然它們都是試圖在

體系結構 、操作運行、軟體硬體、

編譯時間 和運行時間等諸多因素中做出某種平衡,以求達到高效的目的,但採用的方法不同,因此,在很多方面差異很大,它們主要有:

精簡指令集 (1)

指令系統 :RISC設計者把主要精力放在那些經常使用的指令上,儘量使它們具有簡單高效。對不常用的功能,常通過組合指令來完成。因此,在RISC機器上實現特殊功能時,效率可能較低。但可以利用流水技術和

超標量技術 加以改進和彌補。而CISC計算機的指令系統比較豐富,有專用指令來完成特定的功能。因此,處理特殊任務效率較高。

(2)

存儲器 操作:RISC對存儲器操作有限制,使控制簡單化;而CISC機器的存儲器操作指令多,操作直接。

(3)程式:CISC

彙編語言程式 一般需要較大的記憶體空間,實現特殊功能時程式複雜,不易設計;而RISC彙編語言程式編程相對簡單,科學計算及複雜操作的程式設計相對容易,效率較高。

(4)中斷:RISC機器在一條指令執行的適當地方可以回響中斷,但是相比CISC指令執行的時間短,所以中斷回響及時;而CISC機器是在一條指令執行結束後回響中斷。

精簡指令集 (5)CPU:RISC CPU包含有較少的單元電路,因而面積小、功耗低;而CISCCPU包含有豐富的電路單元,因而功能強、面積大、功耗大。

(6)設計周期:RISC

微處理器 結構簡單,布局緊湊,設計周期短,且易於採用最新技術;CISC微處理器結構複雜,設計周期長。

(7)用戶使用:RISC微處理器結構簡單,指令規整,性能容易把握,易學易用;CISC微處理器結構複雜,功能強大,實現特殊功能容易。

(8)套用範圍:由於CISC

指令系統 的確定與特定的套用領域有關,故CISC機器更適合於專用機;而RISC機器則更適合於通用機。

特徵 統一指令編碼(例如,所有指令中的op-code永遠位於同樣的位位置、等長指令),可快速解譯︰

32位精簡指令集架構 泛用的快取器,所有快取器可用於所有內容,以及編譯器設計的單純化(不過快取器中區分了整數和浮點數);

單純的定址模式(複雜定址模式以簡單計算指令序列取代);

硬體中支持少數數據型別(例如,一些CISC計算機中存有處理位元組字元串的指令。這在RISC計算機中不太可能出現)。

RISC設計上同時也有哈佛記憶體模組特色,凡

指令流 和數據流在概念上分開;這意味著更改代碼存在的記憶體地址對處理器執行過的指令沒有影響(因為CPU有著獨立的指令和

數據快取 ),至少在特殊的同步指令發出前。在另一面,這允許

指令快取 和數據快取同時被訪問,通常能改進運行效率。

許多早期的RISC設計同樣共享著不好的副作用——轉移延時槽,轉移延時槽是指一個跳轉或轉移指令之後的指令空間。無論轉移是否發生,空間中的指令將被執行(或者說是轉移效果被延遲)。這些指令讓CPU的算術和

邏輯單元 (ALU)繁忙比通常執行轉移所需更多的時間。現在轉移延時槽被認為是實現特定RISC設計的副作用,現代的RISC設計通常避免了這個問題(如PowerPC,最近的SPARC版本,MIPS)。

結構特點 RISC是簡化

指令集計算機 的簡略縮寫,其風格是強調計算機結構的簡單性和高效性。RISC設計是從足夠的不可缺少的指令集開始的。它的速度比那些具有傳統複雜指令組計算機結構的機器快得多,而且RISC機由於其較簡潔的設計,較易使用,故具有更短的研製開發周期。RISC結構一般具有如下的一些特點:

精簡指令集 ①單周期的執行:它統一用單周期指令。從根本上克服了CISC

指令周期 數有長有短,造成運行中偶發性不確定,致使運行失常的問題。

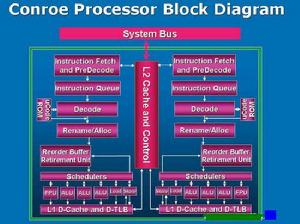

②採用高效的流水線操作:使指令在流水線中並行地操作,從而提高處理數據和指令的速度。

③無

微代碼 的硬連線控制:微代碼的使用會增加複雜性和每條指令的執行周期。

④

指令格式 的規格化和簡單化:為與

流水線結構 相適應且提高流水線的效率,指令的格式必須趨於簡單和固定的規式。比如指令採用16位或32位的固定的長度,並且指令中的

操作碼 欄位、運算元欄位都儘可能具有統一的格式。此外,儘量減少

定址方式 ,從而使硬體邏輯部件簡化且縮短

解碼 時間,同時也提高了機器執行效率和可靠性。

⑤採用面向

暫存器 堆的指令:RISC結構採用大量的暫存器——暫存器操作指令,使

指令系統 更為精簡。控制部件更為簡化,指令執行速度大大提高。由於VLSI技術的迅速發展,使得在一個晶片上做大量的暫存器成為可能。這也促成了RISC結構的實現。

⑥採用裝入/存儲指令結構:在CISC結構中。大量設定

存儲器 ——存儲器操作指令,頻繁地訪問記憶體,將會使執行速度降低。RISC結構的指令系統中,只有裝入/存儲指令可以訪問記憶體,而其它指令均在暫存器之間對數據進行處理。用裝入指令從記憶體中將數據取出,送到暫存器;在暫存器之間對數據進行快速處理,並將它暫存在那裡,以便再有需要時。不必再次訪問記憶體。在適當的時候,使用一條存儲指令再將這個數據送回記憶體。採用這種方法可以提高指令執行的速度。

⑦注重編譯的最佳化,力求有效地支撐高級語言程式。

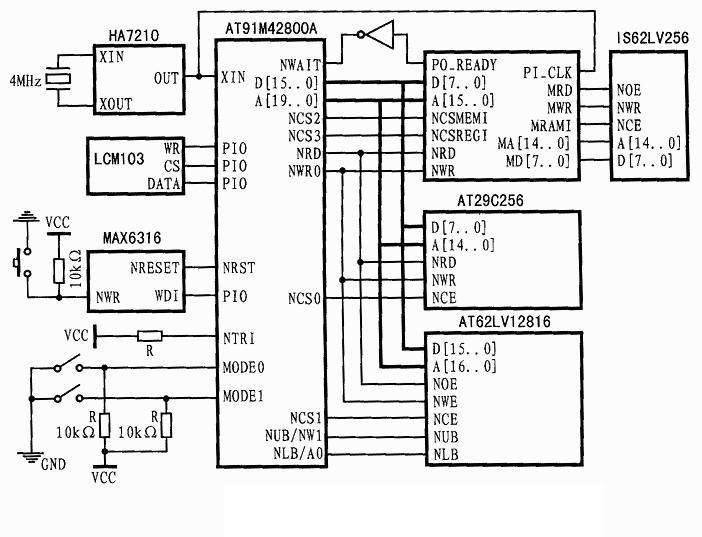

通常使用的

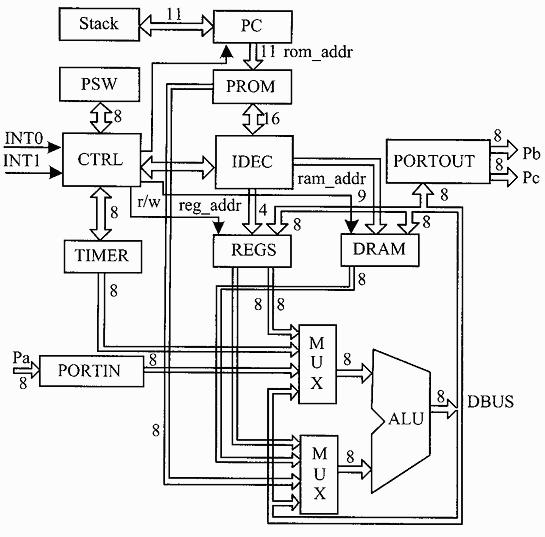

單片機 中,MCS一51系列的單片機屬於CISC的體系結構;AVR系列的單片機則屬於RISC的體系結構。

發展前景 鑒於RISC的設計特點以及其無可比擬的優點,RISC體系結構處理器的發展方向:

一是增加處理器的

並行性 ;

擴展指令集 二是擴展支持可伸縮並行計算機系統的功能;

三是提高工藝水平。最終RISC與DSP在嵌入式套用中完美融合,密不可分。

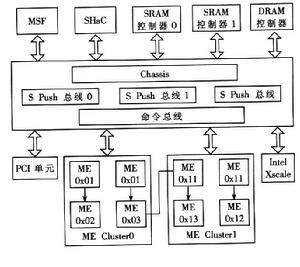

RISC

微處理器 不僅精簡了

指令系統 ,採用

超標量 和超流水線結構;它們的指令數目只有幾十條,卻大大增強了

並行處理 能力。如:1987年SunMicrosystem公司推出的SPARC晶片就是一種超標量結構的RISC處理器。而SGI公司推出的MIPS處理器則採用超流水線結構,這些RISC處理器在構建並行精簡指令系統

多處理機 中起著核心的作用。RISC處理器是當今UNIX領域64位多處理機的主流晶片。

性能特點

性能特點一:由於指令集簡化後,流水線以及常用指令均可用硬體執行;

性能特點二:採用大量的

暫存器 ,使大部分指令操作都在暫存器之間進行,提高了處理速度;

性能特點三:採用

快取 —

主機 —外存三級

存儲結構 ,使取數與存數指令分開執行,使處理器可以完成儘可能多的工作,且不因從

存儲器 存取信息而放慢處理速度。

套用特點

由於RISC

處理器指令 簡單、採用硬布線控制邏輯、處理能力強、速度快,世界上絕大部分UNIX

工作站 和伺服器廠商均採用RISC晶片作CPU用。如原DEC的Alpha21364、IBM的PowerPCG4、HP的PA—8900、SGI的R12000A和SUNMicrosystem公司的UltraSPARC║。

運行特點

RISC晶片的工作頻率一般在400MHZ數量級。

時鐘頻率 低,功率消耗少,溫升也少,機器不易發生故障和老化,提高了系統的可靠性。單一

指令周期 容納多部並行操作。在RISC

微處理器 發展過程中。曾產生了超長

指令字 (VLIW)微處理器,它使用非常長的指令組合,把許多條指令連在一起,以能

並行執行 。VLIW處理器的基本模型是標量代碼的執行模型,使每個

機器周期 內有多個操作。有些RISC處理器中也採用少數VLIW指令來提高處理速度。

精簡指令集

精簡指令集 精簡指令集

精簡指令集 32位精簡指令集架構

32位精簡指令集架構 精簡指令集

精簡指令集 擴展指令集

擴展指令集 精簡指令集

精簡指令集