系統級以下是算法級,在這一層次上,行為描述的是系統的數據結構和算法。算法級在結構上描述了子系統是由哪些模組組成的。

基本介紹

- 中文名:算法級

- 外文名:algorithm level

- 拼音:suàn fǎ jí

- 屬性:系統級以下

- 作用:在結構上描述子系統的模組組成

- 套用學科:計算機

技術簡介,算法級建模方法,算法級抗攻擊措施,減小信號強度,增加隨機噪聲,數據隨機化掩蓋,算法級的低功耗設計,並行結構,流水線技術,匯流排編碼,

技術簡介

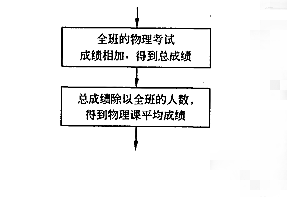

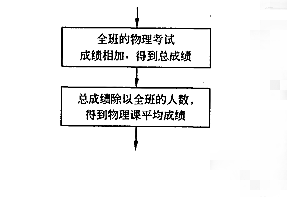

系統級以下是算法級。在這一層次上,行為描述的是系統的數據結構和算法。算法定義了為回響給定的輸入序列並產生所需的結果,該系統(主要是信息處理單元)應執行的運算和各種操作的順序和步驟,以及本系統內部如何與外部世界進行數據交換。算法可用公式或算法流圖形式來予以描述。例如,為了統計一個班同學的物理課考試的平均成績,可以分兩個“運算步”進行計算(如圖1所示)。

圖1 “運算步”進行計算

第一步是將全班同學的物理考試成績相加,得到全班同學的物理總成績;第二步是用全班的人數去除全班的物理總成績,得到全班物理考試的平均成績。

同一個算法可以用軟體程式完成,也可用硬體實現,採用硬體實現的最大優點是工作速度快。針對硬體實現的算法設計是一項具有挑戰性和創造性的工作,這要求設計者不僅有深厚的數學知識,還要有豐富的硬體實踐經驗。設計算法時,必須要考慮硬體實現的可行性、設備的成本、工作速度等多種因素。

算法級在結構上描述了子系統是由哪些模組組成的。例如,信息必理單元由數據處理器(簡稱處理器(processor))和控制器(controller)兩個模組組成,模組之間通過數據通道和控制通道相互連線。數據處理器模組對數據進行傳輸、算術運算、邏輯運算等各種加工和處理工作;控制器模組向數據處理器以及其他子系統發出控制信息,使整個系統按正確的順序有步驟地協調工作。算法級又稱子系統級,它規定了組成子系統的模組的功能,但不涉及模組的內部結構。

算法級建模方法

算法級建模抽象級別很高,往往不考慮硬體實現的具體細節,一般對特大型設計或有較複雜的算法時使用。建模時往往利用高級語言,如C語言及其他一些系統分析工具(如MATLAB),對設計從算法方面進行描述。一般來說,算法級設計只用於仿真,驗證系統功能,通常不支持綜合,在仿真通過後,再用RTL級進行設計。因此對於複雜的系統晶片設計項目,最傳統的辦法是在系統級採用VHDL,在軟體級採用C語言,在實現級採用Verilog。

Verilog HDL和VHDL都是用於數字電子系統設計的硬體描述語言,但兩種語言的標準不統一,適應的範圍也各有側重,Verilog適合算法級、RTL級、門級,而VHDL適合特大型的系統級設計,在系統級抽象方面的功能比Verilog強大。由於兩種硬體描述語言的標準不統一,導致軟、硬體設計工程師之間工作交流出現障礙,工作效率較低。雖然目前VHDL和Verilog的互操作性已經逐步走向標準化,但軟體與硬體的協調設計還是一個很具挑戰性的工作。另外,在設計細化階段,原始的C/C++描述必須手工轉換為VHDL或Verilog HDL。在這個轉換過程中會花費大量的時問,難免會產生一些錯誤,而且當使用C語言描述的模組轉換成HDL描述的模組之後,設計人員花費大量時間建立起來的C模型將再沒有什麼用處。

設計者迫切需要一種語言,要求能單一地完成全部設計,支持系統級調試和系統性能分析,支持從系統級到門級的無縫過渡,能夠用於描述各種不同的抽象級別(如系統級、暫存器傳輸級等);支持軟硬體混合建模,能夠勝任軟硬體的協同設計和驗證。System C就是目前這方面研究的最新、最好的成果,它擴展傳統的軟體語言C和c++,並使它們支持硬體描述,可以很好地實現軟硬體的協同設計,是系統級晶片設計語言的發展趨勢。

算法級抗攻擊措施

目前,算法級防範DPA攻擊的方法有幾類,其防禦思想都是相同的,主要是消除或減少算法運算元特徵;消除算法執行過程中的運算元和中間值與功耗之間的對應關係。算法級防範DPA攻擊的方法大致可以分為以下幾類:減小信號強度、增加隨機噪聲、數據隨機化掩蓋等。

目前,算法級防範DPA攻擊的方法有幾類,其防禦思想都是相同的,主要是消除或減少算法運算元特徵;消除算法執行過程中的運算元和中間值與功耗之間的對應關係。算法級防範DPA攻擊的方法大致可以分為以下幾類:減小信號強度、增加隨機噪聲、數據隨機化掩蓋等。

減小信號強度

減小信號強度的主要實現方法包括算法執行連續編碼、選取小能耗運算指令、均衡漢明重量等。算法執行連續編碼可以防止DPA判斷不同算法的起始點和結束點,不提供有價值的算法信息。選取小能耗運算的實現思想是用不易產生顯著能耗變化的指令取代一些原始指令,使得指令的能耗減小,使得不同指令的能耗趨於平衡。均衡漢明重量可使數據以原碼和反碼兩種形式表示,避免通過漢明重量與能耗的直接關係泄漏能量信息。

減小信號強度的主要實現方法包括算法執行連續編碼、選取小能耗運算指令、均衡漢明重量等。算法執行連續編碼可以防止DPA判斷不同算法的起始點和結束點,不提供有價值的算法信息。選取小能耗運算的實現思想是用不易產生顯著能耗變化的指令取代一些原始指令,使得指令的能耗減小,使得不同指令的能耗趨於平衡。均衡漢明重量可使數據以原碼和反碼兩種形式表示,避免通過漢明重量與能耗的直接關係泄漏能量信息。

增加隨機噪聲

增加隨機噪聲的方法是通過引入隨機噪聲使得有用的信號完全湮沒於無用的噪聲中,可以增加能量攻擊的難度。但是,這種方法不能從根本上解決問題,其因一是攻擊者可以通過有效的濾波消除干擾噪聲;二是DPA本身在做統計平均時就削弱了噪聲的影響。

增加隨機噪聲的方法是通過引入隨機噪聲使得有用的信號完全湮沒於無用的噪聲中,可以增加能量攻擊的難度。但是,這種方法不能從根本上解決問題,其因一是攻擊者可以通過有效的濾波消除干擾噪聲;二是DPA本身在做統計平均時就削弱了噪聲的影響。

數據隨機化掩蓋

數據隨機化掩蓋可分為明文隨機化掩蓋和指數隨機化掩蓋兩類。例如,分別通過數學運算的變換與反變換,使RSA算法中的運算元均為經過一定隨機化變形的替代數。僅通過能量差分運算得不到真實的差異點位置,這就為真實算法做了掩蓋,達到防禦DPA攻擊的目的。例如,RSA抗DPA的MIST算法就是一種可以防禦DPA攻擊的密碼算法。

MIST算法是在每次RSA模冪運算時都生成一個隨機的加法鏈來表示指數,從而隨機化內部的運算;另一個特點是需要用模約減算法來生成所需的隨機加法鏈。

MIST算法是在每次RSA模冪運算時都生成一個隨機的加法鏈來表示指數,從而隨機化內部的運算;另一個特點是需要用模約減算法來生成所需的隨機加法鏈。

算法級的低功耗設計

算法級的低功耗設計是指在確定電路實現方案時就考慮功耗問題,是從電路的體系結構和編碼等方面進行低功耗設計。在電路的體系結構方面下面主要討論並行結構和流水線技術。

並行結構

降低電路的工作電壓可以有效降低功耗,但同時會增加電路的延時,因此電路的設計人員在降低電路工作電壓的同時,必須採取措施提高電路的工作速度,才能真正達到降低功耗的目的。並行結構是將一條數據通路的工作分解到兩條通路上完成,這樣每條數據通路的工作頻率都為原來的一半,數據通路允許的延時增加了一倍,並且電路還可以採用較低的工作電壓。這種電路結構的並行化實質上是在保持電路吞吐量的基礎上通過增加電路的面積來達到降低功耗的目的。

流水線技術

在電路設計時採用流水線技術,就是採用插入暫存器的辦法來降低組合路徑的長度,達到提高電路速度的目的。具體做法是把規模較大,層次較多的邏輯電路分為幾個級,在每個級插入暫存器組暫存中間數據。

在流水線設計時,一般需要多個時鐘周期來獲取第一個計算結果,需要一個時鐘周期來獲取每級隨後的計算結果。因此,採用流水線技術後系統可以在較低的時鐘頻率下工作,從而降低了功耗。

流水線技術的不足之處是設計的複雜度比並行結構高,需要插入暫存器,增大面積而且需要額外的時鐘驅動,由此增加了時鐘負載電容,導致額外的功耗開銷。另外,並非所有算法均能有效地採用流水線技術,一些算法在流水線技術中可能會出現如下的情形。在理想的流水線操作中要求相鄰的兩條指令必須是獨立的,但在實際中,若下一條指令要用到上一條指令的值,由於流水線的原因不能及時更新數據,導致下一條指令取運算元錯誤,從而造成流水線操作的失敗。

匯流排編碼

在一個電路中或系統晶片中一般都有一條或多條匯流排,匯流排的一個基本特點是走線較長、負載較大,因此匯流排通常都具有較大的電容,並且這個電容的值幾乎不可能改變,降低匯流排上的翻轉頻率是節省匯流排功耗的唯一辦法。在完成同樣功能的前提下要降低匯流排上的有效翻轉頻率只有改變匯流排上傳輸數據的編碼。

因此,通過編碼可以減少匯流排的動態翻轉次數,並達到降低匯流排功耗的目的。數據匯流排的數據隨機性較大,地址匯流排的地址向量連續性較大。數據匯流排和地址匯流排這兩種匯流排傳送的數值各有特點,所以針對不同類型匯流排的編碼的算法也不一樣。