公式

輸入輸出的邏輯關係為

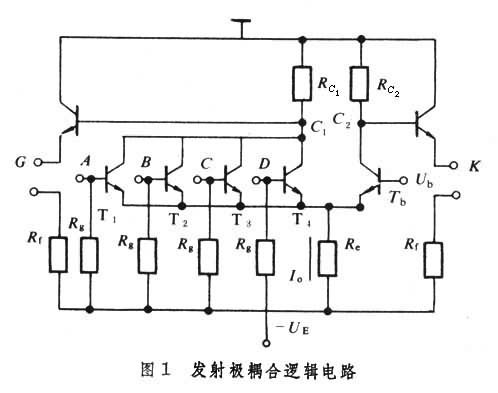

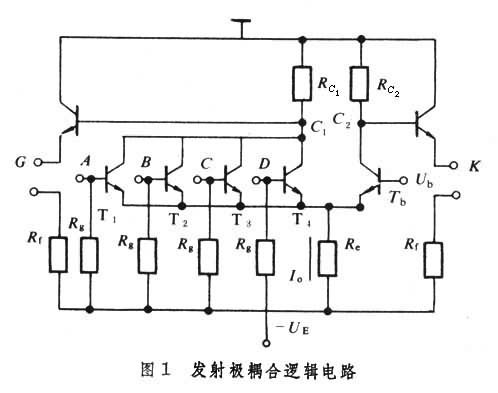

由輸入電晶體T1、T2、T3、T4和定偏電晶體Tb構成差動式結構的電流開關,其間的耦合是通過發射極電阻Re實現,因名發射極耦合邏輯電路。Tb的基極接有固定偏壓Ub,當有m 發射極耦合邏輯電路

個輸入管的基極加入信號Ui時,流過C1、C2兩點的電流滿足下式

式中

αO為輸入和定偏管共基直流放大係數。 發射極耦合邏輯電路

發射極耦合邏輯電路

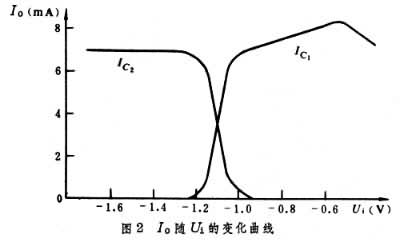

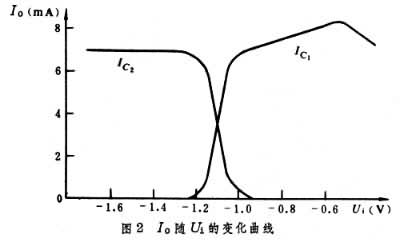

發射極耦合邏輯電路隨著Ui的變化,IO在差分對中切變。當輸入信號滿

時,電路具有整形性質,

C1、

C2兩點出現用電流電平或電壓電平辨別的四個狀 發射極耦合邏輯電路

發射極耦合邏輯電路

發射極耦合邏輯電路態,因而又稱電流開關。它靠Ui對電流的引導完成電流開關作用。

ECL電路的特點

1958年,制出第一塊電流開關,並成功地使用了射極跟隨器作電平移動,解決了信號電平的級聯問題,改善了ECL電路的基本單元電路。 發射極耦合邏輯電路

發射極耦合邏輯電路

發射極耦合邏輯電路為了保持電路的非飽和性質,ECL電路的邏輯幅度的典型值為0.8伏,高電平的典型值為-0.8伏。低電平的典型值為-1.6伏,定偏電晶體基極參考電平為-1.2伏。由於發射極耦合電阻Re的負反饋作用,電路工作時電流是在差分對中切變,不產生大的擾動。同時,由於射極跟隨器的隔離作用而能保證電路在較小的邏輯幅度下也能穩定可靠地工作。

①開關速度快(1納秒左右)。比通常的電晶體-電晶體邏輯電路開關速度快幾倍。

②可以很方便地組成、擴充電路的邏輯功能,節省元件數。缺點是電路功耗大、電平閾值電壓隨溫度而漂移等 。

ECL電路主要用於構成超高速積體電路,如高速、大型、巨型計算機等。

電路中,電晶體工作於非飽和區,Tb在共基極組態下工作。電路差動式結構的加速作用,使共發射極的輸入管實際工作在準共基極狀態下。小的邏輯幅度等條件保證了電路的高速度。電流開關在60年代即已用於計算機,使計算機的性能大大提高。

ECL電路的實用

ECL電路主要用於構成超高速積體電路,如高速、大型、巨型計算機等。電路中,電晶體工作於非飽和區,Tb在共基極組態下工作。電路差動式結構的加速作用,使共發射極的輸入管實際工作在準共基極狀態下。小的邏輯幅度等條件保證了電路的高速度。電流開關在60年代即已用於計算機,使計算機的性能大大提高。

發射極耦合邏輯是建立在一個多輸入差分放大器來放大並結合數位訊號,並發射追隨者調節直流電壓等級為基礎。因此,電晶體的柵極在沒有進入過飽和度,也沒有得到過完全關閉。電晶體留在他們的積極經營區域完全在任何時候。作為一個結果,沒有一個電晶體的電荷存儲時間抗衡,並能更迅速地改變狀態。因此,這種邏輯門的主要優點是非常高的速度。

上圖中所示是來自摩托羅拉的1000/10 MECL裝置系列,這種特殊的電路是一個4輸入或/或非門。該電路標準電壓為是-5.2伏(VEE)和地(VCC的)。未使用的輸入連線至V EE。在右側偏置電路,由一個電晶體和二極體和電阻器及其相關的組成,可以處理任何一個單一的IC封裝的門數。典型IC包括雙4輸入,三路3輸入,四路2輸入門。在每一種情況下,蓋茨自己有多少差別只在他們輸入電晶體。一個單一的偏置電路為所有大門。在操作中,一個邏輯ouput改變狀態僅0.85伏特從-1.60伏特低,電壓高的-0.75。內部偏置電路提供固定的-1.175伏電壓的差分放大器的偏置在電晶體。如果所有的輸入電壓是在-1.6(或綁至V EE),輸入電晶體將全部關閉,只有內部差分電晶體將傳導電流。這降低了電晶體的基極電壓或輸出,其輸出電壓降低到-1.60伏特。與此同時,沒有輸入電晶體輸出電晶體的NOR影響的基礎,所以它的輸出電壓上升到-0.75。這簡直是發射極基電壓V是本身的電晶體。(所有電晶體都在積體電路,並設計有一個V是0.75伏特。)當任何輸入電壓上升到-0.75,即電晶體的發射極電流虹吸管遠離內部差分電晶體,導致輸出開關狀態。

在此類型的電路中,電壓這一變化很小,並且為V取決於上的BE時,涉及他們的電晶體。更重要的電路的工作是通過各種電晶體的電流流動量的,而不是涉及的精確電壓。因此,發射極耦合邏輯也被稱為電流模式邏輯(CML)。這是不是唯一的技術,實現以任何方式慢性粒細胞白血病,但它確實說明,一般到秋天。在任何情況下,這導致我們對這一門式的主要缺點:它描繪了一個從電源電流很大,因此往往浪費了大量的熱量。為了減少這種問題,例如頻率計數器使用某些設備在十年的ECL電路輸入端的櫃檯,由TTL或高速CMOS計數器其次為後來的數字位置。這使得快速,昂貴的IC在那裡是絕對必要的,並允許我們使用更便宜的地點積體電路其中信號不會在那么高的頻率。

發射極耦合邏輯電路

發射極耦合邏輯電路 發射極耦合邏輯電路

發射極耦合邏輯電路 發射極耦合邏輯電路

發射極耦合邏輯電路